在上一章节中我们已经安装好了MATLAB和VeriStand软件,并且配置了MATLAB和VeriStand编译器的联动,这样就完成了VeriStand硬件在环仿真测试中软件环境的搭建。

本文承接上一章中的内容,在完成了软件环境的配置后,我们就可以开始搭建MATLAB和VeriStand硬件在环仿真系统啦,Simulink模型如何编译到VeriStand的动态链接库?让我们一起看看在MATLAB中需要做哪些相关设置吧!

本文教程:

Veristand硬件在环仿真测试第二章

硬件环境:

NI PXIe-1075机箱

NI PXIe-8861控制器

NI PXIe-6220多功能数据采集模块

上位机一台(安装有LabVIEW相关软件)

软件环境:

Windows 10

LabVIEW 2020 SP1

VeriStand 2020 R4

MATLAB R2020a

第一步:

修改路径。

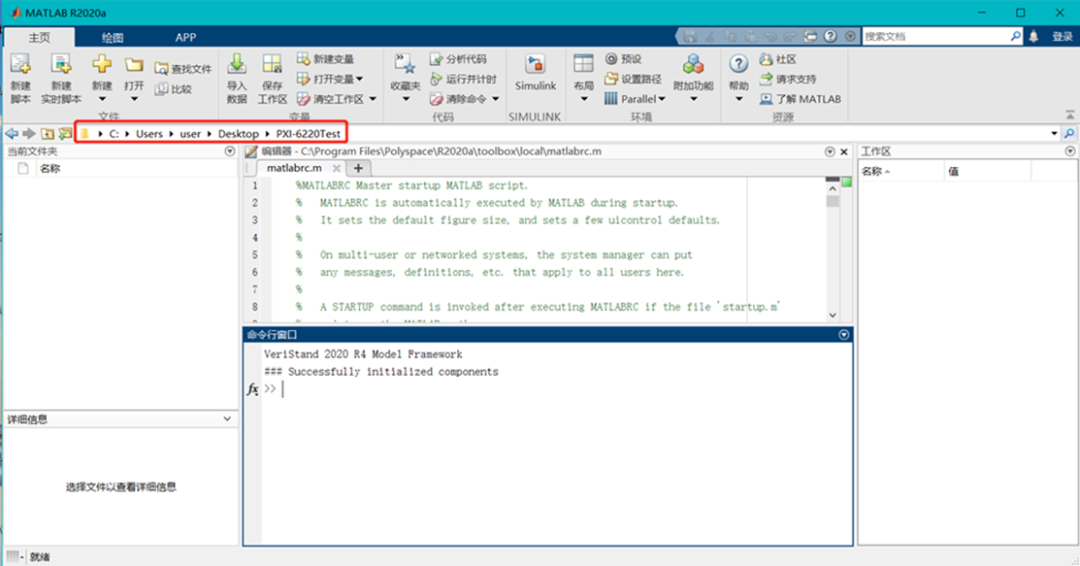

1、打开MATLAB等待一会儿就可以看到命令行窗口弹出“VeriStand 2020 R4 Model Framework”,说明环境变量和编译器已经配置成功了,接下来建立一个空的文件夹(注意不要有中文、空格等字符)将工作目录切换到已建立好的文件夹中。

第二步:

构建模型。

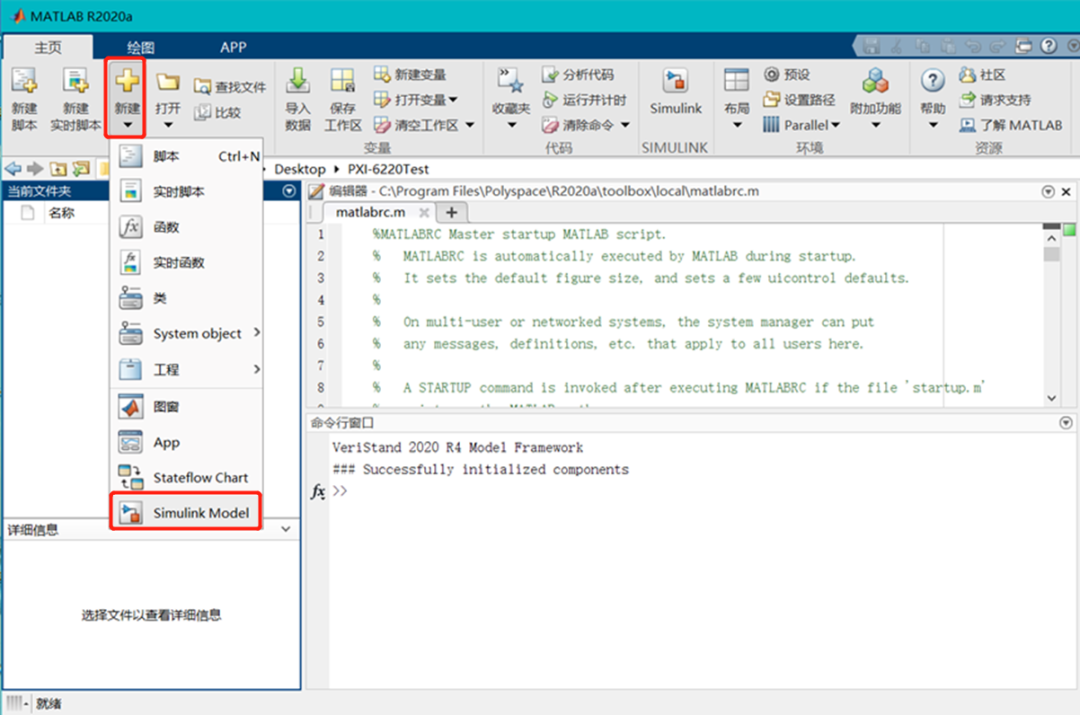

1、点击新建,然后选择Simulink Model,我们将在Simulink中构建我们的仿真模型。

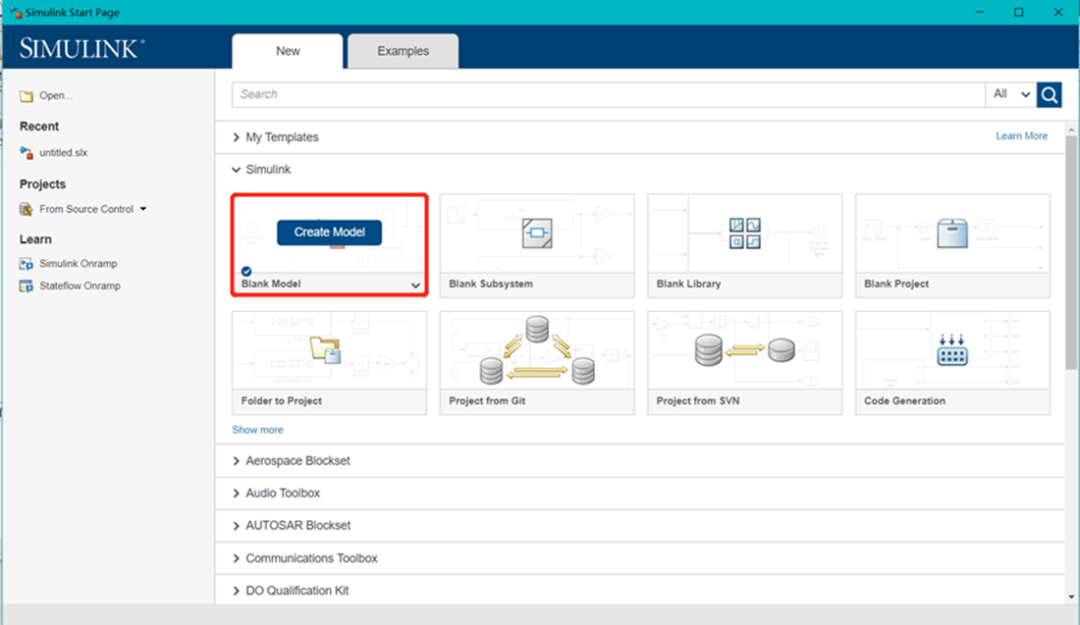

2、点击Blank Model并选择Create Model创建空白的Simulink模型。

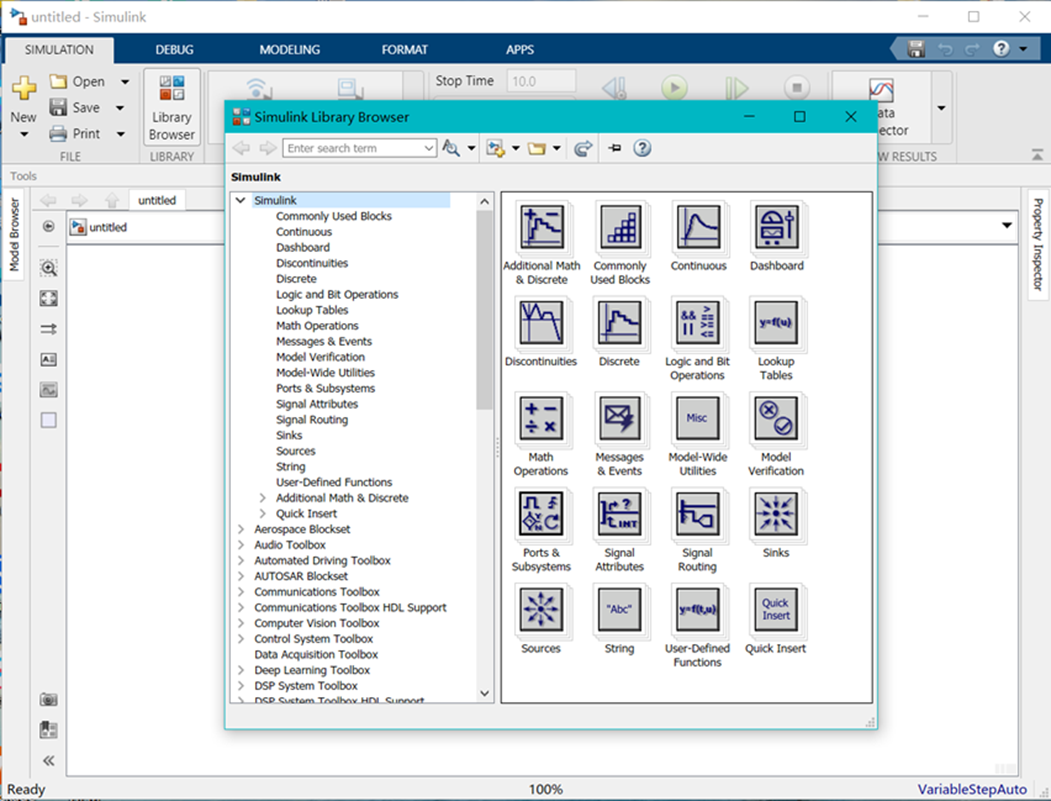

3、建立空白的模型后,点击Library Browser会弹出这个Simulink Library Browser界面。在这里选择要使用的功能模块,搭建自己想要实现的功能模型,这里的编程和LabVIEW图形化的编程方法非常相似,就不过多阐述了。

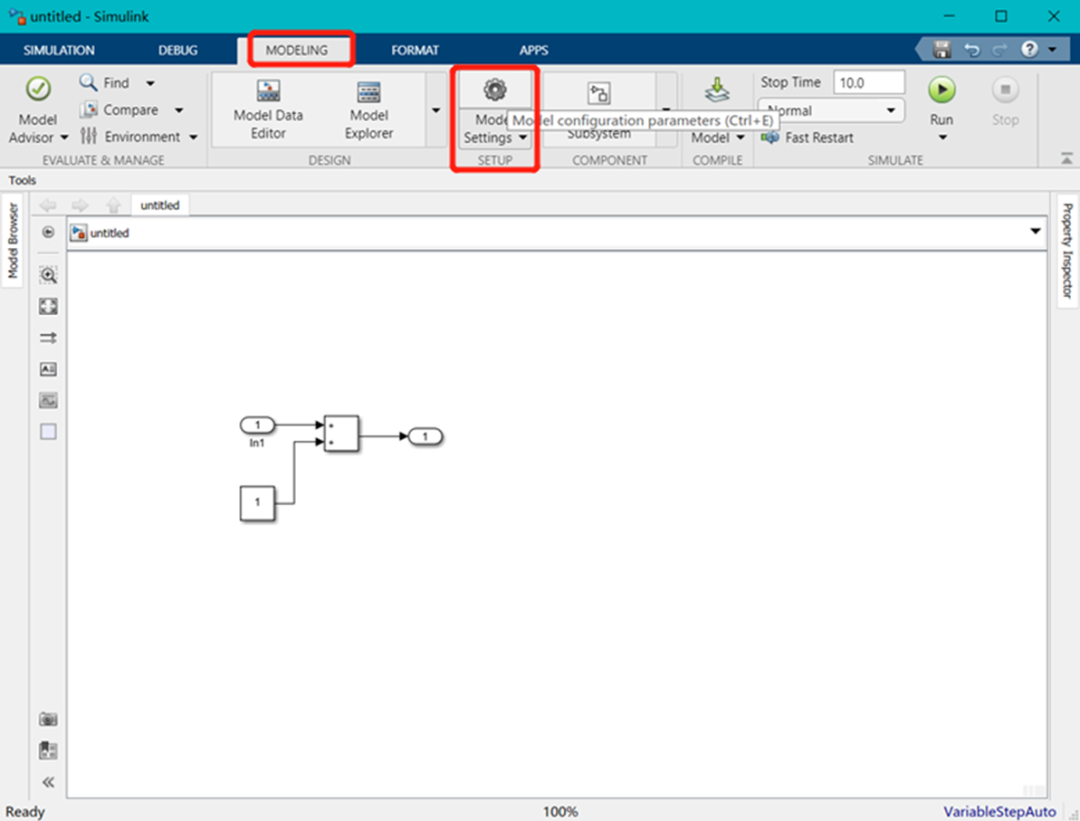

4、我们搭建了一个最简单的模型——输入值加上一个常量“1”的加法模型(注意模型中需要和VeriStand对接的地方都要有输入/输出节点),接下来,我们要开始进行一系列的设置,首先让我们打开设置界面:在MODELING下点击设置或者快捷键Ctrl+E进入设置界面。

第三步:

设置模型。

1、基础设置:

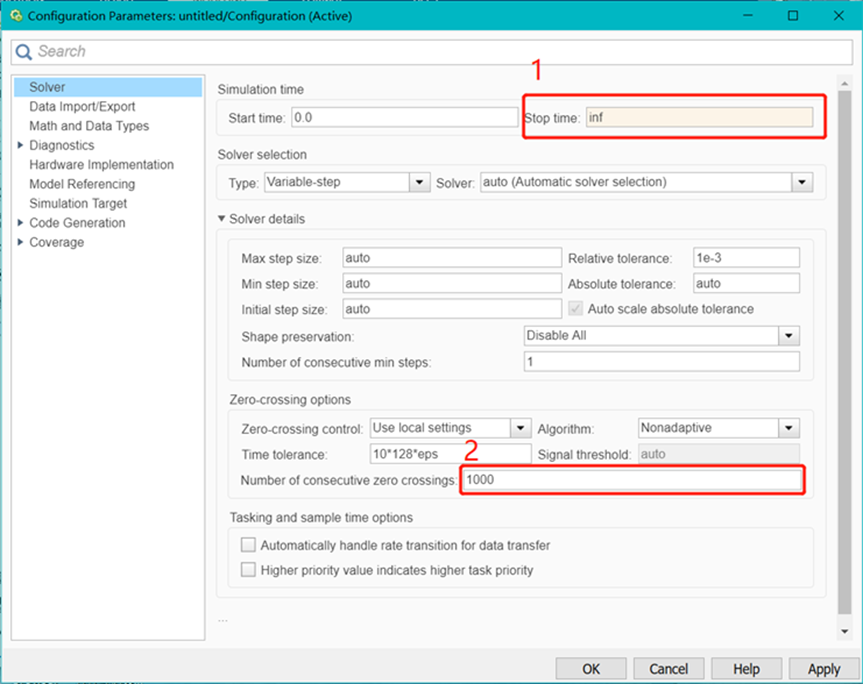

①.设置运行时间,一般设置为小写inf(无穷),让模型可以一直运行,如果用大写INF会报错。

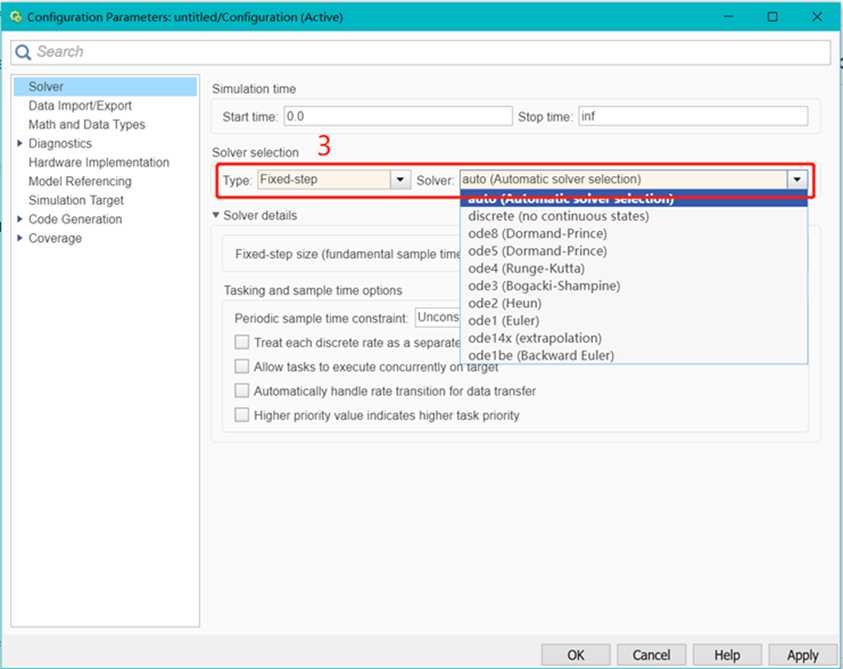

②.设置步长类型,根据需要设置可变步长或者固定步长(Windows下可以选择固定或者可变,RT下只能设置固定步长)步长选择完成后可以设置求解器;固定步长时推荐用ode4,ode4求解器使用四阶龙格库塔算法,它的计算量和求解精度达到了一个比较好的均衡。可变步长时建议用自动求解器,由MATLAB自己决定使用哪种求解器。

2、编译设置:

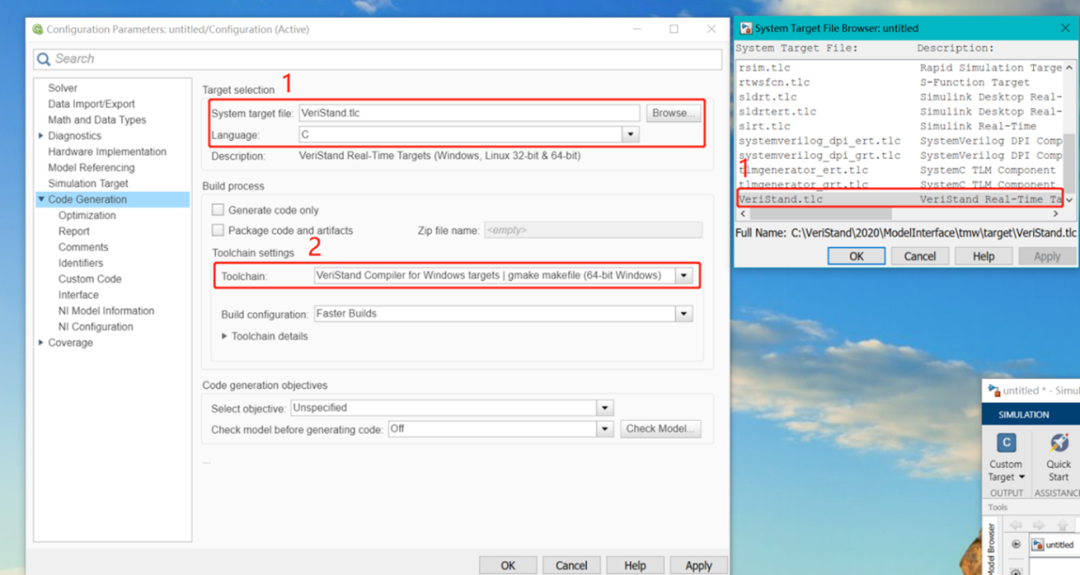

①.在Target selection下选择系统目标文件为“VeriStand.tlc”,语言为C;

②.在Toolchain下选择,根据模型运行在不同下位机操作系统来选择编译工具链,PXI选64bit Linux;ARM cRIO选32bit Linux;本机测试选64bit Windows。前缀都是Veristand Compiler for…

第四步:

编译模型。

1、全部设置完成后在界面点击保存按钮或者快捷键Ctrl+S保存模型。

![]()

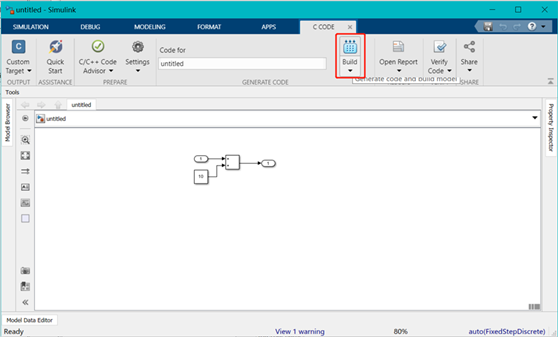

2、保存设置后按Ctrl+B或者按下界面上的Build进行编译,以Windows为目标会生成.DLL文件,以Linux为目标会生成.so文件。

至此Simulink模型编译为可以在VeriStand下调用的的动态链接库,今天这章的内容也到此结束,下一章节是VeriStand硬件在环仿真配置的重点——VeriStand中的相关配置,敬请期待!

对硬件在环仿真测试感兴趣的工程师们,欢迎留言和点赞。请大家持续关注华穗科技微信公众号,也可以私信小编各位的技术困惑和技术需求,以获取参加免费线下培训和技术交流的机会哦!

注:

1. 一定要根据已有的硬件来选择不同的编译器

2. 步长设置要匹配板卡的采样率/刷新率

3. Simulink模型中要和VeriStand对接的地方都必须要有输入/输出节点

4. Simulink模型中要和VeriStand对接的输入/输出节点放在模型顶层才能生效

因本次使用的软件版本为VeriStand 2020R4和MATLAB R2020a,没有验证其它版本的兼容性,感兴趣的可以和我们联系,一起交流探讨~

最后

以上就是兴奋草莓最近收集整理的关于教程 | VeriStand硬件在环仿真测试第二章的全部内容,更多相关教程内容请搜索靠谱客的其他文章。

发表评论 取消回复