乐鑫科技校招芯片岗真题

这题代码有问题,请不要照抄

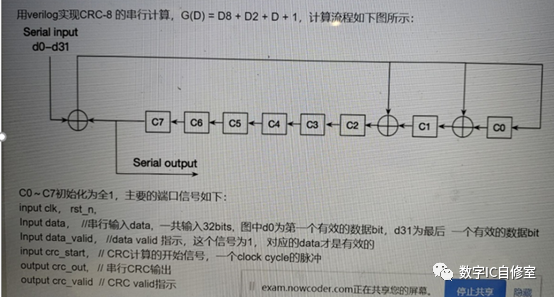

用verilog实现CRC-8的串行计算,G(D)=D8+D2+D+1,计算流程如下

解析:这个题目涉及到状态机(控制通路)和移位计算(数据通路)的混合,稍微有点复杂。基本上围绕着控制通路和数据通路切分的思想来设计会比较清晰。

CRC串行计算的原理就是通过线性反馈移位寄存器进行输入数据移位,同时对应的生成多项式相应项数与对应数据位做异或反馈到输入端,当所有的数据位均移入时,移位寄存器的值就是CRC结果。

控制通路方面,一个状态机控制,需要以下几个状态:

IDLE:等待CRC开始信号

WAIT:等待有效位的串行输入进行移位,如果下一次输入为无效数据,停留此状态,否则跳转到LF

LF:做一次移位计算,如果下一次输入仍为有效数据,则停留此状态,否则回到WAIT状态。每次进入此状态,移位计数器加1,到达32时进入OUTPUT状态

OUT: 完成32bit计算,开始输出移位数据,完成移位输出则回到IDLE

数据通路方面,就是8bit线性反馈移位寄存器,只有在CAL状态下可以进行移位,移位寄存器使能为1。此外该线性反馈移位寄存器的生成多项式对应bit在移位前需要做相应的异或运算,根据图示逻辑来写代码即可。当32bit的输入完全移入移位寄存器时,CRC计算完成,开始输出结果,只有在OUTPUT状态下数据的输出crc_valid才可以为高。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/04/29 19:20:53

// Design Name: 离离离谱

// Module Name: timu1

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module timu1(

clk,

rst_n,

data,

data_valid,

crc_start,

crc_out,

crc_valid

);

input clk;

input rst_n;

input data;

input data_valid;

input crc_start;

output crc_out;

output crc_valid;

reg [7:0] lf;

reg [4:0] counter,crc_counter;//counter 计数32个data,crc_counter计数输出数据

reg [1:0] state , next_state;//当前状态和次态

reg [31:0] temp;

parameter IDLE = 2'b00 , WAIT = 2'b01, LF = 2'b10,OUT = 2'b11;

reg out;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

state <= IDLE;

end

else begin

state <= next_state;

end

end

always@(*)begin

if(!rst_n)begin

next_state <= IDLE;

end

else begin

case(state)

IDLE:begin

if(crc_start)begin//当crc_start信号拉高时,说明开始传输数据

next_state <= WAIT;

end

else begin

next_state <= IDLE;

end

end

WAIT:begin

if(data_valid)begin//当数据有效时,进行移位操作

next_state <= LF;

end

else begin

next_state <= WAIT;

end

end

LF:begin

if(counter == 5'd31)begin//当记满32个数据时,跳转到out状态

next_state <= OUT;

end

else if(data_valid)begin//当数据还是有效时,继续LF状态

next_state <= LF;

end

else begin

next_state <= WAIT;

end

end

OUT:begin

if(crc_counter == 5'd31)begin//当输出满32个数据时,回到空闲状态

next_state <= IDLE;

end

else begin

next_state <= OUT;

end

end

endcase

end

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

counter <= 0;

lf <= 8'b1111_1111;

temp <= 0;

crc_counter <= 0;

end

else begin

case(state)

IDLE:begin

lf <= 8'b1111_1111;

crc_counter <= 0;

end

WAIT:begin

if(data_valid)begin

counter <= counter + 1;

lf <= {lf[6:2],data^lf[7]^lf[1],data^lf[7]^lf[0],data^lf[7]};

temp[counter] <= lf[7];

end

else begin

counter <= counter;

lf <= lf;

end

end

LF:begin

if(counter == 5'd31)begin

counter <= 0;

end

else if(data_valid)begin

counter <= counter + 1;

lf <= {lf[6:2],data^lf[7]^lf[1],data^lf[7]^lf[0],data^lf[7]};

temp[counter] <= lf[7];

end

else begin

counter <= counter;

end

end

OUT:begin

if(crc_counter == 5'd31)begin

crc_counter <= 0;

end

else begin

crc_counter <= crc_counter + 1;

temp <= {1'b0,temp[31:1]};

end

end

endcase

end

end

assign crc_valid = (state == OUT)?1'b1:1'b0;

assign crc_out = (state == OUT)?temp[0]:1'b0;

endmodule

最后

以上就是鲜艳纸鹤最近收集整理的关于用verilog实现CRC-8的串行计算乐鑫科技校招芯片岗真题的全部内容,更多相关用verilog实现CRC-8内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复