Verilog HDL 之 步进电机驱动控制

步进电机的用途还是非常广泛的,目前打印机,绘图仪,机器人等等设备都以步进电机为动力核心。那么,下面我们就了解下什么是步进电机,它是怎么控制的。

一、步进电机相关知识简介

1、步进电机概述

步进电机是一种能够将电脉冲信号转换成角位移或线位移的机电元件,它实际上是一种单相或多相同步电动机。单相步进电动机有单路电脉冲驱动,输出功率一般很小,其用途为微小功率驱动。多相步进电动机有多相方波脉冲驱动,用途很广。使用多相步进电动机时,单路电脉冲信号可先通过脉冲分配器转换为多相脉冲信号,在经功率放大后分别送入步进电动机各相绕组。每输入一个脉冲到脉冲分配器,电动机各相的通电状态就发生变化,转子会转过一定的角度(称为步距角)。正常情况下,步进电机转过的总角度和输入的脉冲数成正比;连续输入一定频率的脉冲时,电动机的转速与输入脉冲的频率保持严格的对应关系,不受电压波动和负载变化的影响。由于步进电动机能直接接收数字量的输入,所以特别适合于微机控制。

2、步进电机的种类

目前常用的步进电机有三类:

(1)反应式步进电动机(VR):它的结构简单,生产成本低,步距角可以做的相当小,但动态性能相对较差。

(2)永磁式步进电动机(PM):它的出力大,动态性能好;但步距角一般比较大。

(3)混合步进电动机(HB):它综合了反应式和永磁式两者的优点,步距角小,出力大,动态性能好,是性能较好的一类步进电动机。

如果还想做更深入的了解,自行查找相关资料。

3、步进电机控制的实现

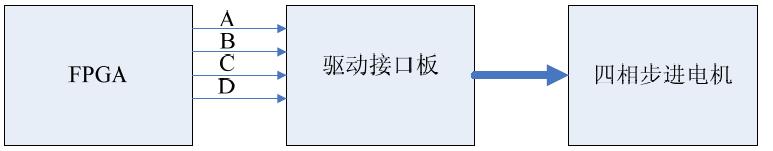

我们实验中所使用的步进电机为四相步进电机。转子小齿数为64。系统中采用四路I/O进行并行控制,FPGA直接发出多相脉冲信号,在通过功率放大后,进入步进电机的各相绕组。这样就不再需要脉冲分配器。脉冲分配器的功能可以由纯软件的方法实现。

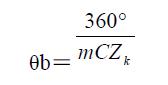

四相步距电机的控制方法有四相单四拍,四相单、双八拍和四相双四拍三种控制方式。步距角的计算公式为:

其中:m为相数,控制方法是四相单四拍和四相双四拍时C为1,控制方法是四相单、双八拍时C为2,Zk为转子小齿数。本系统中采用的是四相单、双八拍控制方法,所以步距角为360°/512。但步进电机经过一个1/8的减速器引出,实际的步距角应为360°/512/8。

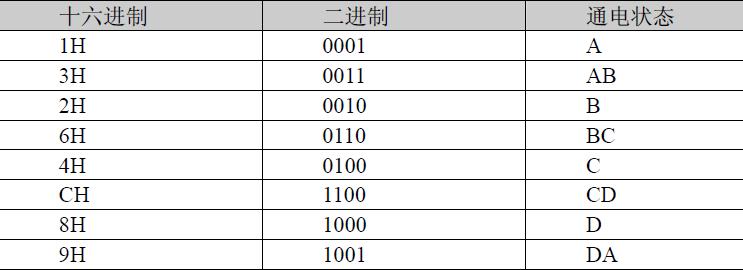

试验中使用EXI/O的高四位控制四相步进电机的四个相。按照四相单、双八拍控制方法,电机正转时的控制顺序为A→AB→B→BC→C→CD→D→DA。EXI/O的高四位的值参见表1.1。

表1.1 电机正转时,FPGA四位IO口的值

反转时,只要将控制信号按相反的顺序给出即可。

步进电机的频率不能太快,也不能太慢。在200Hz附近最好。频率太快是转动不起来的。

注:为什么步进电机高于一定速度就无法启动:

步进电机有一个技术参数:空载启动频率,即步进电机在空载情况下能够正常启动的脉冲频率,如果脉冲频率高于该值,电机不能正常启动,可能发生丢步或堵转。在有负载的情况下,启动频率应更低。如果要使电机达到高速转动,脉冲频率应该有加速过程,即启动频率较低,然后按一定加速度升到所希望的高频(电机转速从低速升到高速)。

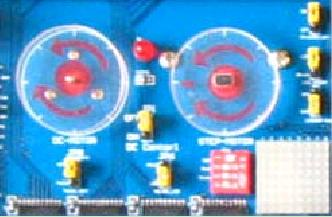

二、实验平台

Quartus II 7.2 集成开发环境、SOPC-MBoard板、ByteBlaster II 下载电缆

三、实验实现

详细实现步骤请参考 【连载】 FPGA Verilog HDL 系列实例--------8-3编码器

1、在设计文件中输入Verilog代码。

1 //-------------------------------------------------------------------------------------------------- 2 // Title : StepMotorPorts 3 // Author : wangliang 4 // Generated : 2011.08.16 5 //------------------------------------------------------------------------------------------------- 6 7 module StepMotorPorts (StepDrive, clk, Dir, StepEnable, rst); 8 9 input clk; 10 input Dir; 11 input StepEnable; 12 input rst; 13 14 output[3:0] StepDrive; 15 16 reg[3:0] StepDrive; 17 reg[2:0] state; 18 reg[31:0] StepCounter = 32'b0; 19 parameter[31:0] StepLockOut = 32'd200000; //250HZ 20 reg InternalStepEnable; 21 22 always @(posedge clk or negedge rst) 23 begin 24 if ( !rst) 25 begin 26 StepDrive <= 4'b0; 27 state <= 3'b0; 28 StepCounter <= 32'b0; 29 end 30 31 else 32 begin 33 if (StepEnable == 1'b1) InternalStepEnable <= 1'b1 ; 34 35 StepCounter <= StepCounter + 31'b1 ; 36 if (StepCounter >= StepLockOut) 37 begin 38 StepCounter <= 32'b0 ; 39 40 if (InternalStepEnable == 1'b1) 41 begin 42 InternalStepEnable <= StepEnable ; 43 if (Dir == 1'b1) state <= state + 3'b001 ; 44 else if (Dir == 1'b0) state <= state - 3'b001 ; 45 case (state) 46 3'b000 : StepDrive <= 4'b0001 ; 47 3'b001 : StepDrive <= 4'b0011 ; 48 3'b010 : StepDrive <= 4'b0010 ; 49 3'b011 : StepDrive <= 4'b0110 ; 50 3'b100 : StepDrive <= 4'b0100 ; 51 3'b101 : StepDrive <= 4'b1100 ; 52 3'b110 : StepDrive <= 4'b1000 ; 53 3'b111 : StepDrive <= 4'b1001 ; 54 endcase 55 end 56 end 57 end 58 end 59 endmodule

注:

(1)第19行,此处的数值为200000,因为实验中所使用的晶振时钟频率是50MHz,这样我们为步进电机提供了250Hz的频率,使之能正常工作。

(2)第43、44行是选择正转还是反转。

(3)第45行~第54行:就是根据表1.1而来的,配置步进电机的IO口值。

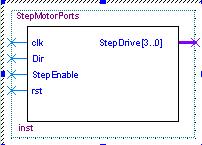

2、由设计文件生成的.bsf文件,其外接接口如图1.2所示。

3、引脚分配

clk接时钟;Dir接按键,控制正转还是反转;StepEnable接按键,表示开关;rst接复位信号;StepDrive接步进电机的4个引脚。

4、实验结果

烧写到FPGA上以后,通过拨动开关就可以使步进电机正转反转了。

最后

以上就是靓丽小伙最近收集整理的关于FPGA Verilog HDL 系列实例--------步进电机驱动控制的全部内容,更多相关FPGA内容请搜索靠谱客的其他文章。

发表评论 取消回复