ISE14.7,联合Modelsim SE仿真

模块源代码

`timescale 1ns / 1ps

module half_clk_test(

reset,

clk_in,

clk_out

);

input clk_in,reset;

output clk_out;

reg clk_out;

always @(posedge clk_in)

begin

if(!reset) clk_out = 0;

else clk_out = ~clk_out;

end

endmodule

测试模块代码

`timescale 1ns / 100ps

`define clk_cycle 50

module vtf_half_clk_test;

// Inputs

reg reset;

reg clk_in;

// Outputs

wire clk_out;

// Instantiate the Unit Under Test (UUT)

half_clk_test uut (

.reset(reset),

.clk_in(clk_in),

.clk_out(clk_out)

);

//产生测试时钟

always #`clk_cycle clk_in = ~clk_in;

//注意这边引用宏定义时的写法

initial begin

// Initialize Inputs

reset = 1;

clk_in = 0;

#10 reset = 0;

#110 reset = 1;

// Wait 100 ns for global reset to finish

#100000 $stop;

// Add stimulus here

end

endmodule

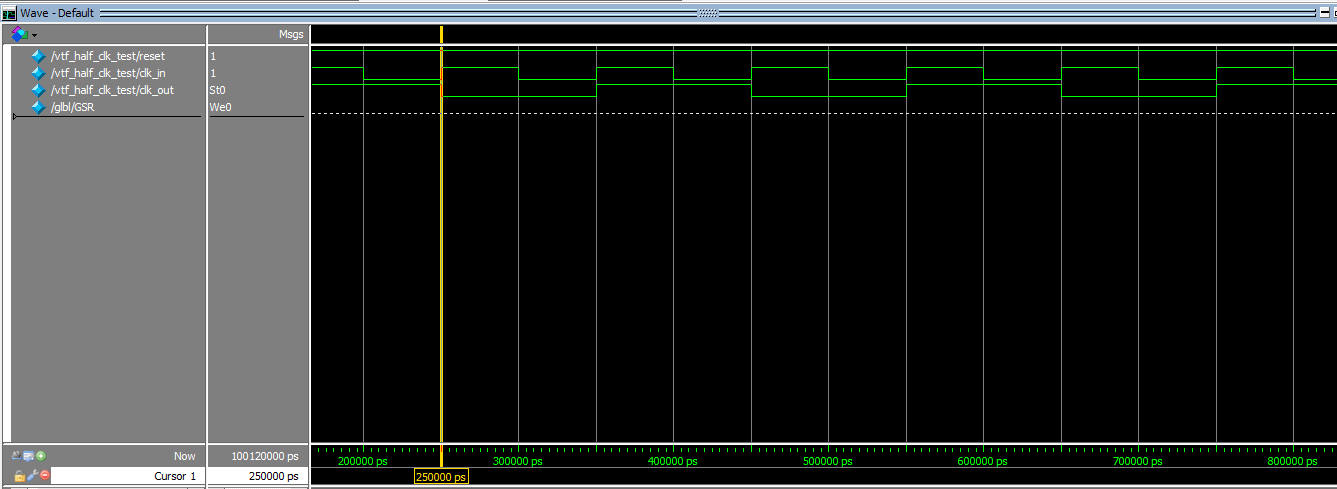

仿真波形

最后

以上就是忧伤镜子最近收集整理的关于练习二 二分频的全部内容,更多相关练习二内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复