数字前端设计的一些问题——门控时钟

初次了解到门控时钟的概念是在做一个算法IP的时候,为了解决Block功耗较大,建议改版加入门控时钟clock gating的设计;

后续的改版也没有由我来完成,所以实际效果不能给出。

不过,这里会留有一份文件,仅供参考。

这里直接开始,看看怎么设计。

雏形

门控时钟,顾名思义,就是加一个门电路,来使能时钟信号。

当某个模块不使用的时候,将其drive clock进行复位,以减小该模块的功耗。

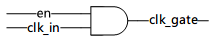

根据理解,最先想到的是这样的操作:

assign clk_gate = en & clk_in;

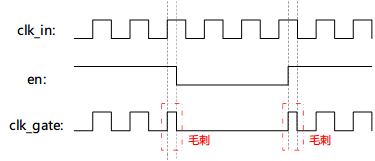

乍一看,像模像样;仔细考虑一下,如果EN没有跟clk_in对齐,就会出现gate_clk周期及相位上的波动,如下图所示:

上图的毛刺现象,可能会对设计带来一定的影响。

改进

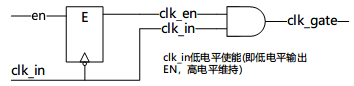

可以在en端增加一个以clk_in为触发的寄存器,生成clk_en信号,再将clk_in与clk_en连接到与门;

可以理解为latch为低有效,也就是说latch的en端口(clk_in)为低时,latch的q端(clk_en)是根据en变化的;

latch的en端口(clk_in)为高时,latch的q端就会被锁住;

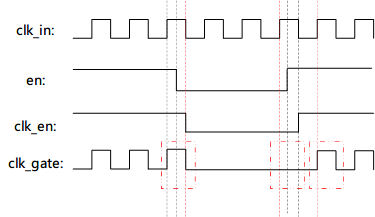

工作波形如下图所示:

可以对比红色cursor处进行观察。

RTL code

module clk_gating(

input wire clk_in,

input wire en,

output wire clk_gate

);

reg clk_en;

always @(*) begin // latch

if ( ~clk_in ) begin

clk_en = en;

end else begin

clk_en = clk_en;

else

end

assign clk_gate = clk_en & clk_in;

endmodule

参考

关于latch的门控时钟。

更新

2020-09-17:更新工作波形图;

2022-11-01:更新RTL code;

最后

以上就是耍酷草丛最近收集整理的关于数字前端设计的一些问题——门控时钟数字前端设计的一些问题——门控时钟的全部内容,更多相关数字前端设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复