之前有介绍过《FPGA/IC内卷新“标准”-最新刷题网站公布》。

题目链接

❝https://www.nowcoder.com/exam/oj?tab=Verilog%E7%AF%87&topicId=302&fromPut=pc_zh_verilog4

阅读原文可到达。

练题链接 https://www.nowcoder.com/exam/oj?tab=Verilog%E7%AF%87&topicId=302&fromPut=pc_zh_verilog4

https://www.nowcoder.com/exam/oj?tab=Verilog%E7%AF%87&topicId=302&fromPut=pc_zh_verilog4

今天就简单说一下一些知识点及题目的解析。

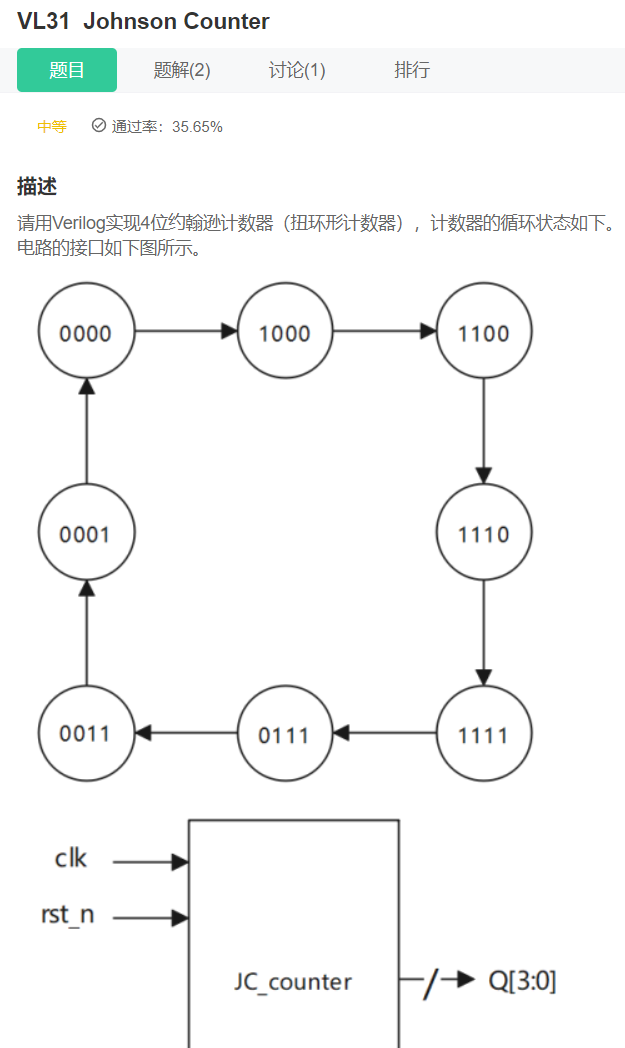

VL31 Johnson Counter

Johnson Counter本质是个同步计数器,我在《Verilog时序逻辑硬件建模设计(三)同步计数器》中有过详细介绍和设计。

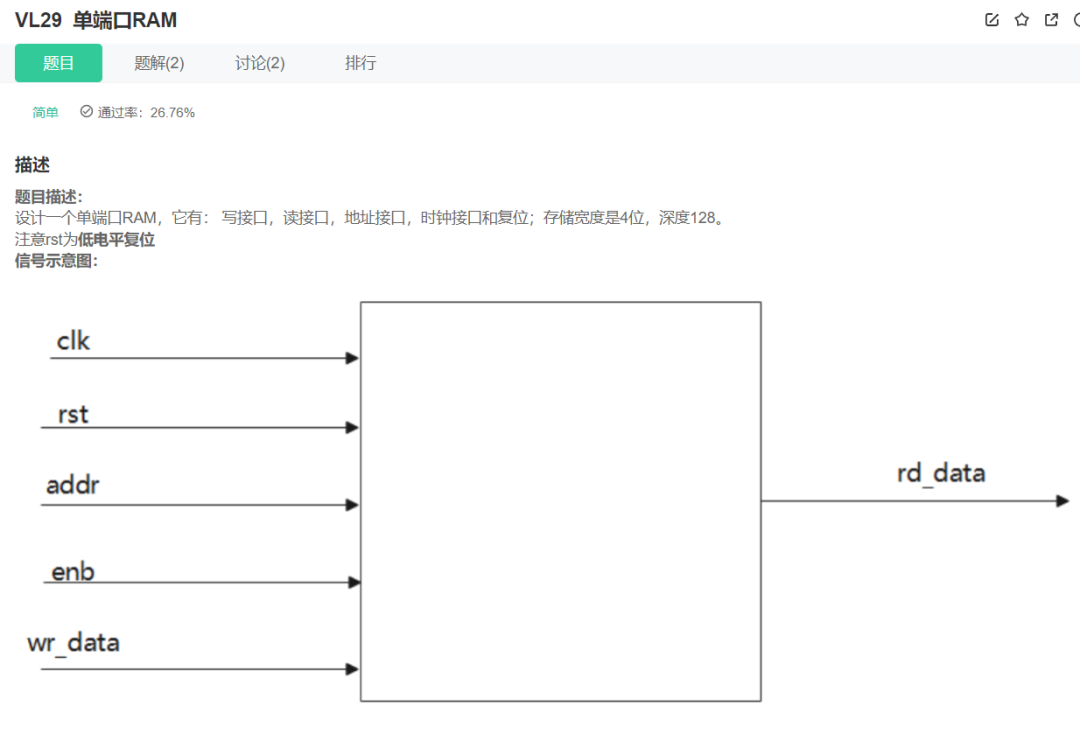

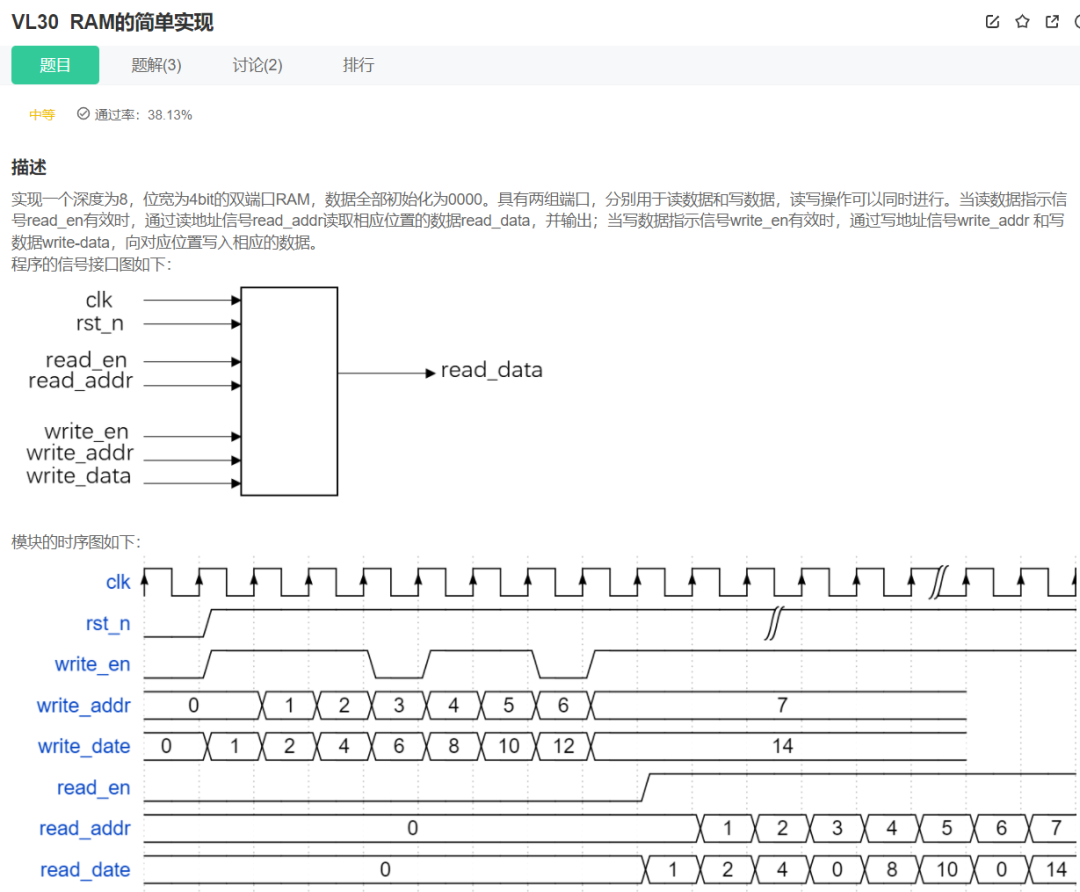

VL29 单端口RAM & VL30 RAM的简单实现

存储器可以是ROM、RAM、单端口或双端口类型,这部分在《Verilog时序逻辑硬件建模设计(五)异步计数器&总结》中有过简单介绍

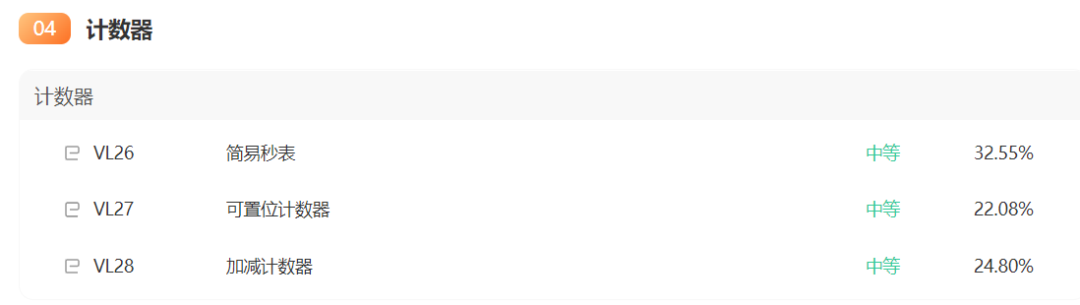

VL26 简易秒表 & VL27 可置位计数器 & VL28 加减计数器

这部分也是考察的同步计数器,属于时序逻辑设计,这部分在《Verilog时序逻辑硬件建模设计(三)同步计数器》和《Verilog时序逻辑硬件建模设计(四)移位寄存器》中有过介绍和实例讲解。

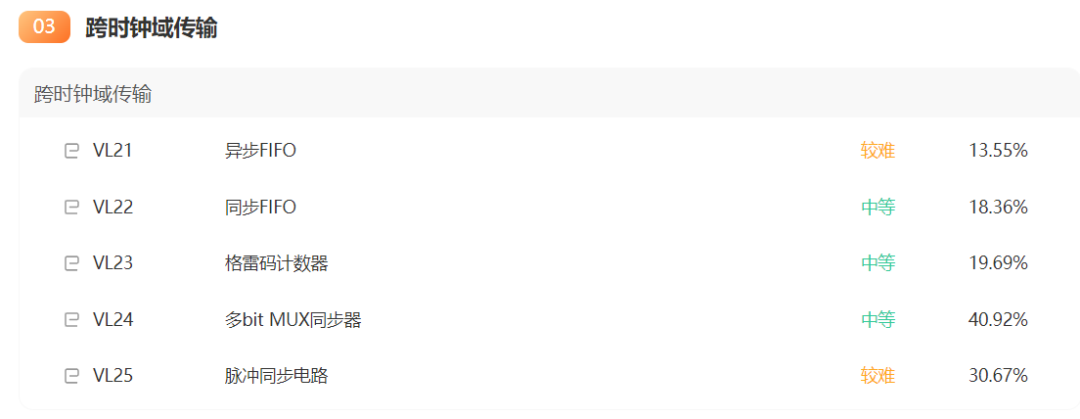

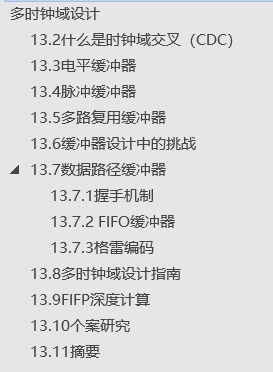

跨时钟域传输

这部分本来要写的,但是准备是做个专题的,这几天会整理好发出来:

这部分也可以参考《高级FPGA设计技巧!多时钟域和异步信号处理解决方案》,虽然没有代码,但是理论知识很基础。

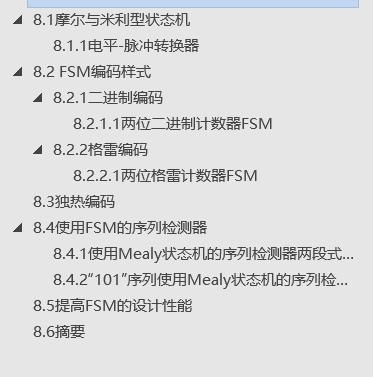

序列检测 & 时序逻辑

这两部分重点还是考察有限状态机,这部分也会在后续出个专题介绍:

包括后续的交通灯都有涉及。

基础部分

基础部分题目都比较简单,主要涉及基本Verilog语法,组合逻辑和时序设计,这几部分大部分内容我都在下列文章中有过介绍:

《数字硬件建模-Verilog篇阶段总结及SystemVerilog篇介绍》

差不多就这样,有什么问题大家可以后台留言,后续可以单独写文章讲解。

【Vivado那些事儿】在不重新安装 Vivado 的情况下,是否能够安装 Xilinx USB/Digilent 线缆驱动器?

数字硬件建模-Verilog篇阶段总结及SystemVerilog篇介绍

FPGA/IC内卷新“标准”-最新刷题网站公布

最后

以上就是妩媚书本最近收集整理的关于牛客网题目简析VL31 Johnson CounterVL29 单端口RAM & VL30 RAM的简单实现VL26 简易秒表 & VL27 可置位计数器 & VL28 加减计数器跨时钟域传输序列检测 & 时序逻辑基础部分的全部内容,更多相关牛客网题目简析VL31内容请搜索靠谱客的其他文章。

发表评论 取消回复