在FPGA中,状态机是比较常用的。特别是要处理一些串行执行的操作。但是对于我们编写的状态机,综合出来的电路应该是长什么样子的了?这个在初学的时候都是不关心的,但是深入的话,还是要了解的。

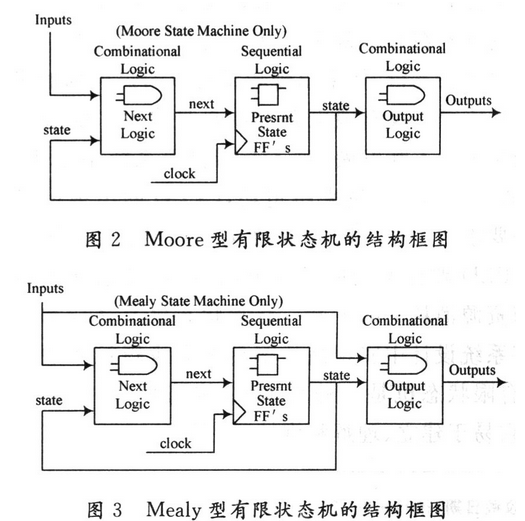

状态机分为两种,一种是moore型,一种是mealy型。两种的区别就是输出逻辑是否会由输入决定。

如下图:

状态机分为三部分模块

第一部分为次态组合逻辑电路,通过将状态输出反馈到次态组合逻辑电路,在和输入信号决定,下一状态是什么状态。

第二部分就是时序电路,就是一个触发器,将下一状态的值给现在的状态

第三部分是输出逻辑,通过判断当前的状态,得到输出

module led(

input clk,

input rst_n,

input change,

output reg [3:0] led

);

localparam led_0001 = 'd0;

localparam led_0010 = 'd1;

localparam led_0100 = 'd2;

localparam led_1000 = 'd3;

reg [1:0] state;

//

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

state <= led_0001;

else

case(state)

led_0001:

if(change)

state <= led_0010;

led_0010:

if(change)

state <= led_0100;

led_0100:

if(change)

state <= led_1000;

led_1000:

if(change)

state <= led_0001;

endcase

end

//

`define use_case

`ifdef use_case

always@* begin

case(state)

led_0001: led = 4'b0001;

led_0010: led = 4'b0010;

led_0100: led = 4'b0100;

led_1000: led = 4'b1000;

endcase

end

`else

//

always@* begin

if(state == led_0001)

led = 4'b0001;

else if(state == led_0010)

led = 4'b0010;

else if(state == led_0100)

led = 4'b0100;

else

led = 4'b1000;

end

`endif

endmodule

功能其实很简单,有4个状态,按照普通二进制编码。每个状态在输入信号change有效的时候状态跳转。在每个状态,4个LED输出是不一样的。

在代码中,使用了预编译`ifdef。这里输出逻辑采用if和case来实现,比较看看综合出来的电路区别。

ref

http://blog.chinaaet.com/weiqi7777/p/40172

最后

以上就是隐形雪糕最近收集整理的关于FPGA状态机电路综合分析的全部内容,更多相关FPGA状态机电路综合分析内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复