文章目录

- 题目

- 题解

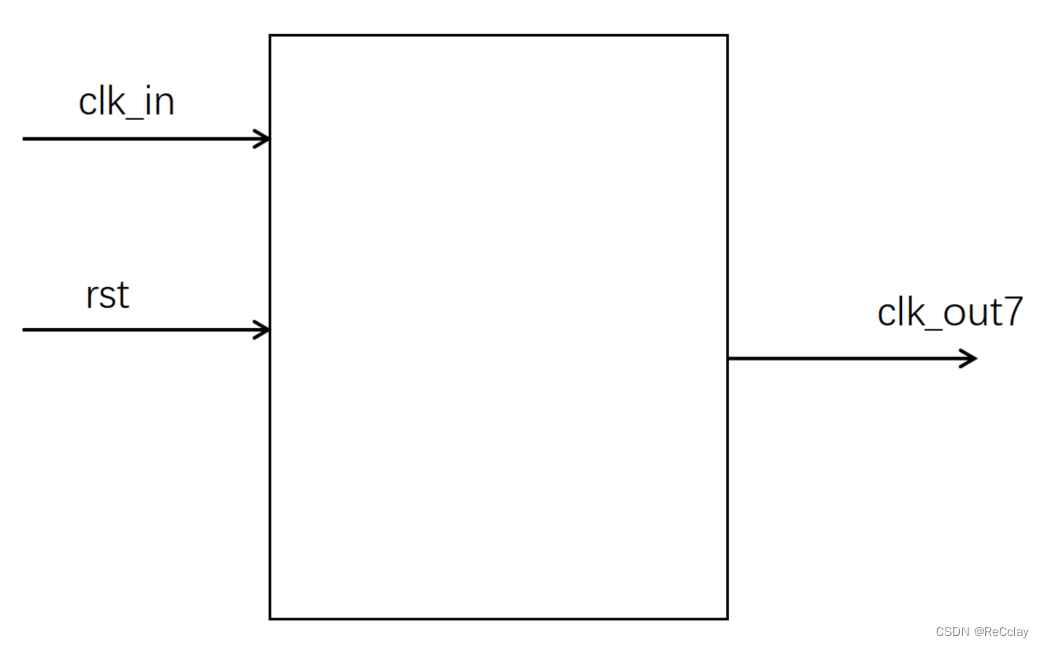

题目

描述

设计一个同时输出7分频的时钟分频器,占空比要求为50%

注意rst为低电平复位

信号示意图:

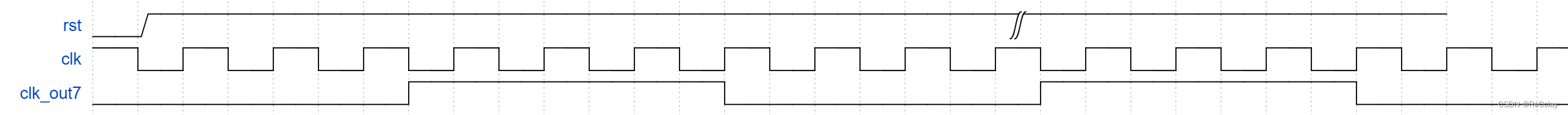

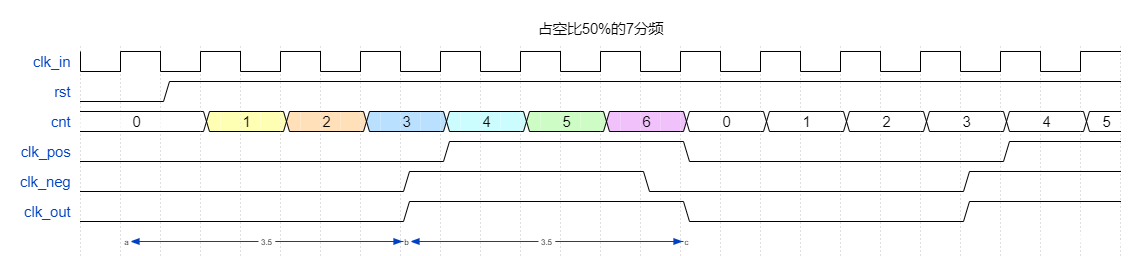

波形示意图:

输入描述:

输入信号 clk_in rst

类型 wire

输出描述:

输出信号 clk_out7

类型 wire

题解

`timescale 1ns/1ns

module odo_div_or

最后

以上就是复杂冥王星最近收集整理的关于【校招Verilog进阶挑战】 时序逻辑篇:VL16 占空比50%的奇数分频题目题解的全部内容,更多相关【校招Verilog进阶挑战】内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复