verilog行为级建模(behavioral model)

Verilog HDL的抽象层级

- 行为级(behavioral) ,更高层级的对逻辑的行为进行建模;

- RTL级 逻辑在寄存器级(register level)进行建模;

- 结构级(structural) 逻辑在寄存器和门级进行建模;

程序块(procedural blocks)

Verilog的行为级代码一般要写在程序块内部,但也有例外。

Verilog中有两种程序块:

initial:initial块在零时刻开始执行,且仅执行一次。

always:always块一次次地循环执行,换言之,就像它的名字所说的那样,它一直(always)执行。

举例

module initia—l_example();

reg clk, reset, enable, data;

initial begin

clk = 0;

reset = 0;

enable = 0;

data = 0;

end

endmodule

module always_example();

reg clk,reset,enable,q_in,data;

always @ (posedge clk)

if (reset) begin

data <= 0;

end else if (enable) begin

data <= q_in;

end

endmodule

上例中,initial block从零时刻开始执行,不需要等待;always block需要等待“触发事件”的发生,此处为时钟的上升沿,执行过一次后,再次等待下一次“触发事件”的发生。

顺序赋值语句

1、顺序赋值语句给reg, integer, real或者time变量赋值,不能给nets(wire数据类型)赋值。

2、可以给寄存器(reg类型)赋值为net(wire类型)、常数、其他寄存器或一个特定值。

顺序赋值组(procedural assignment group)

如果一个顺序块包含了不止一条声明,这些声明应当被包括在:

1、顺序begin - end块

2、并行frok - jion块

使用 begin-end 时,可以给这个group起名,我们称之为 named blocks

举例

例一

module initial_begin_end();

reg clk, reset, enable, data;

initial begin

$monitor(

"%g clk = %b reset = %b enable = %b data = %b",

$time, clk, reset, enable, data);

#1 clk = 1;

#10 reset = 1;

#3 enable = `;

#5 data = 0;

#1 $finish;

end

endmodule

begin:clk在延时一个时间单位后为0,reset延时11个时间单位后为0,16个时间单位后使能(enable),19个时间单位后data赋值为0。所有的语句顺序执行。

begin-end块的特点:

顺序执行

延时累积

块在最后一条语句之后结束

模拟结果:

0 clk=x reset=x enable=x data=x

1 clk=0 reset=x enable=x data=x

11 clk=0 reset=0 enable=x data=x

16 clk=0 reset=0 enable=0 data=x

19 clk=0 reset=0 enable=0 data=0

例二

1 module initial_fork_join();

2 reg clk,reset,enable,data;

3

4 initial begin

5 $monitor("%g clk=%b reset=%b enable=%b data=%b",

6 $time, clk, reset, enable, data);

7 fork

8 #1 clk = 0;

9 #10 reset = 0;

10 #5 enable = 0;

11 #3 data = 0;

12 join

13 #1 $display ("%g Terminating simulation", $time);

14 $finish;

15 end

16

17 endmodule

fork:一个时间单位后clk被赋值,10个时间单位后reset被赋值,5个时间单位后enable被赋值,3个时间单位后data被赋值。所有语句并行(同时)执行。

特点:

同时执行

块在最后一条语句完成后结束(延迟最高的语句,它可以是块中的第一条语句)

模拟结果:

0 clk=x reset=x enable=x data=x

1 clk=0 reset=x enable=x data=x

3 clk=0 reset=x enable=x data=0

5 clk=0 reset=x enable=0 data=0

10 clk=0 reset=0 enable=0 data=0

11 Terminating simulation

阻塞和非阻塞赋值(Blocking and Nonblocking assignment)

- 阻塞赋值按照程序的排列顺序执行。

因为直到当前语句执行完毕才能执行下一跳语句,即“阻塞”了下一条语句的执行,所以被称为阻塞赋值。

阻塞赋值用 “=”,如 a = b;

- 非阻塞赋值是并行执行的。由于当前语句的执行不会阻塞下一条语句的执行,因此称为非阻塞语句。

非阻塞赋值用 “<=”,如 a <= b;

举例

1 module blocking_nonblocking();

2

3 reg a,b,c,d;

4 // Blocking Assignment

5 initial begin

6 #10 a = 0;

7 #11 a = 1;

8 #12 a = 0;

9 #13 a = 1;

10 end

11

12 initial begin

13 #10 b <= 0;

14 #11 b <= 1;

15 #12 b <= 0;

16 #13 b <= 1;

17 end

18

19 initial begin

20 c = #10 0;

21 c = #11 1;

22 c = #12 0;

23 c = #13 1;

24 end

25

26 initial begin

27 d <= #10 0;

28 d <= #11 1;

29 d <= #12 0;

30 d <= #13 1;

31 end

32

33 initial begin

34 $monitor("TIME = %g A = %b B = %b C = %b D = %b",$time, a, b, c, d);

35 #50 $finish;

36 end

37

38 endmodule

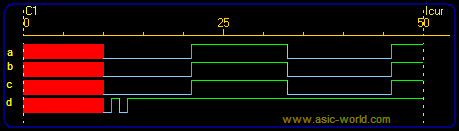

波形:

最后

以上就是标致雪碧最近收集整理的关于verilog行为级建模(1)verilog行为级建模(behavioral model)的全部内容,更多相关verilog行为级建模(1)verilog行为级建模(behavioral内容请搜索靠谱客的其他文章。

发表评论 取消回复