HDLBits Module

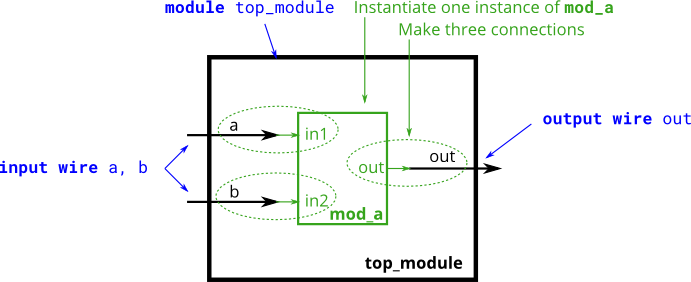

模块调用

方法

By position

mod_a instance1 ( wa, wb, wc );

通过端口位置一一对应,以此来实现两个模块之间的连接,但当其中一个模块的端口位置发生改变,就需要对相应连接的线进行重新连接。及线连接的对象会因为端口位置的变化而变化。

By name

mod_a instance2 ( .out(wc), .in1(wa), .in2(wb) );

该方法是通过端口名字的一一对应来实现连接,通过该方法就不需要考虑模块端口的位置变化。

实例代码:

//通过位置

module top_module ( input a, input b, output out );

mod_a ins1 (a,b,out);

endmodule

//通过名字

module top_module ( input a, input b, output out );

mod_a ins2 (.in1(a),.in2(b),.out(out));

endmodule

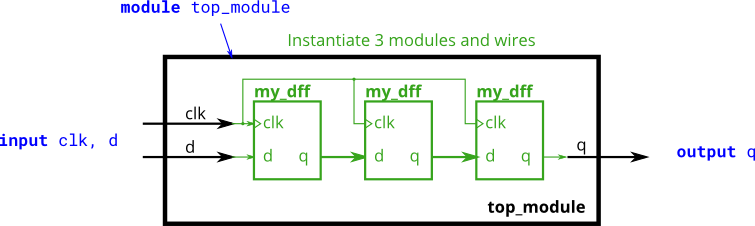

多模块连接

例题

The module provided to you is: module my_dff ( input clk, input d, output q );

代码实现:

//通过名称

module top_module ( input clk, input d, output q );

wire qd1,qd2;

my_dff ins1 (

.clk(clk),

.d(d),

.q(qd1)

);

my_dff ins2 (

.clk(clk),

.d(qd1),

.q(qd2)

);

my_dff ins3 (

.clk(clk),

.d(qd2),

.q(q)

);

endmodule//通过地址

module top_module (

input clk,

input d,

output q

);

wire a, b; // Create two wires. I called them a and b.

// Create three instances of my_dff, with three different instance names (d1, d2, and d3).

// Connect ports by position: ( input clk, input d, output q)

my_dff d1 ( clk, d, a );

my_dff d2 ( clk, a, b );

my_dff d3 ( clk, b, q );

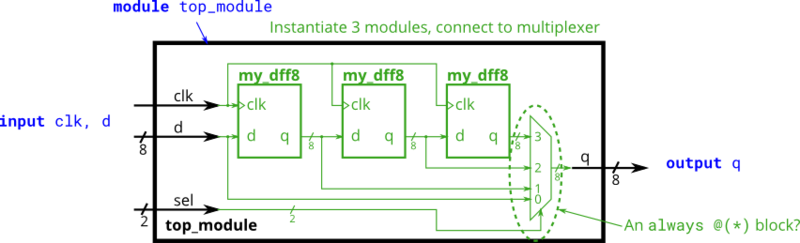

endmodule进阶:

//通过名字

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output [7:0] q

);

wire [7:0]out1,out2,out3;

my_dff8 dff1 (

.clk(clk),

.d(d),

.q(out1)

);

my_dff8 dff2 (

.clk(clk),

.d(out1),

.q(out2)

);

my_dff8 dff3 (

.clk(clk),

.d(out2),

.q(out3)

);

always @(*) begin

case (sel)

2'b00: q = d;

2'b01: q = out1;

2'b10: q = out2;

2'b11: q = out3;

endcase

end

endmodule//通过地址

module top_module (

input clk,

input [7:0] d,

input [1:0] sel,

output reg [7:0] q

);

wire [7:0] o1, o2, o3; // output of each my_dff8

// Instantiate three my_dff8s

my_dff8 d1 ( clk, d, o1 );

my_dff8 d2 ( clk, o1, o2 );

my_dff8 d3 ( clk, o2, o3 );

// This is one way to make a 4-to-1 multiplexer

always @(*) // Combinational always block

case(sel)

2'h0: q = d;

2'h1: q = o1;

2'h2: q = o2;

2'h3: q = o3;

endcase

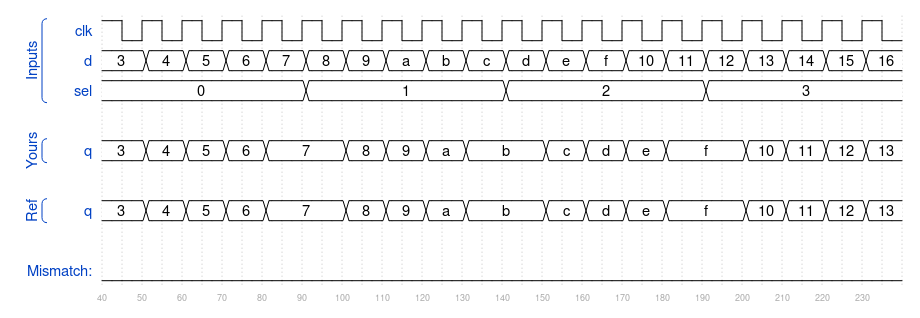

endmodule实现效果:

全加器:

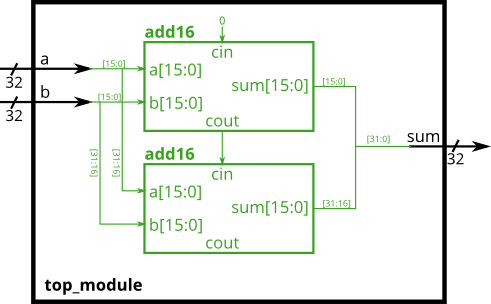

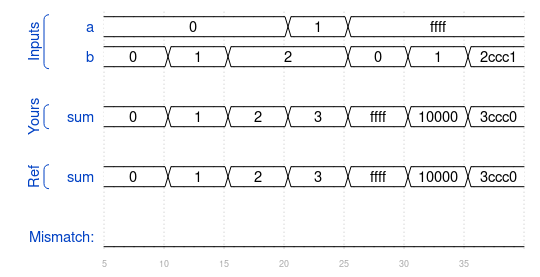

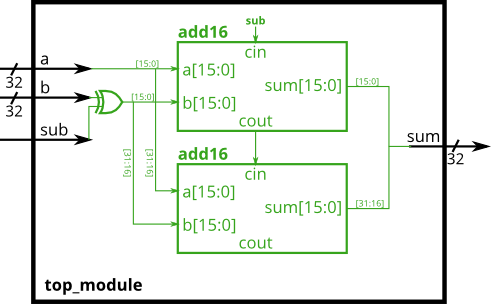

16位*2拼接32位:

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire c;

add16 add_1 (

.a(a[15:0]),

.b(b[15:0]),

.cout(c),

.sum(sum[15:0])

);

add16 add_2 (

.a(a[31:16]),

.b(b[31:16]),

.cin(c),

.sum(sum[31:16])

);

endmodule

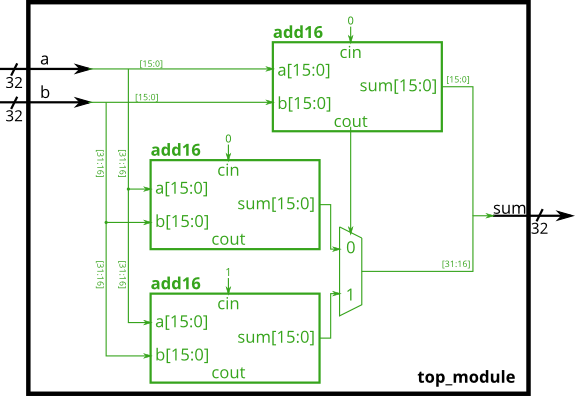

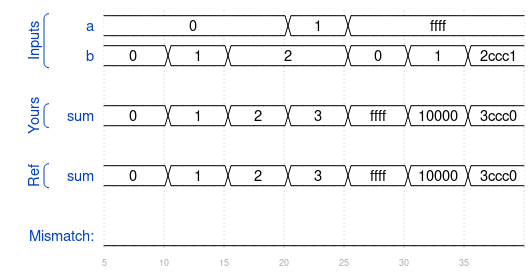

并行加法器:

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire out,in;

wire [15:0]out1,out2;

assign in = 1;

add16 add_1 (

.a(a[15:0]),

.b(b[15:0]),

.sum(sum[15:0]),

.cout(out)

);

add16 add_2 (

.a(a[31:16]),

.b(b[31:16]),

.sum(out1),

.cin()

);

add16 add_3 (

.a(a[31:16]),

.b(b[31:16]),

.sum(out2),

.cin(in)

);

always @(*) begin

case (out)

1'b0: sum[31:16] = out1;

1'b1: sum[31:16] = out2;

endcase

end

endmodule

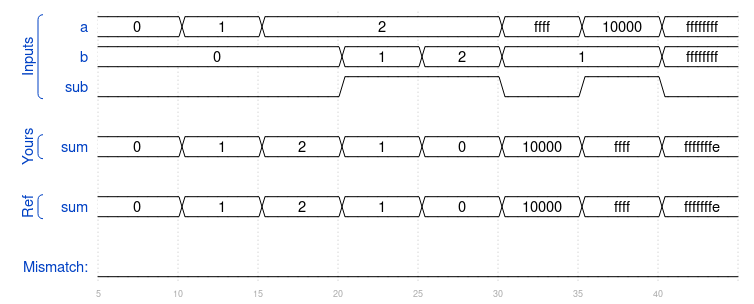

加减法器:

module top_module(

input [31:0] a,

input [31:0] b,

input sub,

output [31:0] sum

);

wire [31:0]b2;

wire out;

assign b2 = b ^ {32{sub}};

/*也可以使用如下方法实现xor:

always @(*) begin

case (sub)

1'b0: b2 = b;

1'b1: b2 = ~b;

endcase

end

或者:

assign b2 = sub? (~b):b;

*/

add16 add_1 (

.a(a[15:0]),

.b(b2[15:0]),

.cin(sub),

.cout(out),

.sum(sum[15:0])

);

add16 add_2 (

.a(a[31:16]),

.b(b2[31:16]),

.cin(out),

.cout(),

.sum(sum[31:16])

);

endmodule

最后

以上就是花痴火龙果最近收集整理的关于verilog学习笔记(模块module)HDLBits Module模块调用多模块连接的全部内容,更多相关verilog学习笔记(模块module)HDLBits内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复