前言

本文将列举在动手设计 CPU 系列中使用到的各类元件真值表,并持续更新。

注意:本文所有操作环境均为 Quartus II 13.0

各类元件

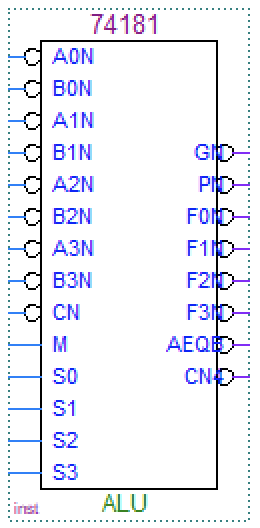

(1) 74181 — ALU

该元件即为 ALU,可实现四位数字的多种逻辑运算与算术运算,功能十分强大。

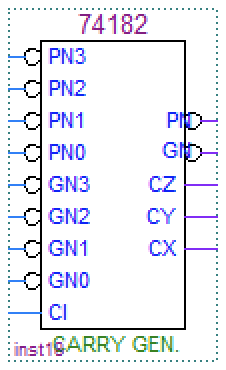

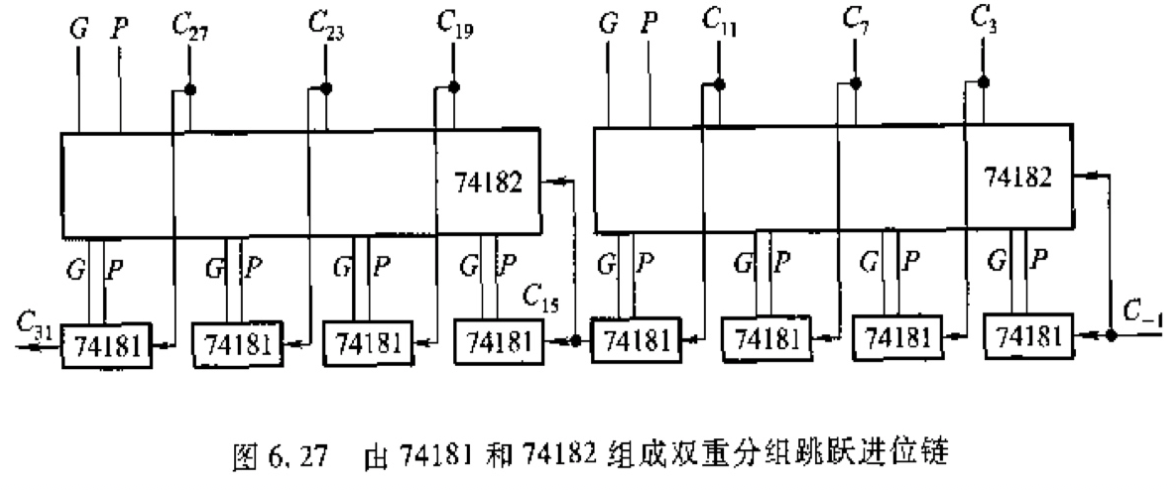

(2) 74182 — 用于并行加法器

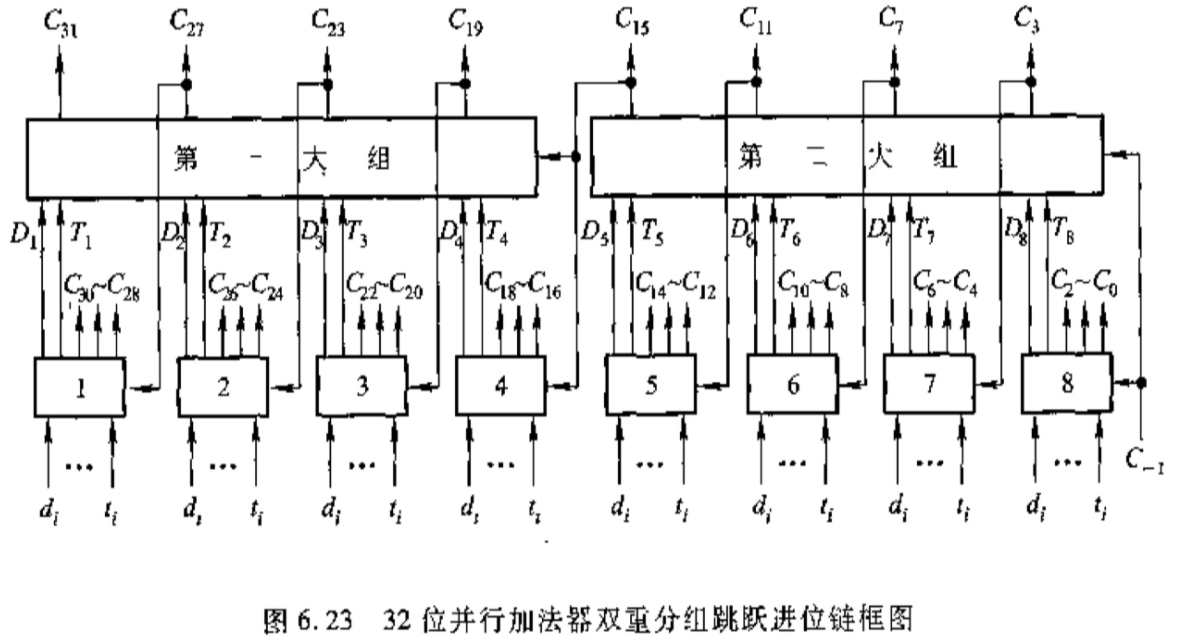

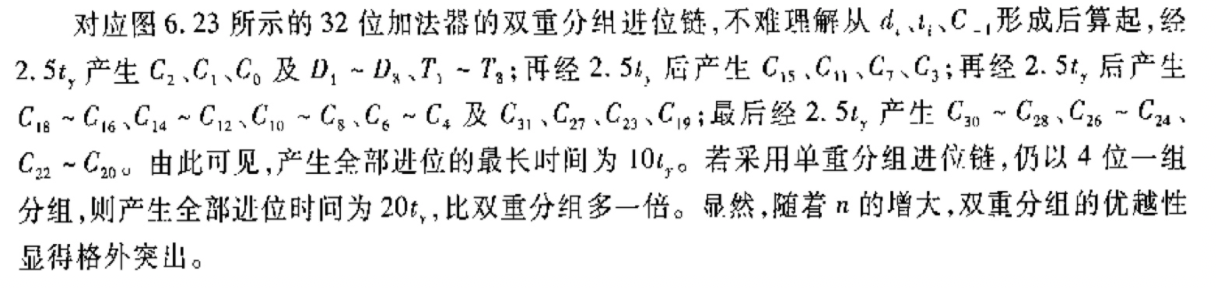

下述内容选自《计算机组成原理》(唐硕飞版)6.5 节。

双重分组跳跃进位

下述文字内容是课本中对于此种并行加法器的说明,详细计算过程可以参看书本,主要表达的观点就是此种并行加法器随着位数的增加,计算效率也将大大提升。

74181 与 74182 进行组合

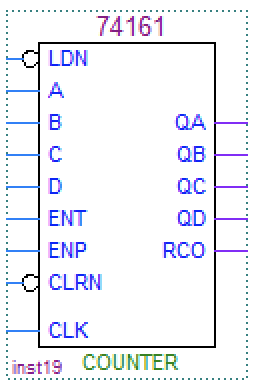

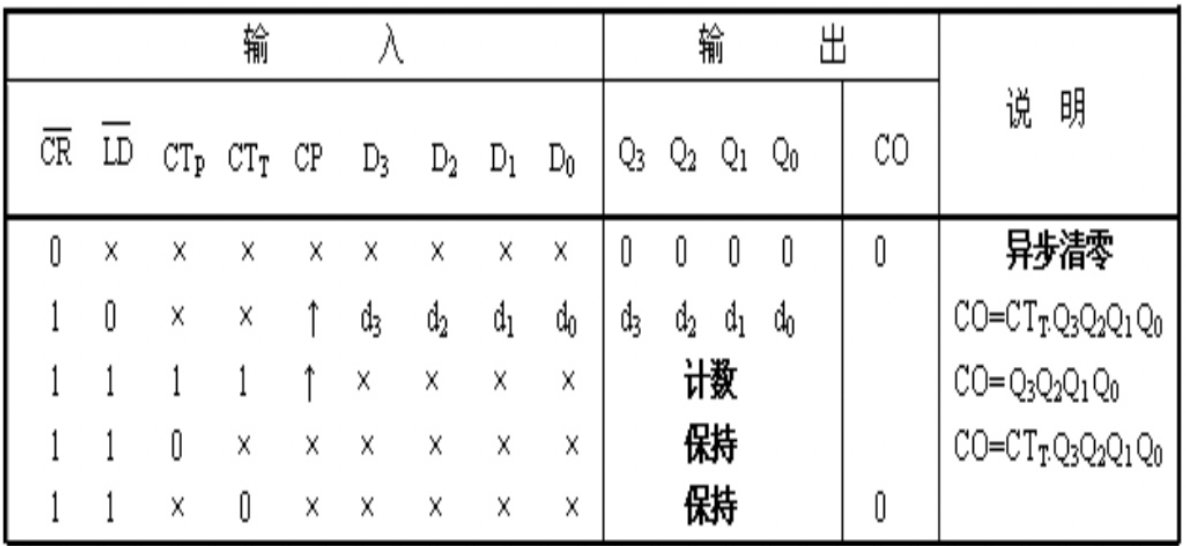

(3) 74161 — 四位同步二进制加法计数器

该计数器可以用于实现 PC、uPC 等计数器,并可进一步拼接实现 8 位乃至 16 位的计数器。

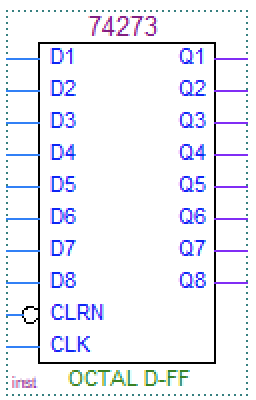

(4) 74273 — 八位寄存器

八位寄存器,其中 CLK 为时钟,上升沿打入,CLRN 为异步清 0 端。

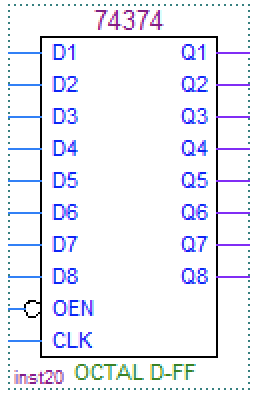

(5) 74374 — 锁存器

器件介绍

锁存器。(三态输出的寄存器,与 74273 无太大差别)

- D1~D8: 数据输入端

- OEN: 三态允许控制端(低电平有效)

- CLK: 时钟输入端

- Q1~Q8: 输出端

输出端 Q1~Q8 可直接与总线相连。当三态允许控制端 OEN 为低电平时,Q1~Q8 为正常逻辑状态,可用来驱动负载或总线。当 OEN 为高电平时,Q1~Q8 高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。

在时钟端 CLK 脉冲上升沿的作用下,Q 随数据 D 而变。

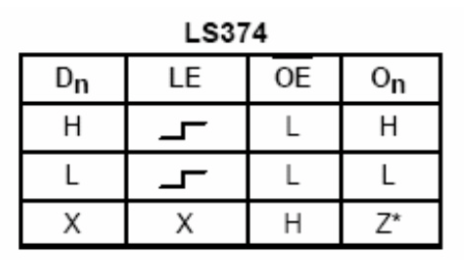

真值表

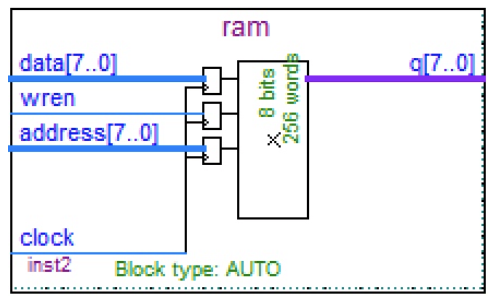

(6) RAM

- wren 低电平时读允许,高电平时写允许。

- CLK 下降沿打入

最后

以上就是欣喜小兔子最近收集整理的关于动手设计 CPU(一)—— 各类元件功能表的全部内容,更多相关动手设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复