1、实验内容

①采用D触发器实现同步模4可逆计数器

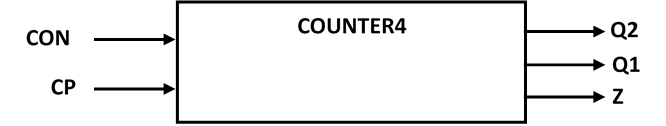

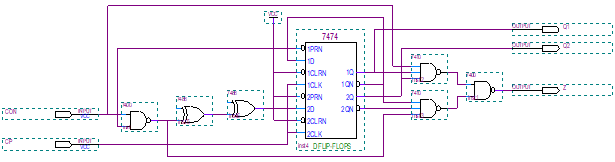

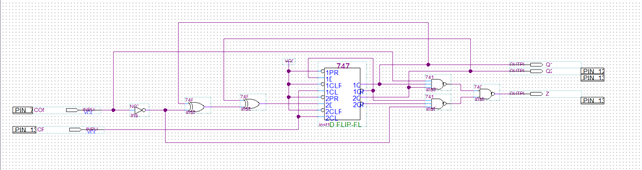

在掌握同步时序逻辑电路设计方法的基础上,要求采用D触发器、二输入与非门、三输入与非门和异或门设计一个可逆模4计数器,其框图如图3.11所示,其中CP为计数脉冲输入端,CON为可逆计数器的控制端(CON=1进行加计数,CON=0进行减计数),Q2Q1位计数输出端,Z为进位端。同步模4可逆计数器原理图如图3.12所示。

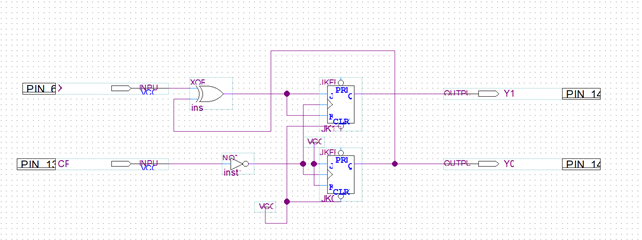

②采用JK触发器实现同步模4可逆计数器

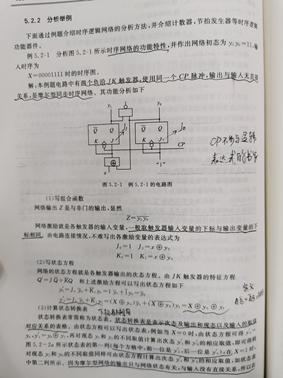

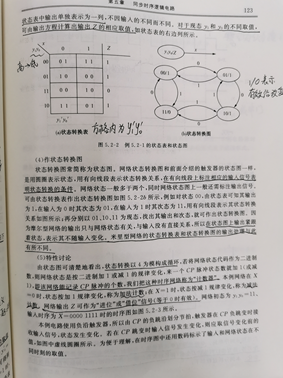

实验原理如教材所示:

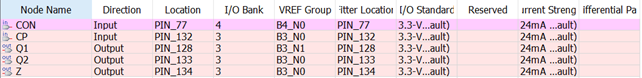

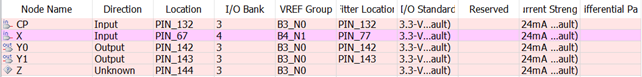

2、实验原理图

①用D触发器实现:

引脚分配图:

②用JK触发器实现:

引脚分配图:

最后

以上就是明理凉面最近收集整理的关于【2021山东大学数字逻辑实验6】 八位寄存器的全部内容,更多相关【2021山东大学数字逻辑实验6】内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复