一、日志(2019.3.4完成)

1.1、3位数码管实验下载:

在下载时首先要查看芯片的状态,是否与实际芯片相符,通过assignment->device进行查看,由于我的板子是cyclone||-ep2c5t144c8,便设置。如果不设置的话,在下载的过程中会报错,提示板子的型号不正确。

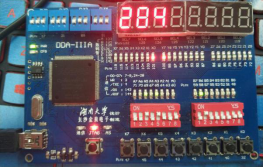

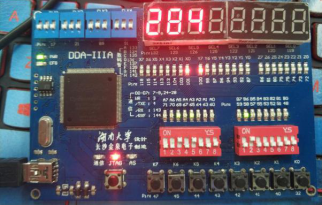

选好板子后再通过assignment->pins进行针脚设置。之后再进行全编译,为processing->compiler tool进行全编译。之后通过tools->programmer进行下载,注意驱动设置为USB,选择正确的sof文件。下载后的结果如图所示

实际上在实际中是一种频闪的状态,这是由于clk3的时钟信号的频率只有1Khz,已经可以产生视觉暂留。可以通过下方的拨码开关对显示数值进行调整,拨码开关每四位一组,满足“8421”。修改左上方的时钟信号的档位可以对时钟信号的频率进行微调,发现是进行频闪,且顺序为从左到右依次闪烁。

1.2、示波器测量位选信号和时钟信号:

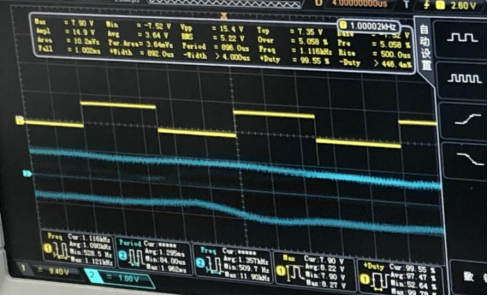

时钟信号:

其中的黄色是时钟信号,可以看出时钟信号是一个十分规整的方波,占空比大约为50%,频率为1.00002KHZ,这与时钟信号的特性有关。

位选信号:

可以看出位选信号也是一个方波,但占空比不一定为50%,而是60%,这是因为我们这里是三个数码管循环显示,在计数器的时候产生的是0,1,2,3,其比值为2:1:1:1,其中0表示了一个数码管,1表示了一个数码管,2,3共同表示了一个数码管,导致最终的三个数码管的时间之比为2:1:2。其频率为200.005HZ

二、报告

2.1、实验目的:

实验目的是熟悉quartus||的数字系统设计流程,DDA系列数字系统实验平台的使用,图形输入、文本输入(硬件描述语言)、层次设计的过程,三位数码管的使用方法、代码编写和针脚设计,以及图形输入的注意事项和画图技巧。

我的实验资源是一台基于windows 10 专业版的联想拯救者r700电脑,一块装有cyclone||-ep2c5t144c8的DDA数字系统实验平台,以及quartus||配套软件

2.2、设计

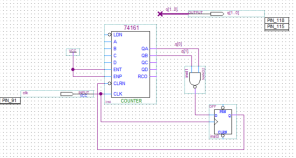

2.2.1、模4计数器电路图:

如图所示,即为一个模4计数器,其中由于仅仅是用来计数,所以a~d不需要输入,而由于是用来进行连续的输出,所以直接将两个使能端ent和enp设置为vcc高电平,使其永远成立。而qa和qb是输出端,其中qa是低位,qb是高位,并进行输出。取nand后当且仅当两者全为1的时候会输出0,而当他输出0的时候发生器dff会产生一个时钟周期的停留,所以展示出来的结果就是数字0占据了两个时钟周期,而1,2,3都只占据了一个时钟周期。如图所示:

2.2.2、模4计数器下载:

首先设置阵脚(由于之前芯片已经设置好了,所以不需要进行额外的更改),这里为了可以直观显示,将始终的阵脚设置为91,将输出的阵脚设置为二极管118~115,然后进行全编译,再进行下载,下载结果为:

可以看出在设置时钟信号为最低档的时候,可以很明显的看到二极管118和115在交替闪烁,闪烁的规律大致为00(全灭)->01->10->11(全亮),并且00的时间明显要长于其他情况。此现象和仿真的结果相吻合,所以证明电路行为正确,并得出结论:74161模块是一个计数模块,通过clrn端口进行置零,并进行计数,最高可以达到15。

2.2.3、比较仿真验证与下载验证:

仿真验证有时序仿真和功能仿真两种,功能仿真是在忽略了所有的延迟之后进行的仿真,仅仅用来考察功能是否正确;时序仿真添加上了延迟。实际上在我们的实验过程中功能仿真已经足够我们进行观察是否正常。

下载验证是将所写好的mof文件通过USB接口下载到板子上,然后板子开始运行程序,通过观察板子上出现的现行,比方说二极管发光,数码管显示等来变相观察代码是否正确。

总的来说,一般先进行仿真验证再进行下载验证,一方面是因为通过仿真波形图可以比实际下载更轻松更直接的找出可能出现的错误;另一方面是因为如果程序本身出现了结果上的问题,直接下载到板子上可能会导致板子出现错误,发生损坏等。

2.3、实现

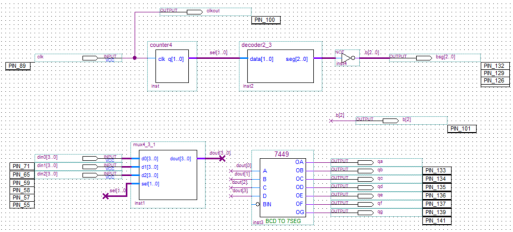

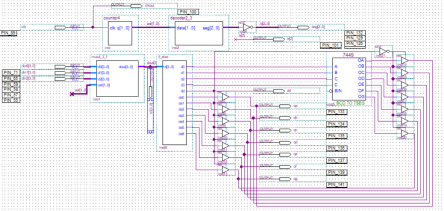

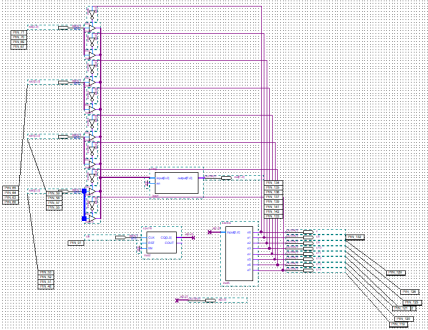

2.3.1、顶层电路

可以看出整个电路大致是通过四个模块组成,左上角的是一个counter4模块,即上文的模4计数器;右上角的是一个2-3译码器,将模4计数器产生的两位信号进行译码,译码成一个三位的信号用来控制三个位选信号,以此来控制三个数码管进行显示;左下角是一个4-3-1模块,是自己写出来用来通过拨码开关对数码管上的显示数字进行控制的模块,其产生的数据dout将会传给右下角的模块;右下角的模块式一个7449芯片,用来进行4-7的BCD译码,以此来对段选信号进行控制,通过从ABCD输入的一个四位二进制数,对其进行编译解码,是之可以在数码管上进行显示,比方说数字0展示在数码管上就要求段选信号a~g的值是1111110。

2.3.2下载

结果如图:

注意我在这里进行了修改,由于时钟信号clk4的频率太低,在使用时会出现频闪的情况,所以我使用了clk3,即针脚89代替了针脚91的clk4,通过此方法来得到一个不会发生可视频闪的三位数码管展示。以下为输入0~f时的符号显示结果

| 输入数值 | 译码情况 | (段选信号) |

|---|---|---|

| 0 | (0000) | 1111110 |

| 1 | (0001) | 0110000 |

| 2 | (0010) | 1101101 |

| 3 | (0011) | 1111001 |

| 4 | (0100) | 0110011 |

| 5 | (0101) | 1011011 |

| 6 | (0110) | 0011111 |

| 7 | (0111) | 1110000 |

| 8 | (1000) | 1111111 |

| 9 | (1001) | 1110011 |

| a | (1010) | 0001101 |

| b | (1011) | 0011001 |

| c | (1100) | 0100011 |

| d | (1101) | 1001011 |

| e | (1110) | 0001111 |

| f | (1111) | 0000000 |

这里可以很明显的看出,在quartus2里面的7449芯片不能完全处理0-f的所有情况,所以需要在下面对电路图进行改进,需要改进显示6,9以及a-f的情况,在这里我通过设置新的模块来达到优化的目的。

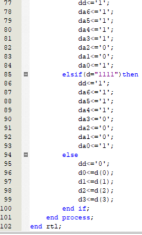

2.3.3优化

由于需要在不删除7449芯片的时候进行优化,所以想到可以自己新建两个模块,一个模块是将判断是否可以使用7449芯片,另一个是在7449芯片不能使用的时候进行补充替换,后来在实际制作的过程中发现实际上两个模块可以进行合并。由此先得到6,9以及a~f的段选信号表示:

| 输入数值 | 段选信号值 |

|---|---|

| 6(0110) | 1011111 |

| 9(1001) | 1111011 |

| a(1010) | 1110111 |

| b(1011) | 0011111 |

| c(1100) | 1001110 |

| d(1101) | 0111101 |

| e(1110) | 1001111 |

| f(1111) | 1000111 |

经过优化后最终电路图如下:

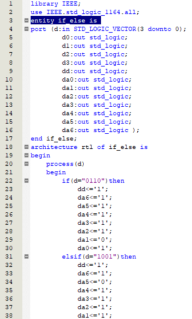

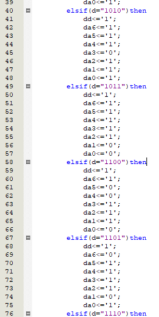

其中新加模块if_else为:

这里是通过直接加入一个if_else模块,当d(数据)的值不是6,9,af的时候,就直接输出输入的数据,将数据导入到7449模块中进行译码;而如果满足6,9,af的时候,就直接在该模块中进行译码。同时输出一个dd判断信号,用来判断是通过那个模块得到的数值,再通过该判断信号对三态门进行控制,将两个模块所得到的值进行汇总融合便可以达到0~f全显示的目的。最终结果如下:

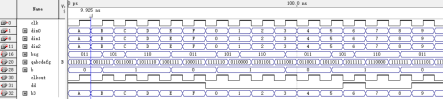

仿真结果为:

由于针脚没有改变,所以不需要重新设定针脚的值,芯片与阵脚保持不变,直接全编译

通过下载的结果可知,符合仿真结果,实验正确

三、总结

3.1、学到的知识点:

学习到了对数码管的使用方法,以及段选信号和位选信号的作用究竟是什么。可以自己使用数码管进行简单的编译和制造调用,为以后的多种输出,输出数量超过了板子所能承受的最大数量的时候,可以通过数码管进行结果展示。还熟悉了下载的方法。

3.2、掌握的技能:

数码管的简单使用——跑马灯

这是我在闲暇之余帮同学做的一个生日礼物,本来想通过数码管来显示“birthday”这个单词,后来发现实在是太麻烦了,所以没有办法,就设计成了简单的跑马灯,并且可以通过拨码开关来设置数值,也算是加深一下自己对板子的理解。

这个的原理实际上是通过对段选信号和位选信号的使用。首先我这里通过一个计数器来对时钟进行分组,将八个时钟分为一组,分别对应八位数码管中的每一位,使每个周期只有一个数码管点亮。通过拨码开关输入数值,由于拨码开关总共只有十六位,所以每四位拨码开关对应两个数码管。通过一个BCD码3-8译码器,对输入进行译码,转换成段选信号,注意之所以八位,因为段选信号本身就是八位,除了常见的a~g之外还有一个h用来控制每两位数码管之间的小数点,也要进行设置避免出错。通过三态门对输入、输出进行控制。最终每个时钟只有一组段选信号传播到输出端,只有一个数码管会进行显示。

最后在实验的时候出现了一点问题(对0~f的设置不是很正确,而且由于我一开始的初衷是写出来一个显示“birthday”的跑马灯,所以很多字母需要自己设置),但最终还是实现了birthday的跑马灯展示,如图所示:

3.3、人文:

还是要尽量少熬夜,虽然这篇报告的初稿是我在接到任务后的当天晚上写出来的,一直写到了凌晨四点,或者说第二天的早晨四点,但感觉还是要减少熬夜的次数,毕竟身体才是本钱,为了学习这么拼命容易得不偿失的。

3.4、记忆:

表格型:如上面我多次运用了表格的方法,对输入的可能情况进行设定以及整合,并对输出进行书写与描述,最终得到了一个输入与输出的对应表格,通过这个表格,我在编写代码的时候就少走了很多的弯路,感觉优点很多。

树形:在本篇报告中树形其实并没有体现太多,但在我的电脑中体现的很丰富。由于这次实验时间跨度长,实验知识点多,所以需要记录的实验结果也很多;而我就在每次实验之后直接进行分门别类的放置和存储,并形成了一个相互嵌套的树形结构,这样在我这次编写实验报告的时候我可以很轻易的找到我所需要的实验记录,实验结果在哪里,为我撰写实验报告提供了很大的便利。

最后

以上就是开放芹菜最近收集整理的关于数字系统实验:三位数码管一、日志(2019.3.4完成)二、报告三、总结的全部内容,更多相关数字系统实验:三位数码管一、日志(2019内容请搜索靠谱客的其他文章。

发表评论 取消回复