FPGA中的串并转换

1、串并转换的思想

FPGA中的串并转换主要设计思想来源于用面积换速度,对数据流进行管理,FPGA中实现串并转换的主要方式有双口RAM,FIFO,移位寄存器等,对于数据量较大的一般使用双口RAM或者FIFO实现,数据量较小的使用移位寄存器实现。

2.串并转换的移位寄存器实现

代码如下:

module S2P(

input clk_bit,

input bit_valid,

input bit_data,

output [1:0] para_data,

output para_valid

);

reg [1:0] shift_data_reg = 2'b0; //移位寄存器

reg [1:0] shift_cnt; //移位计数

reg para_valid_reg = 0; //数据有效使能

reg [1:0] para_data_reg;

assign para_data = shift_data_reg;

assign para_valid = para_valid_reg;

always @(posedge clk_bit) begin

if (bit_valid) begin

shift_data_reg <= {shift_data_reg[0],bit_data};

if (shift_cnt) begin

para_valid_reg <= 1;

shift_cnt <= 0;

end

else begin

shift_cnt <= shift_cnt + 1;

para_valid_reg <= 0;

end

end

else begin

shift_data_reg <= 2'b0;

shift_cnt <= 0;

para_valid_reg <= 0;

end

end

endmodule

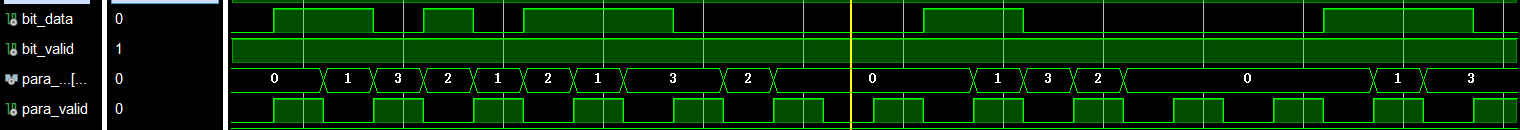

利用移位寄存器设计串并转换,采样使能端高电平才为有效数据。仿真结果如下:

最后

以上就是虚拟月光最近收集整理的关于verilog笔记(一)——串并转换FPGA中的串并转换的全部内容,更多相关verilog笔记(一)——串并转换FPGA中内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[Matlab]Simulink串口接收详解2用S-Function解析数据包1.概述2. 效果3. S-Function源码4. 文件说明及下载](https://www.shuijiaxian.com/files_image/reation/bcimg2.png)

发表评论 取消回复