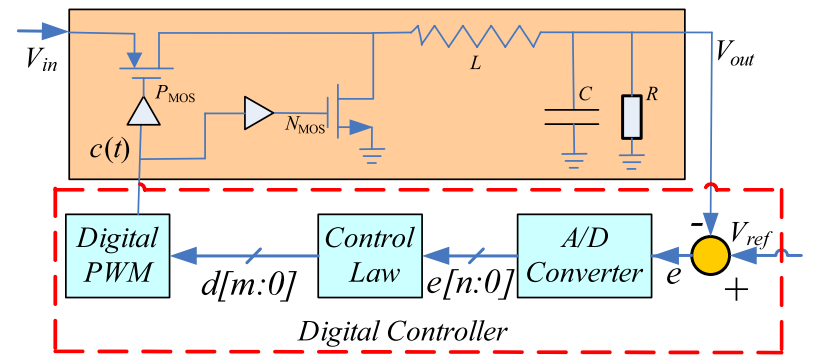

开关电源数字控制设计中,通常我们会使用FPGA来实现DPWM的设计,然后在传统DPWM的设计中,应用于高频时会有明显缺陷,对于FPGA的优化、面积和效率尤为重要。本文在传统DPWM设计的基础上,创新一种快速提高DPWM分辨率的FPGA设计方法,有效解决传统DPWM在高频PWM设计时的缺陷。

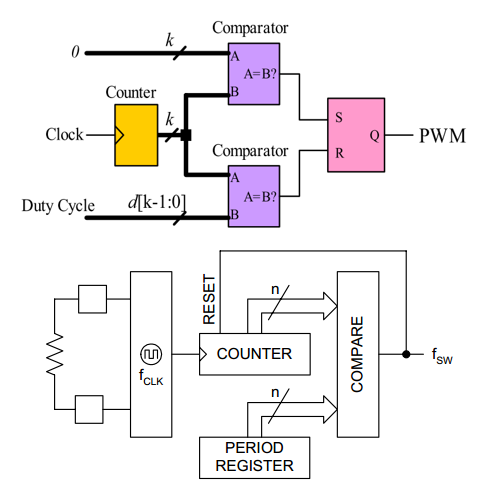

传统DPWM设计

fclk = 2^k * fsw

此方法原理简单,一个计数器,一个比较器!

致命缺陷:当开关频率需要很高时,所需要的系统时钟频率也会高的无法想象!!!

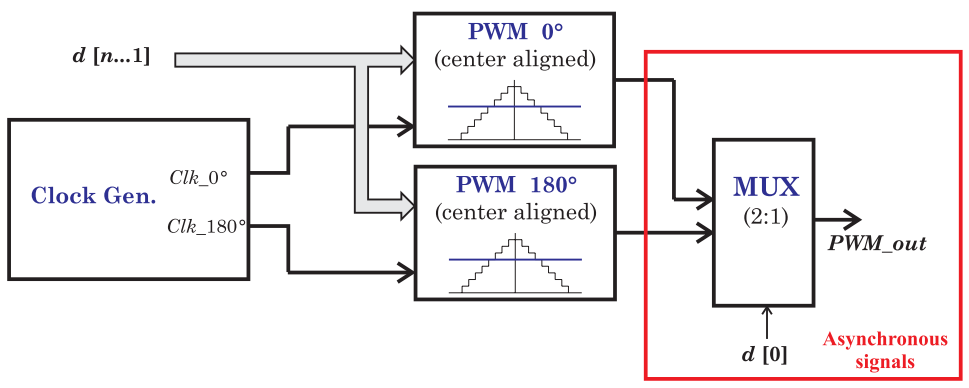

创新DPWM设计

系统框图:

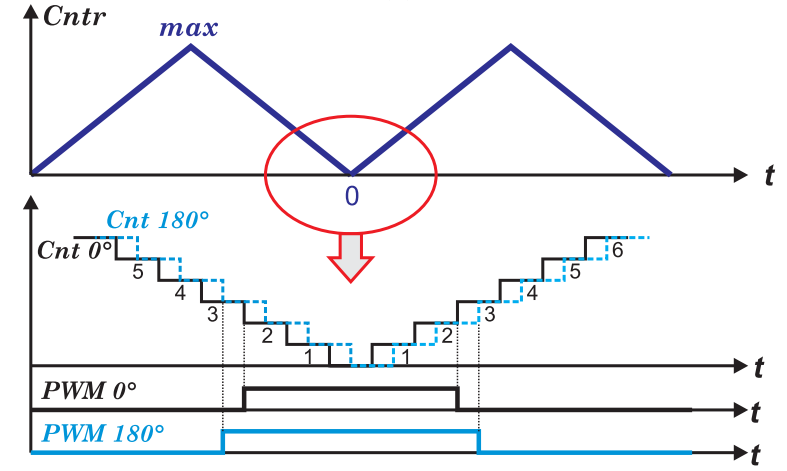

原理:

移相时钟,一个时钟不移相,另一个时钟移相180°

分别用两个时钟计数,与输入比较,得到两个PWM

输入信号d[n…1]的最后一位决定使用哪一个PWM

这样可提高DPWM的分辨率,比普通的DPWM多1位

最后

以上就是秀丽鸡最近收集整理的关于一种简单的可提高DPWM分辨率的FPGA设计方法传统DPWM设计创新DPWM设计的全部内容,更多相关一种简单内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复