参考视频:中国大学MOOC 芯动力——硬件加速设计方法 (2.1节)

本篇所有内容来源于《芯动力——硬件加速设计方法》此课程的教学视频 、ppt等相关资料。

一、VerilogHDL可综合概述

1. Verilog HDL 的基本功能之一是描述可综合的硬件电路。

对Verilog HDL的常见的误解:

- 很多语法规则与C语言相似,书写时可参考C语言;

- 追求代码的整洁、简短;

- 着眼于代码书写,性能优化由综合器实现;

- 把Verilog代码当做了程序,把电路设计当成了编程;

正确认知:

HDL : Hardware Description是硬件描述

HDL语言仅是对已知]硬件电路的文本表现形式编写前,对所需实现的硬件电路“胸有成竹”

Verilog HDL的基本功能之一是描述可综合的硬件电路。

相比C语言,最显著的区别在与HDL语言具备以下硬件设计的基本概念:

- 互连(connectivity ): wire型变量描述各个模块之间的端口与网线连接关系。

- 并发(concurrency):可以有效地描述并行的硬件系统。

- 时间(time):定义了绝对和相对的时间度量,可综合操作符具有物理延迟。

C语言是一种软件语言,所以并无上述硬件对象。

2.硬件描述语言描述的电路,最终将通过逻辑综合工具、布局布线工具将其实现为芯片。

但是,并不是 verilog中所有的关键词都可以被综合为硬件电路。

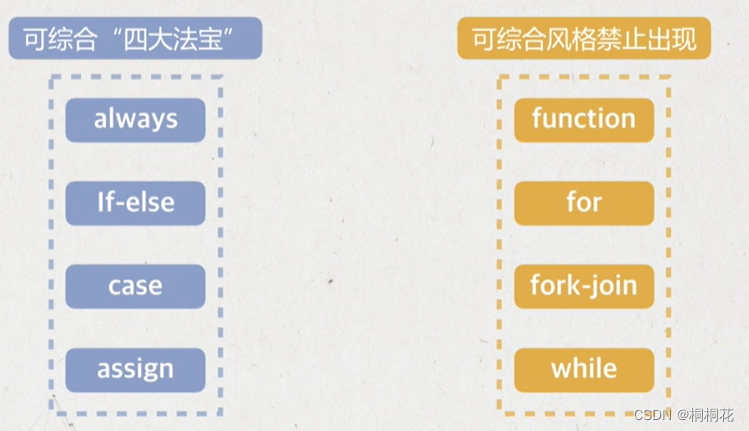

通常,只有四个关键字能够被综合为电路(称之为可综合四大法宝):

- always

- if-else

- case

- assign

除此以外,其他关键字都不可以被综合为硬件电路,例如function、for、fork join、while。

那么verilog中众多的关键字有什么存在价值呢?

这些不可综合的关键字都可以用于书写testbench,用来仿真

二、常见可综合语法与硬件的映射关系

if-else

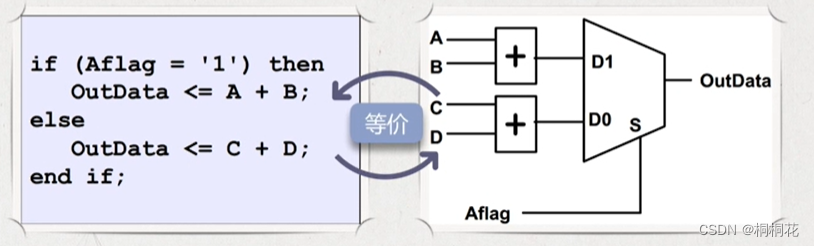

if-else通常会被逻辑综合其映射为多路选择器

输出结果由输入的条件决定。

举例:

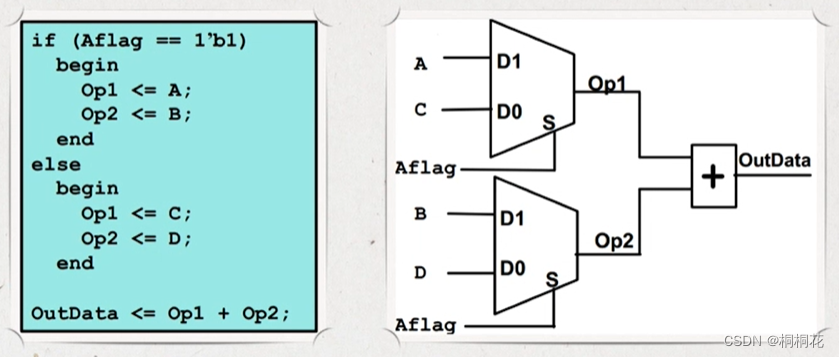

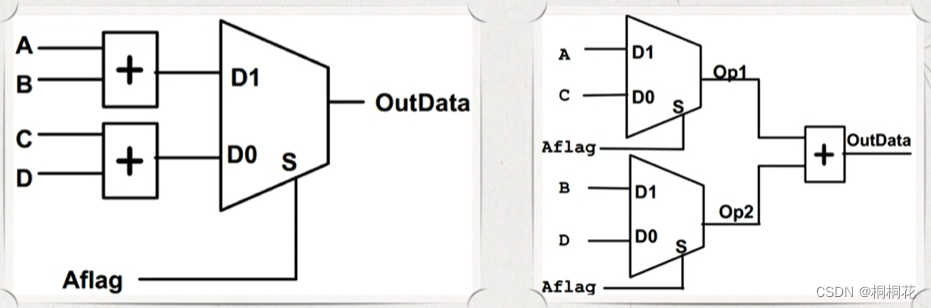

重构if-else映射的硬件结构:减少了一个加法器,减小了硬件的面积。(加法器结构较为复杂,晶体管比较多,少一个加法器,减小了面积)

问题:修改后的电路要比之前的电路好吗?

分析两种电路的传播延时:

第一个电路:

数据通道的延时:一个加法器和一个选择器

控制通道:一个选择器

第二个电路:

数据通道的延时:一个加法器和一个选择器

控制通道:一个选择器和一个加法器

所以,相比第一个电路,修改后的第二个电路控制通道延时比较大。

虽然第二个电路的面积比较小,但是如果控制信号Aflag信号来的比较晚,那么第二个电路的性能比第一个电路的性能要差。

需根据设计目标,小心设计:先"加"后“选",先“选"后“加”。

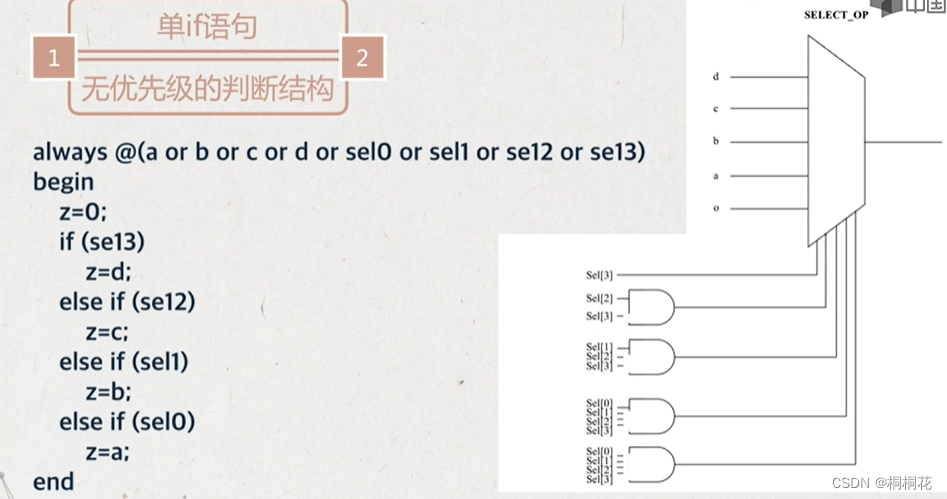

单if 语句

逻辑综合工具会将其映射为无优先级的判断结构。

推荐初学者尽量使用单if语句(if...else if.. .else if...)描述多条件判断结构。

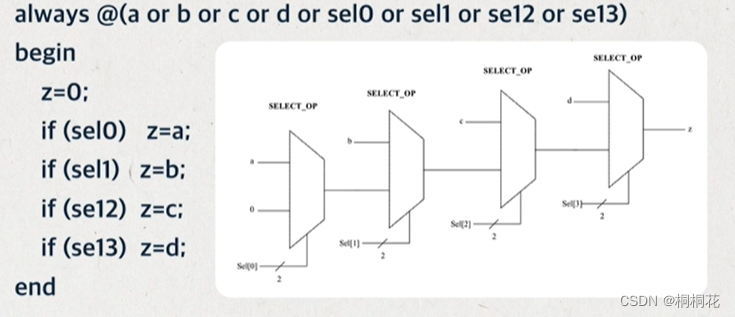

多if语句

逻辑综合工具会将其映射为有优先级的判断结构。

特点

- 最后一级选择信号具有最高优先级。

- 具有优先级的多选结构会消耗组合逻辑。(不推荐这种写法,有点乱。)

使用多if语句的情况:

若某些设计中,有些信号要求先到达(如关键便能信号、选择信号等),而有些信号需要

后到达(如慢速信号、有效时间较长的信号等),此时则需要使用if..if..结构。

设计方法:最高优先级给最迟到达的关键信号。

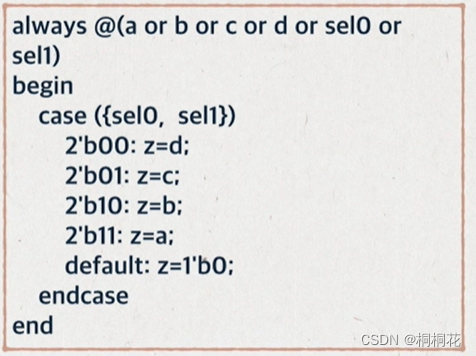

case

case是一种无优先级的判断结构。

case语句与单if语句的区别:case 的条件互斥。多用于指令译码电路。

三、电路设计需要注意的基本事项

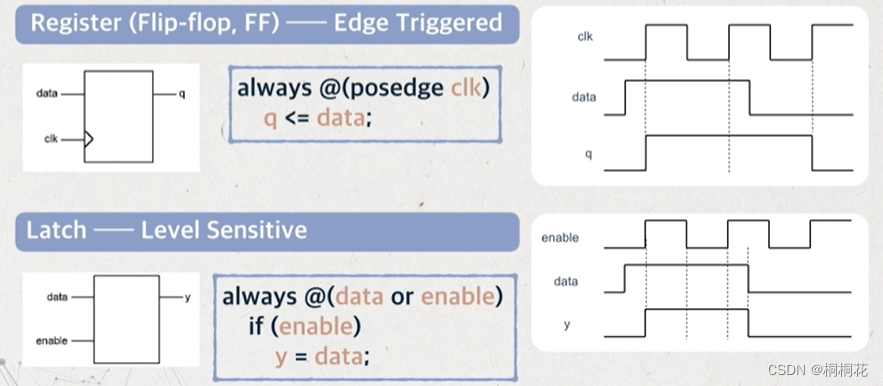

慎用latch

逻辑综合工具很难解释latch,因此,除非特殊用途,一般避免引入latch。

一般在异步电路和门控时钟会用到latch

慎用latch的原因:

- latch由电平触发,非同步控制。在使能信号有效时latch相当于通路,在使能信号无效时latch保持输出状态。DFF由时钟沿触发,同步控制。

- latch容易产生毛刺( glitch ),DFF则不易产生毛刺。

- latch将静态时序分析变得极为复杂。

一般的设计规则是:

在绝大多数设计中避免产生latch。latch最大的危害在于不能过滤毛刺。这对于下一级电路是极其危险的。所以,只要能用D触发器的地方,就不用latch。

一般会使用代码检查工具对代码中的latch进行排查,如果发现,一定要修改

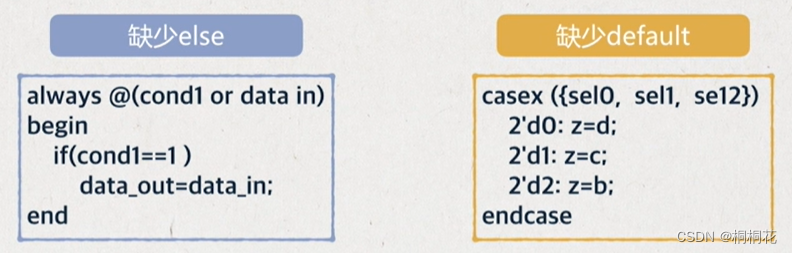

易引入latch 的途径

一般是使用不完备的条件判断语句。

防止产生非目的性Latch 的措施主要有:

- 使用完备的if..else 语句;

- 为每个输入条件设计输出操作,为case 语句设置default操作;

- 仔细检查综合器生成的报告, latch 会以 warning的形式报告。

full-case和parallel-Case 综合器指令

除电路结构设计本身外,还可以控制综合器,对电路结构进行指定 ,例如 full-case和parallel-Case 综合器指令。

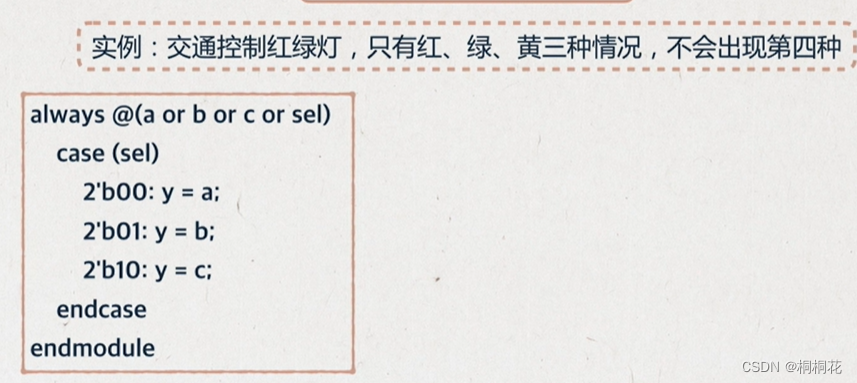

举例:

红绿灯有3种情况,需要2bit进行编码。2bit有4种情况,这意味着有一种情况是没有最终结果的。即出现分支赋值不完备情况。但是对于红绿灯,第四种情况不会出现。这样出现了综合器和现实的悖论。

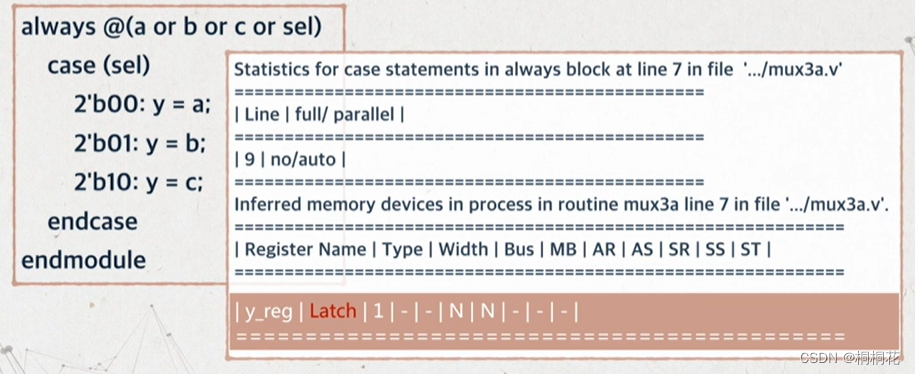

如果直接使用综合器对代码进行综合,就会产生一个latch。

综合报告中推断出有latch。

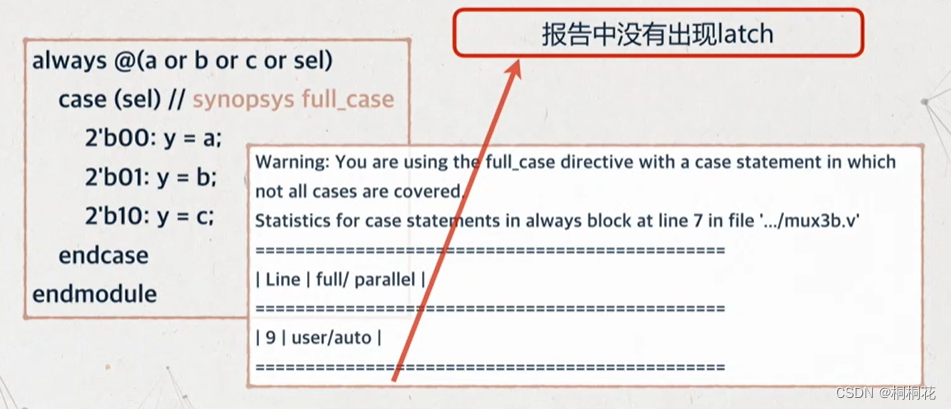

使用full case 原语,告诉综合器,当前case结构所列条件已完备

这样,综合报告中不会推断出有latch。

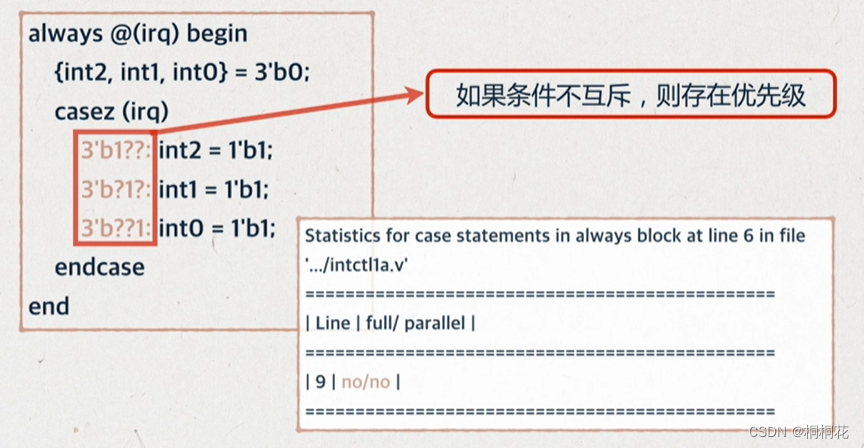

另一种情况:

如果分支条件不互斥,在综合过程中存在优先级。

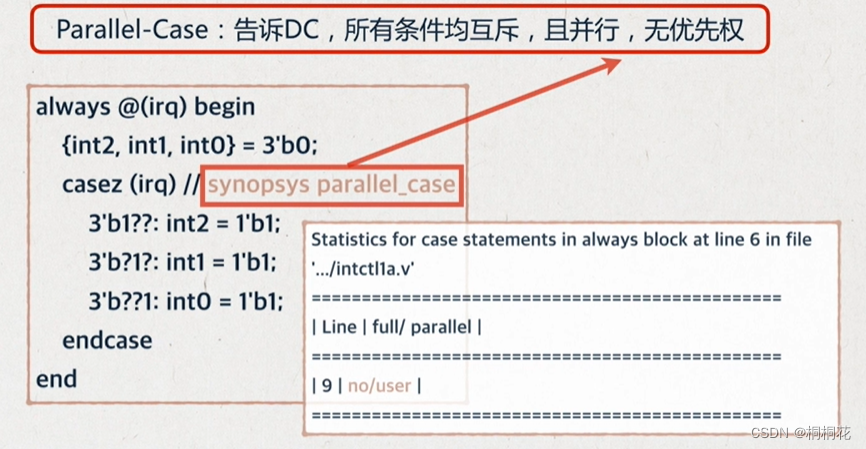

使用Parallel-Case:告诉DC,所有条件均互斥,且并行,无优先权

从下面报告可以看出,电路为用户指定的并行分支结构

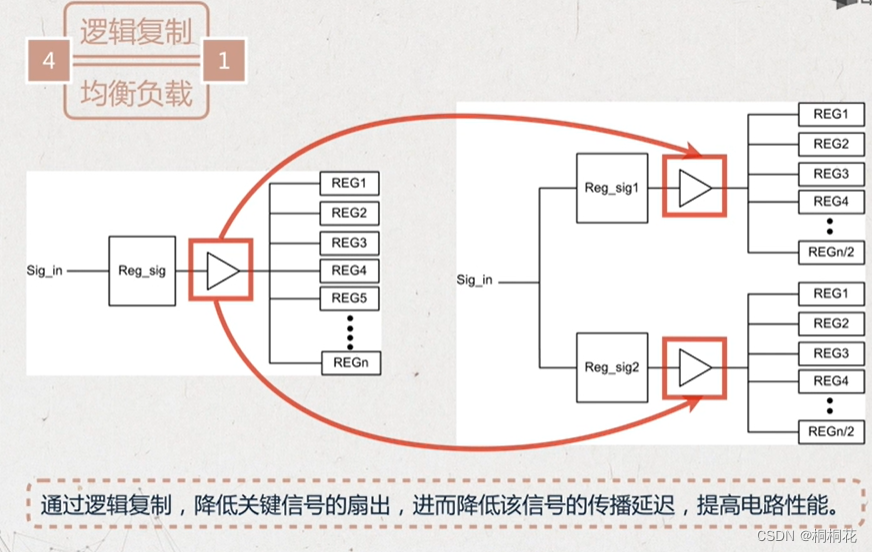

逻辑复制-均衡负载

在电路设计的过程中,如果发现某个电路的负载比较多,则可以通过逻辑复制,降低关键信号的扇出,进而降低该信号的传播延迟,提高电路性能。

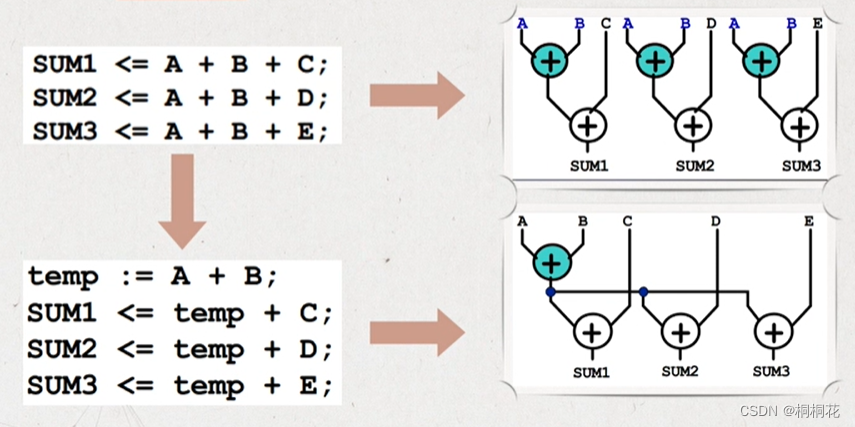

资源共享-减小面积

如果我们发现电路中存在较多的公共单元,也可以通过资源共享的方式,减小面积。

但是,一般来说,共享会导致性能下降,所以还要根据性能和面积进行取舍。

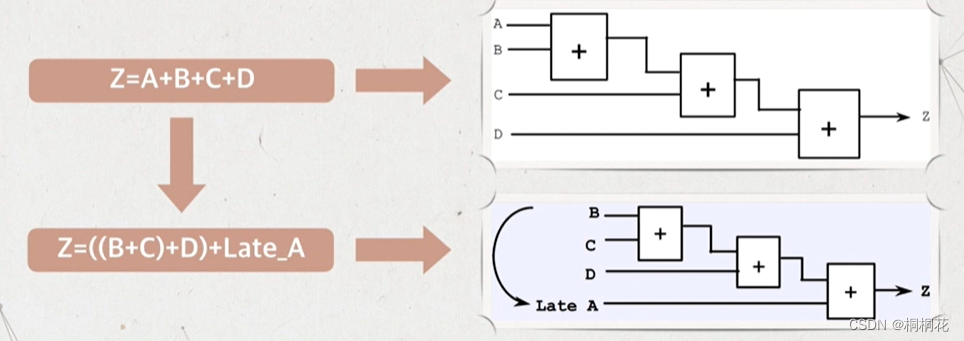

资源顺序重排-降低传播延迟

在设计电路的时候,可以根据数据的延迟,对这些资源进行顺序重排,降低传播延迟。

如图所示,A信号到来比较晚,我们就可以把它尽可能放到后面,隐藏其延迟。

尽可能使用always描述电路

在代码书写过程中,尽可能使用always描述电路, assign仅仅用来连线。

少用:?这种形式,因为这种形式通常难以阅读,且多层嵌套后很难被综合器解释。

四、可综合风格对代码的要求

1、完整的always敏感信号列表

所有的组合逻辑或锁存的always 结构必须有敏感信号列表。这个敏感信号列表必须包含所有的输入信号。

原因:

综合过程将产生一个取决于除敏感列表中所有其它值的结构,它将可能在行为仿真和门级仿真见产生潜在的失配。

2、每个always敏感信号列表对应一个时钟

在综合过程中,每个Verilog always 块敏感信号列表只能对应一个时钟。

原因:

这是将每一个过程限制在单一寄存器类型的要求,有利于逻辑综合和静态时序分析。

3、不允许 Wait声明和# delay声明。

Wait声明语句,不论是清楚还是含糊,都不能用于可综合设计。

原因:

从RTL级转换到gate级的综合工具一般都不支持Wait声明和# delay声明,为了有效的综合,这些语句应该避免。

在不需要进行综合的行为模块中,如测试模块、表示行为的虚拟器件模块中可以使用。

4、在时序电路中必须使用非阻塞赋值(<=),组合逻辑电路必须使用阻塞赋值(=),

这个一定要注意,严格按这个要求写。

5、分开异步逻辑与同步逻辑。

原因:

避免综合和静态时序时碰到问题,简化约束和编码难度。

例外:

不可应用于非综合模块中(例如:总线模块,总线监视器或是模拟模块)除非他们被设

计来综合仿真。

6、分开控制逻辑和存储器

建议控制逻辑和存储器逻辑分成独立的模块。

原因:

便于高层的存储器模块的使用和便于重新描述为不同的存储器类型。

通常来说,存储器是用memory compiler生成的,其综合方式与RTL代码不同,所以混在一起,不利用综合,不利于很方便地更换工艺库和平台。

五、总结

初学者通常会有一个误区︰

把verilog 代码当做了程序,把电路设计当成了编程。

那怎么样写好 verilog 呢?

牢记并理解可综合“四大法宝"所对应的硬件结构。

写前,确认电路指标是什么:性能?面积?根据指标再来设计电路。

硬件思维方式:

- 代码不再是一行行的代码而是—块一块的硬件模块

- 对所需实现的硬件电路"胸有成竹"。

电路优化的质量取决于代码的书序方式。请不要把电路性能优化寄希望于综合工具。

参考视频:中国大学MOOC 芯动力——硬件加速设计方法 (2.1节)

最后

以上就是顺心荷花最近收集整理的关于Verilog HDL可综合描述(高质量Verilog书写)一、VerilogHDL可综合概述二、常见可综合语法与硬件的映射关系 三、电路设计需要注意的基本事项 四、可综合风格对代码的要求五、总结的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复