一、实验目的

1. 学习掌握可综合 Verilog 语言进行 时序逻辑设计 的使用;

2. 学习测试模块的编写、综合和不同层次的仿真。

二、实验过程

一)时钟上升沿触发的D寄存器

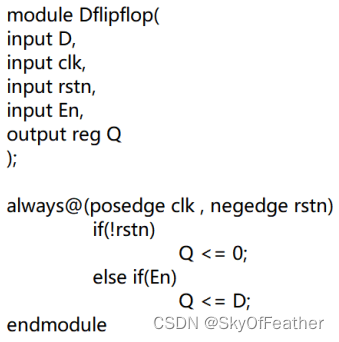

1) 源码

1. Dflipflop

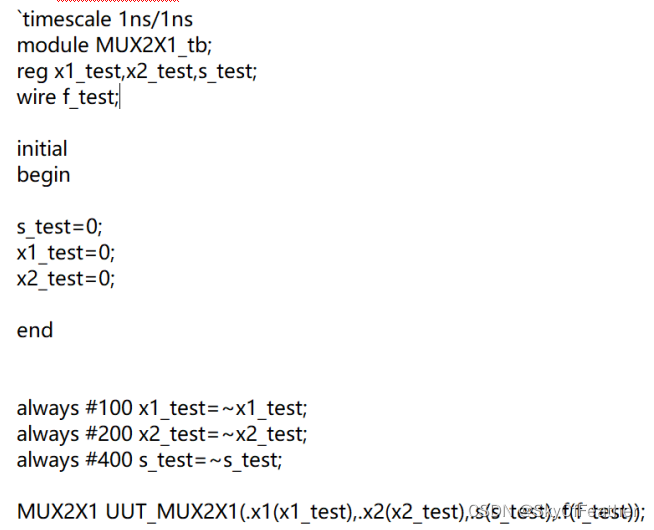

- Dflipflop_tb

- 生成波形与RTL图形

略

- 分析

D触发器是一种最简单的触发器,在触发边沿到来时,将输入端的值存入其中,并且这个值与当前存储的值无关。在两个有效的脉冲边沿之间,D的跳转不会影响触发器存储的值,但是在脉冲边沿到来之前,输入端D必须有足够的建立时间,保证信号稳定。

一个时钟信号的上升沿来临时,将此时的输入D传输给输出Q;在时钟信号的其他阶段内,输出均保持不变。

根据波形分析可知,满足此要求。

- 4bBit具有并行加载功能的移位寄存器

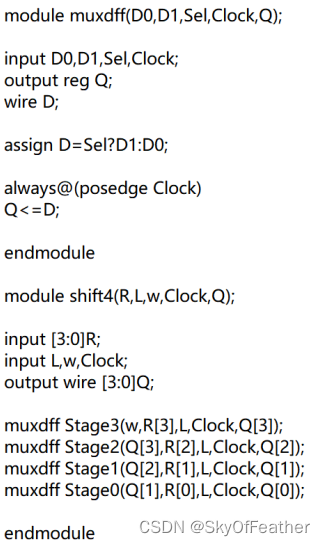

- 源码

- shift4

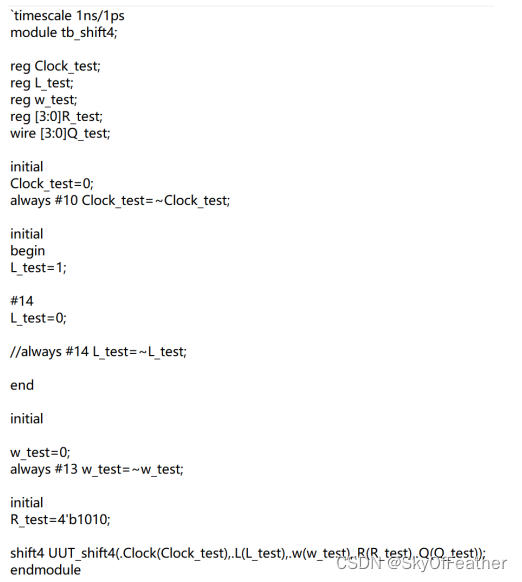

- shift4_tb

- 生成波形与RTL图形

略

- 分析

在数字电路中,移位寄存器是一种在若干相同时间脉冲下工作的以触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一些列位。实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

即:L为0时并行加载,数组R为加载时的输入。L为1时移位,数组Q右移一位,左端补当前变量w的值。

对比可知,模拟仿真无误。

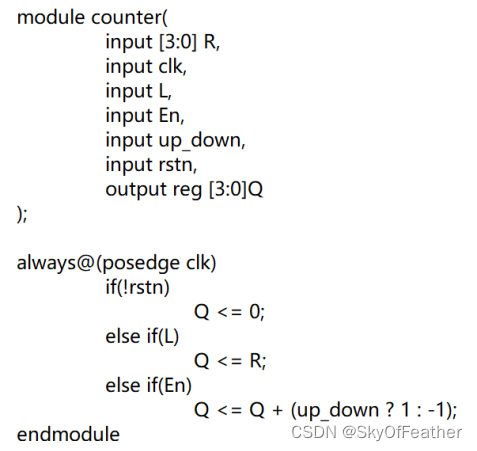

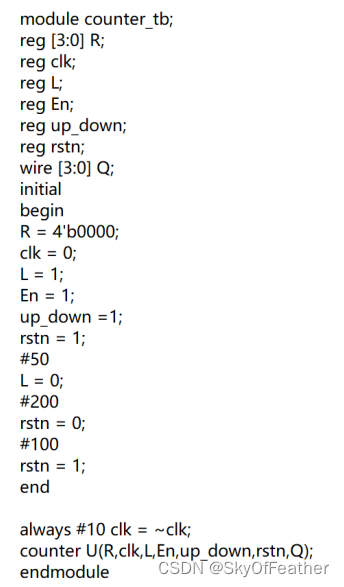

- 4 bit带复位功能的计数器

- 源码

- counter

- counter_tb

- 生成波形与RTL图形

略

- 分析

4 bit 带复位功能的计数器的基本功能,当时钟的上升沿到来时:若复位信号为0,表示复位信号有效,此时将数据R置为0;

Reset信号为1时重置。使能信号E为1时计数器工作,每当时钟上升沿到来时,输出Q加1.

分析波形可知,模拟仿真无误。电路能复位,能按预期增加计数,且能按预定溢出。

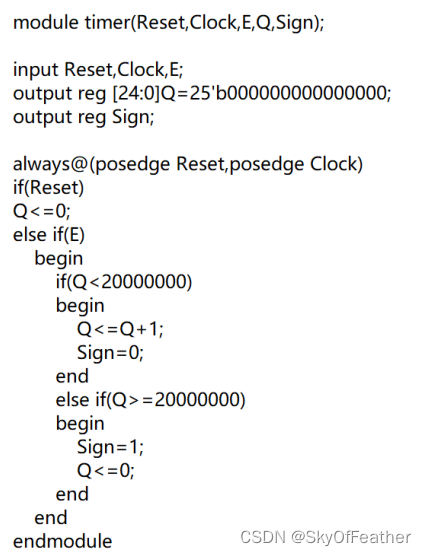

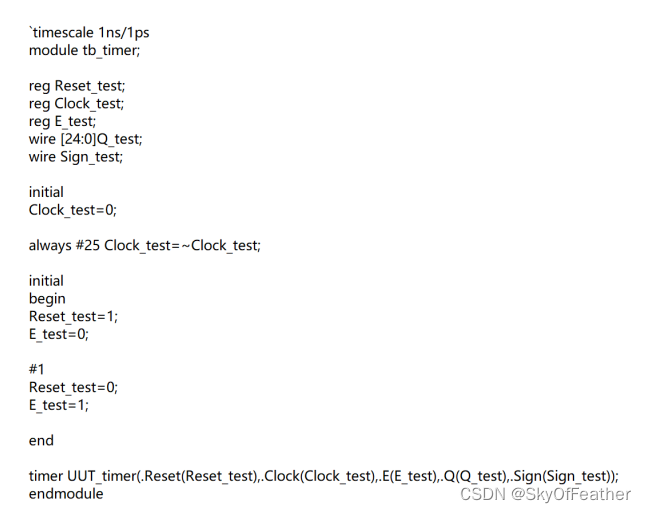

- 设计一个定时器(时钟频率20M,定时为1秒)

- 源码

- timer

- timer_tb

- 生成波形与RTL图形

略

- 分析

当根据时钟信号计数到一秒时,Sign信号由零变为1,从而实现计时。频率为20 MHz,即周期为50ns,也就是说每25ns,时钟反向一次;计数1s,表示每经过1s应该会出现一个输出信号。

- QuartusII软件基本使用步骤

- 编写verilog语言,由modelsim编译可知无误;

- 新建工程New project (注意工程名和设计文件的module名保持一致),选择和开发板一致的FPGA器件型号;

- Add to project,将源文件(即所编源码)添加到工程中;

- Start Compilation ,编译源文件;

- 使用Tool–>Netlist Viewers–>RTL Viewer工具查看电路图结构,是否和预期设计一致.

- 收获和心得

通过本次实验,我进一步加深了对Verilog语言的了解,学会初步使用QuartusII进行模拟,并且能够使用这种语言解决一些简单时序电路的构建和创造。这为今后数字逻辑与设计以及后续课程相关知识的学习奠定了基础,并且为更快掌握这些知识提供了便利。

一、实验目的

1. 学习掌握可综合 Verilog 语言进行 时序逻辑设计 的使用;

2. 学习测试模块的编写、综合和不同层次的仿真。

二、实验过程

一)时钟上升沿触发的D寄存器

1) 源码

1. Dflipflop

- Dflipflop_tb

- 生成波形与RTL图形

- 分析

D触发器是一种最简单的触发器,在触发边沿到来时,将输入端的值存入其中,并且这个值与当前存储的值无关。在两个有效的脉冲边沿之间,D的跳转不会影响触发器存储的值,但是在脉冲边沿到来之前,输入端D必须有足够的建立时间,保证信号稳定。

一个时钟信号的上升沿来临时,将此时的输入D传输给输出Q;在时钟信号的其他阶段内,输出均保持不变。

根据波形分析可知,满足此要求。

- 4bBit具有并行加载功能的移位寄存器

- 源码

- shift4

- shift4_tb

- 生成波形与RTL图形

- 分析

在数字电路中,移位寄存器是一种在若干相同时间脉冲下工作的以触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一些列位。实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

即:L为0时并行加载,数组R为加载时的输入。L为1时移位,数组Q右移一位,左端补当前变量w的值。

对比可知,模拟仿真无误。

- 4 bit带复位功能的计数器

- 源码

- counter

- counter_tb

- 生成波形与RTL图形

- 分析

4 bit 带复位功能的计数器的基本功能,当时钟的上升沿到来时:若复位信号为0,表示复位信号有效,此时将数据R置为0;

Reset信号为1时重置。使能信号E为1时计数器工作,每当时钟上升沿到来时,输出Q加1.

分析波形可知,模拟仿真无误。电路能复位,能按预期增加计数,且能按预定溢出。

- 设计一个定时器(时钟频率20M,定时为1秒)

- 源码

- timer

- timer_tb

- 生成波形与RTL图形

- 分析

当根据时钟信号计数到一秒时,Sign信号由零变为1,从而实现计时。频率为20 MHz,即周期为50ns,也就是说每25ns,时钟反向一次;计数1s,表示每经过1s应该会出现一个输出信号。

- QuartusII软件基本使用步骤

- 编写verilog语言,由modelsim编译可知无误;

- 新建工程New project (注意工程名和设计文件的module名保持一致),选择和开发板一致的FPGA器件型号;

- Add to project,将源文件(即所编源码)添加到工程中;

- Start Compilation ,编译源文件;

- 使用Tool–>Netlist Viewers–>RTL Viewer工具查看电路图结构,是否和预期设计一致.

- 收获和心得

通过本次实验,我进一步加深了对Verilog语言的了解,学会初步使用QuartusII进行模拟,并且能够使用这种语言解决一些简单时序电路的构建和创造。这为今后数字逻辑与设计以及后续课程相关知识的学习奠定了基础,并且为更快掌握这些知识提供了便利。

最后

以上就是纯真季节最近收集整理的关于数字逻辑与设计实验三 可综合时序逻辑电路实验的全部内容,更多相关数字逻辑与设计实验三内容请搜索靠谱客的其他文章。

发表评论 取消回复