3.RX模块设计

经过TX模块的设计分析之后,现在对RX是不是就不那么惧怕啦?我们还是按照老规矩来拆解这个模块:

逻辑关系:

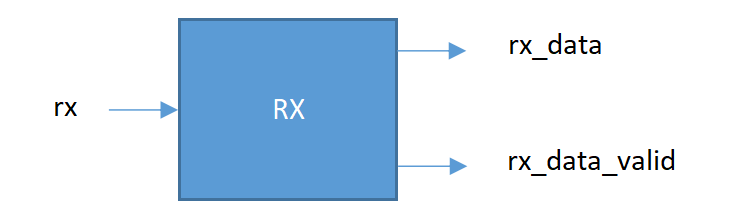

rx表示接收到的单bit数据(其实它就是一段持续的电流,忽高忽低,想象一下);rx_data表示生成的并行数据;rx_data_valid表示对rx_data进行使能。

设计思路:

(1)看输出,rx_data和rx_data_valid。而rx_data来源于rx,由单bit数据经过串行转并行生成,而rx_ready取决于当前状态,rx_data没有生成的时候置0,当rx_data生成后就置1。

问题1)怎么定义rx_data_valid?

解释:当rx_data生成后,就可以置1。怎么判定数据生成了呢?等第8位数据传完后,检测到当前状态为STOP,下个状态为IDLE,且baud_cnt_end为真时,rx_data_valid拉高,维持一个clk周期就拉低,保证这个数据可以被存起来就ok了。

问题2)怎么检测接收数据的下降沿呢?

最后

以上就是瘦瘦小蚂蚁最近收集整理的关于(4)UART应用设计及仿真验证3 —— RX模块设计的全部内容,更多相关(4)UART应用设计及仿真验证3内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复