在单片机中,时钟就如同人类的心脏一般,为单片机提供工作的节拍。时钟分为高速时钟和低速时钟,其中高速时钟直接或通过PLL倍频后充当系统时钟,系统时钟为单片机内绝大部分的外设及CPU提供工作节拍,低速时钟用于驱动独立看门狗和通过程序选择驱动RTC。

时钟的产生大体上分为两种,一种以单片机内部的信号发生器为时钟信号的,另一种是以外部信号为时钟信号的。

以单片机内部的信号发生器为时钟信号的产生时钟的方法又有两种。

第一种为单片机内部的信号发生器产生一段包含所有频率的信号,然后通过单片机内部的RC滤波器得到我们想要频率的信号,用该信号充当时钟信号。优点为不用外加外部晶体/陶瓷谐振器,降低成本和不用设计外部晶振电路。缺点为单片机内部集成的RC滤波器往往不够精准,在对时间或者时序要求严格的系统中往往不采用这种方式。

第二种为单片机内部的信号发生器产生一段包含所有频率的信号,然后通过单片机的SOC_IN引脚和OSC_OUT引脚之间外加的外部晶体/陶瓷谐振器,外部晶体/陶瓷谐振器只允许某一个特定频率的信号通过,所以单片机可以得到一个极其精准的某个频率的信号充当时钟信号。本系统也是使用这种方式来获取时钟信号的。

以外部信号为时钟信号的方式只有一种。

通常为将具有50%占空比的外部时钟信号(方波、正弦波或三角波)连到OSC32_IN引脚,同时保证OSC32_OUT引脚悬空。用户可通过设置在时钟控制寄存器中的HSEBYP和HSEON位来选择这一模式。

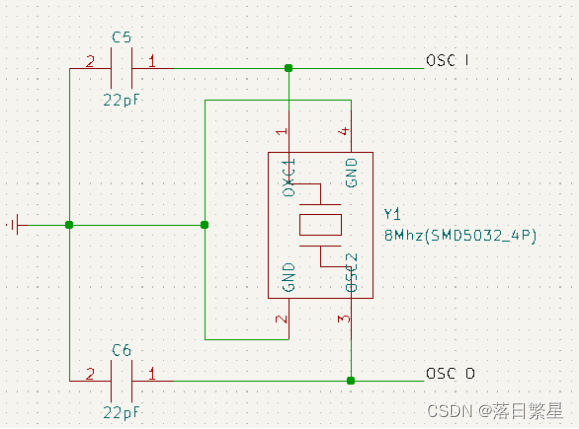

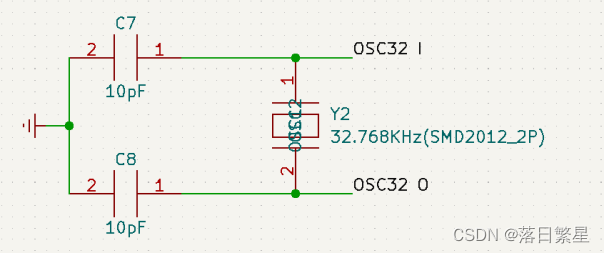

本系统采用外接晶振的方式来提供时钟信号,其中连接高速时钟外部晶振的引脚OSC I为PD0,OSC O为PD1,连接低速时钟外部晶振的引脚OSC32 I为PC14,OSC32 O为PC15。晶振电路如图3.3,图3.4所示。

图3.3 高速时钟晶振电路

图3.4 低速时钟外部晶振电路

高速时钟外部晶振本系统采用8MHz的晶振,经过PLL倍频后的系统时钟频率为72M。低速时钟外部晶振本系统采用32.768KHz的晶振。同时连接电容的目的为滤波,让信号输出更稳定,电容大小是根据选择的外部晶振的产品手册的说明来选择的,一般为10~40pF,本电路中高速时钟外部晶振采用的是22pF,低速时钟外部晶振采用的是10pF。

最后

以上就是高挑抽屉最近收集整理的关于晶振电路设计的全部内容,更多相关晶振电路设计内容请搜索靠谱客的其他文章。

发表评论 取消回复