一、Boundary Scan Register

-

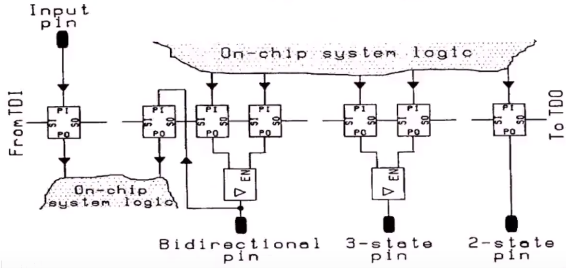

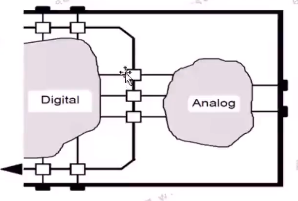

scan path 沿着IC边界,在内部逻辑之外,

-

Boundary Scan technique to ctrl and to observe each IO siganl anround IC boundary using testing principles

-

between core logic and pad cell of IC

BS紧贴内部IO,紧贴IO和内部逻辑之间(具体非门,门等实现逻辑)

测试原则类似Scan测试。

-

PAD有三种:

2-state pin(0,1) input output (PI,PO functional 接口)SI,SO(scan接口)

从内部逻辑到pad之间断开,然后插入Boundary scan 单元,分别连接到PI,PO3-state pin(带buffer的enable的pin的。input output)

需要两个路径,(pad有三个端口)两个输入信号,和一个输出,在两个路径断开,插入两个单元Cell,分别连接到PI,PObidi pin (常见的inout pin ,带enable 的output ,可输入,输出)

-

核心:放在PAD和内部逻辑之间,两个中间没有逻辑(只有一根线,pad在内部的连接关系,在线上断开,放入BS cell,Boundary cell和逻辑之间不能有其他逻辑组成)

-

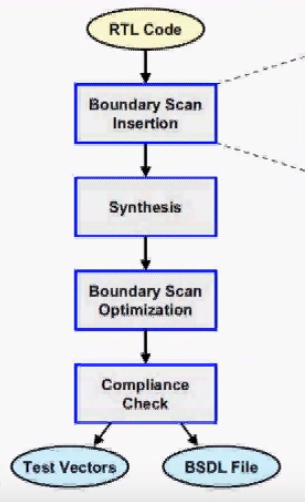

BOundary Scan flow

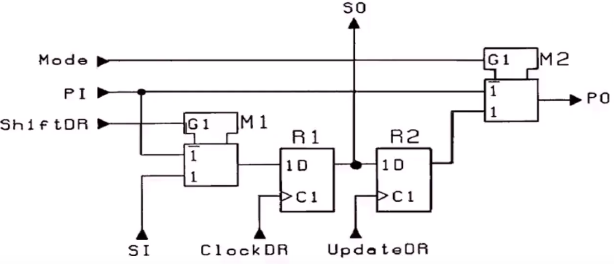

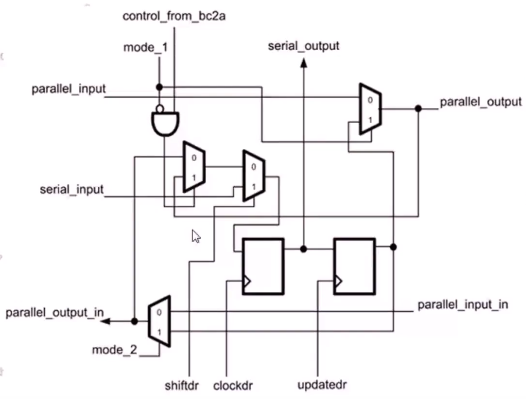

二、 Boundary Scan Cell(通用CELL)

-

the mode input should be ctrlled according to the type of pin connected to the cell (input, output,etc) and the specific instruction selected.

Support SAMPLE,PRELOAD,EXTEST,and INTEST,

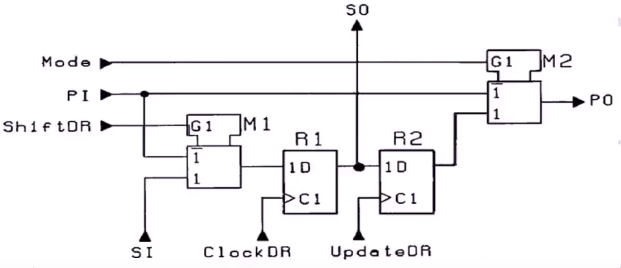

结构和Scan很类似,但是多了一个MUX。 -

SAMPLE:通过capture动作来完成

PRELOAD:shift动作,先shift,在upload

EXTEST:针对外面的测试完成的动作,所有的PI不能work,针对PO,对output 的hold register 控制

INTEST:input 由hold register 控制,不是由pad,hold register来替代pad

-

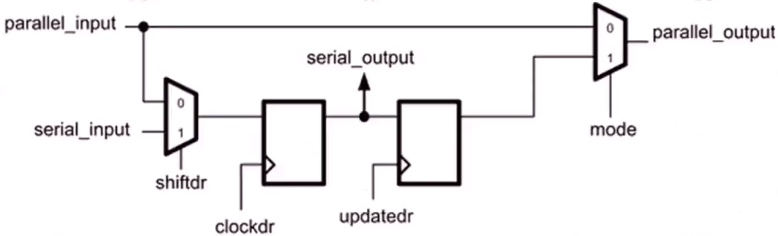

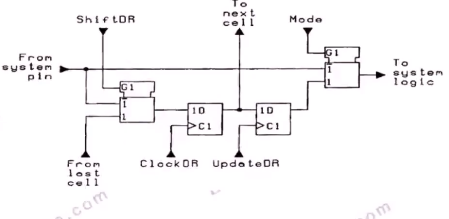

Shift DR MUX

SI 和PI(data input)

Clock DR:Shift DR capture DR两个状态

在shift DR状态下(ShiftDR = 1)的时候,通过SI 和SO端口和其他的boundary scan cell里的其他 shift register 串联起来,完成数据的输入。

在非shiift DR状态(ShiftDR = 0)下,Clock DR 可以在capture的状态下,把PI的值capture 到系统中 -

Update DR:把shift DR的状态转到R2 寄存器内。

PI从PAD过来,PO输出到functional逻辑中。

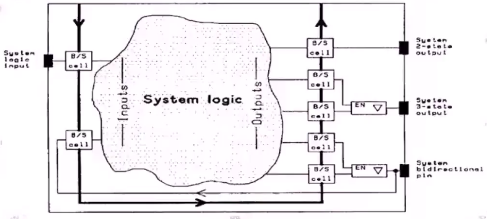

三、 Boundary Scan Cell Placement

- 一个或多个 boundary scan 单元可以在每一个SOC系统逻辑输入或者输出。

- 模拟电路中:在系统逻辑和模拟逻辑之间可以放置boundary scan

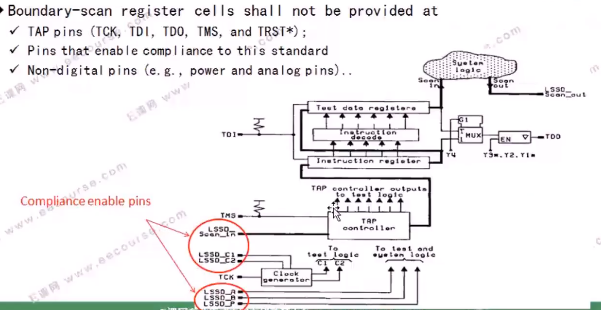

- 不能放的位置:

TAP pin

compliance pin (自定义的方式完成JTAP的,类似的,对JTAG逻辑操作)

非数字信号pin (power pin,模拟信号等)

有针对IEEE 1149.6 针对ac信号的pin(差分信号)

IEEE 1149.1 针对数字信号

- 基本要求:

保证在正常模式下,functional 路劲是正常工作。

boundary scan register和 pin 之间无逻辑

pin脚没有的情况下,

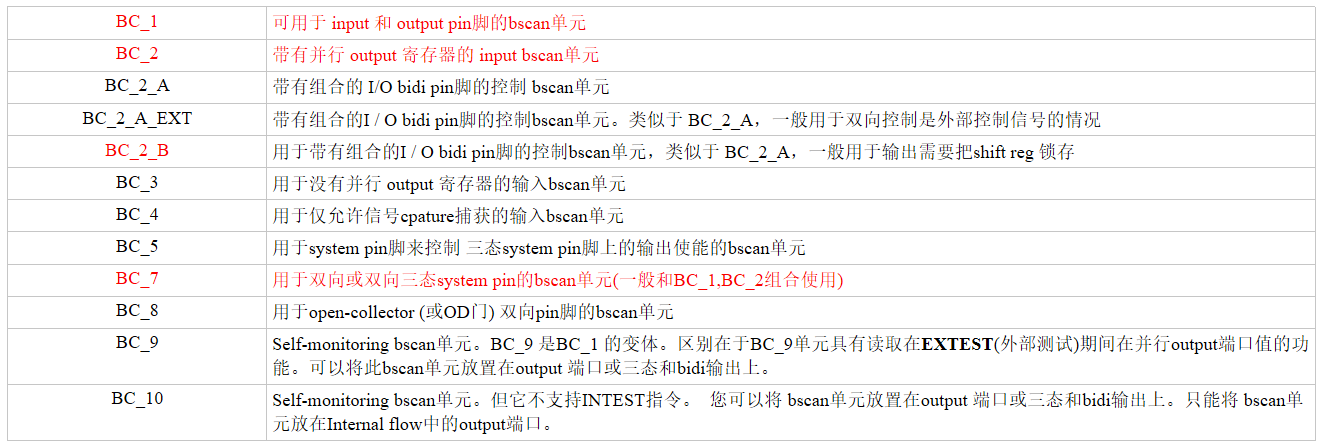

四、 Boundary Scan Cell Type

-

Boundary Scan Register 要求:

替换芯片的输出和输入状态;

控制系统逻辑输入或者观测系统逻辑输出 -

通用类型:

可以在此基础上加一些MUX和mode衍生出很多类型(这个是JTAG组织的员工没事干,开发这么多不同功能的单元,其实可以根据自己的要求来选择) -

对于不同的输入和输出要求,有很多种不同的Boundary Scan Cell 类型:| BC_1 | BC_2 | BC_2_A | BC_2_A_EXT | BC_2_B | BC_3 | BC_4 | BC_5 |BC_7 | BC_7_LOW | BC_8 | BC_9 | BC_10|

五、常用的Cell就三个单元。BC_1、 BC_2、 BC_7

-

BC_1 Cell for OUTPUT/INPUT:

parallel input : function input

parallel output :

serial input: SI

serial output: SO

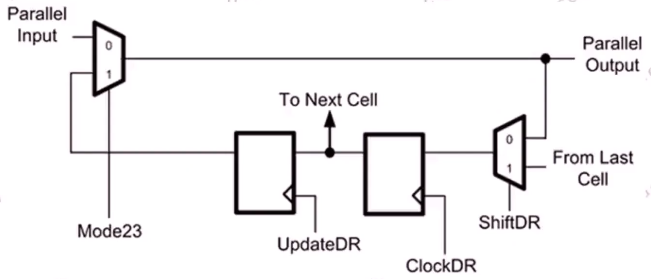

parallel input 到 parallel output 是function路径,将function 路径断开接入cell单元,通过MUX mode信号来选择路径,进入模式mode转换中,mode通常连接在指令译码选择器出来控制信号。

update DR 是标准的clockmode: mode信号通过指令code,decode出来的译码信号接入mode。如果寄存器有很多指令,都需要bypass function 路径,就可以在mode端或起来。

注意:

BC_1可以作为我们的Input 也可以作为Output。

INPUT:

从system pin 进来,从 system logic 出去,bypass。OUTPUT:

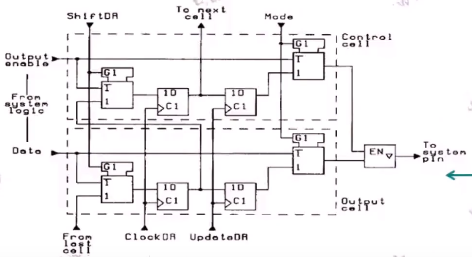

三态output组合:

system logic 系统输出 —> IO的enable端(bypass路径)

Shift DR, Clock DR, Update DR, Mode可以共享 -

BC_2 for INPUT and Control

An input cell with parallel output register

parallel input 从pad中进来,经过mode选择。

BC_1不同的是:Update的输出端,Parellel input 和output调换顺序。 -

BC_7 for INOUT **

好处:只有两个寄存器,但缺少output enable** 控制,把input 和output merge起来

所以,一般会和BC_1或者BC_2配合使用,BC_1专门用来output enable 的控制 加上BC_7 cell的控制。好处:SHift Register数减少,减少了面积,增加MUX来减少FF数量。

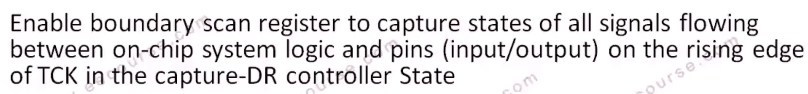

六、 Boundary Scan Register Timing

所有状态都由TCK上升沿来完成。

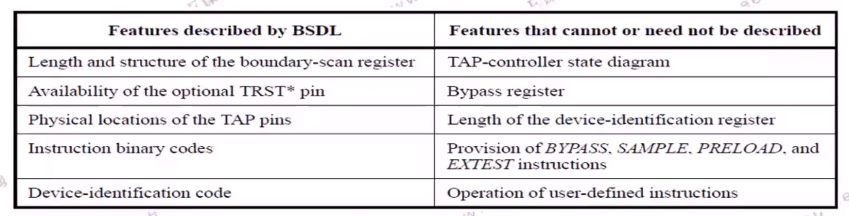

七、BSDL(Boundary Scan Description Language)

不具有通用性,不可用于仿真,基于VHDL。

最后

以上就是懦弱西装最近收集整理的关于SOC——Boundary scan介绍(二)的全部内容,更多相关SOC——Boundary内容请搜索靠谱客的其他文章。

发表评论 取消回复