SOC——Boundary scan模块的RTL代码设计(三)

Boundary Scan Cell Types

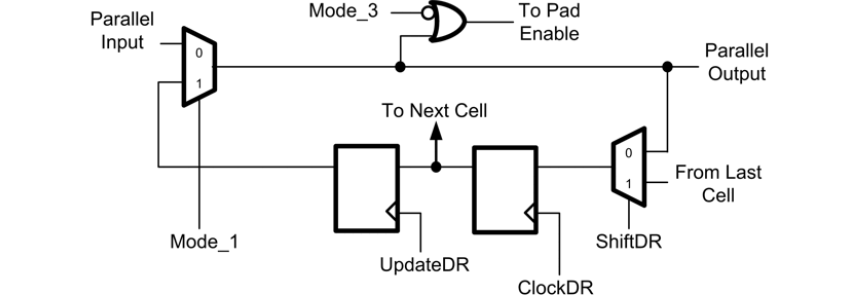

BC_2_B Type Cell

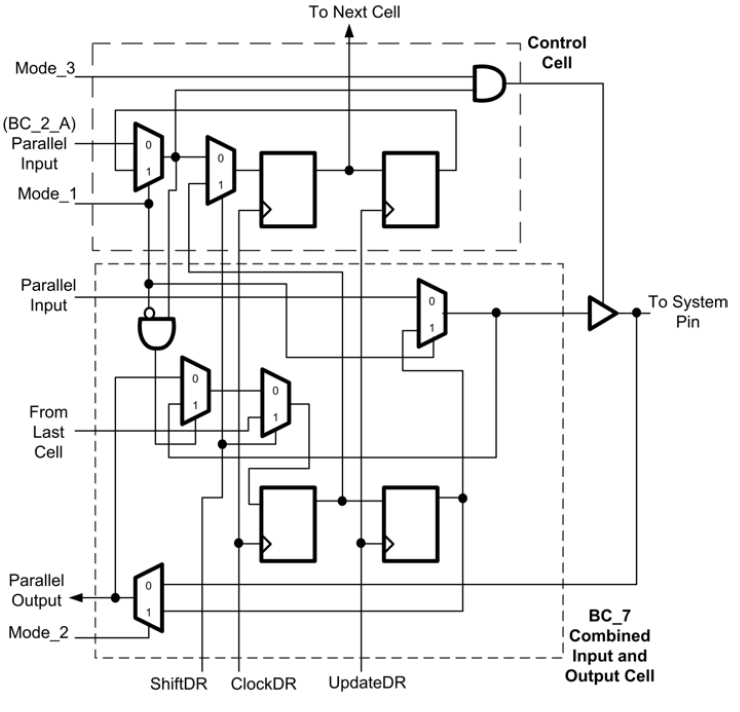

BC_7 Type Cell Shown with BC_2_A Control Cell

其总的代码描述如下,包括一个bc_7 单元和bc_2_a单元:

module boundary_scan (

//

jtg_shiftdr,

jtg_clockdr_in,

jtg_updatedr,

jtg_trst_n,

jtg_mode_1,

jtg_mode_2,

jtg_mode_3,

serial_input,

outen_from_core,

dataout_from_core,

datain_from_pad,

jtg_clock_out,

serial_output,

outen_to_pad,

dataout_to_pad,

datain_to_core

);

input jtg_shiftdr;

input jtg_clockdr_in;

input jtg_updatedr;

input jtg_trst_n;

input jtg_mode_1;

input jtg_mode_2;

input jtg_mode_3;

input serial_input;

input outen_from_core;

input dataout_from_core;

input datain_from_pad;

output jtg_clockdr_out;

output serial_output;

output outen_to_pad;

output dataout_to_pad;

output datain_to_core;

wire serial_output_inout_enable;

wire dummy_inout_enable_control_to_bc7;

wire serial_clockdr;

bc_2_b bsc_dummy_inout_enable(

.shiftdr (jtg_shiftdr),

.clockdr_in (serial_clockdr),

.clockdr_out (jtg_clockdr_out),

.updatedr (jtg_updatedr),

.trst_n (jtg_trst_n),

.serial_input (serial_input), //.serial_input (serial_output_inout_enable),

.parallel_input (outen_from_core),

.mode_1 (jtg_mode_1),

.mode_3 (jtg_mode_3),

.serial_output (serial_output_inout_enable), //.serial_output (serial_output),

.control_to_bc7 (dummy_inout_enable_control_to_bc7),

.parallel_output (outen_to_pad)

);

bc_7 bsc_dummy_inout_output(

.control_from_bc2a (dummy_inout_enable_control_to_bc7),

.shiftdr (jtg_shiftdr),

.clockdr_in (jtg_clockdr_in),

.clockdr_out (serial_clockdr),

.updatedr (jtg_updatedr),

.trst_n (jtg_trst_n),

.parallel_input (dataout_from_core),

.serial_input (serial_output_inout_enable), //.serial_input (serial_input),

.mode_1 (jtg_mode_1),

.mode_2 (jtg_mode_2),

.parallel_input_in (datain_from_pad),

.parallel_output (dataout_to_pad),

.serial_output (serial_output), //.serial_output (serial_output_inout_enable),

.parallel_output_in (datain_to_core)

);

endmodule

bc_2_b的cell单元的RTL code描述:

///

module bc_2_b(

///

shiftdr,

clockdr_in,

clockdr_out,

updatedr,

trst_n,

serial_input,

parallel_input,

mode_1,

mode_3,

serial_output,

control_to_bc7,

parallel_output

);

input shiftdr;

input clockdr_in;

output clockdr_out;

input updatedr;

input trst_n;

input serial_input;

input parallel_input;

input mode_1;

input mode_3;

output serial_output;

output control_to_bc7;

output parallel_output;

reg serial_output_b;

reg latch_out;

wire shift_reg_in;

wire control_to_bc7_b;

macro_buffer U_2nd_clockdr_buf (.A(clockdr_in),.Z(clockdr_out));

assign control_to_bc7_b = (mode_1 == 1'b0) ? parallel_input :

(mode_1 == 1'b1) ? latch_out:

1'bx;

assign shift_reg_in = (shiftdr == 1'b0) ? control_to_bc7_b :

(shiftdr == 1'b1) ? serial_input:

1'bx;

assign parallel_output = control_to_bc7_b | ~mode_3;

assign control_to_bc7 = control_to_bc7_b;

always @ (posedge clockdr_in or negedge trst_n) begin

if (~trst_n)

serial_output_b <= 1'b0;

else

serial_output_b <= shift_reg_in;

end

always @ (posedge updatedr or negedge trst_n) begin

if (~trst_n)

latch_out <= 1'b0;

else

latch_out <= serial_output_b;

end

assign serial_output = serial_output_b;

endmodule

bc_7的cell单元描述如下:

///

modeule bc_7(

///

control_from_bc2a,

shiftdr,

clockdr_in,

clockdr_out,

updatedr,

trst_n,

parallel_input,

serial_input,

mode_1,

mode_2,

parallel_input_in,

parallel_output,

serial_output,

parallel_output_in

);

input control_from_bc2a;

input shiftdr;

input clockdr_in;

output clockdr_out;

input updatedr;

input trst_n;

input parallel_input;

input serial_input;

input mode_1;

input mode_2;

input parallel_input_in;

output parallel_output;

output serial_output;

output parallel_output_in;

reg latch_out;

reg serial_output_b;

wire in_or_out_ctrl;

wire in_or_out;

wire shift_reg_in;

wire parallel_output_b;

wire parallel_output_in_b;

macro_buffer U_1st_clockdr_buf (.A(clockdr_in),.Z(clockdr_out));

assign in_or_out_ctrl = ~mode_1 & control_from_bc2a;

assign in_or_out = (in_or_out_ctrl == 1'b0) ? parallel_output_in_b:

(in_or_out_ctrl == 1'b1) ? parallel_output_b:

1b'x;

assign shift_reg_in = (shiftdr == 1'b0) ? in_or_out:

(shiftdr == 1'b1) ? serial_input:

1b'x;

assign parallel_output_in_b = (mode_2 == 1'b0) ? parallel_input_in:

(mode_2 == 1'b1) ? latch_out:

1'b1;

assign parallel_output_b = (mode_1 == 1'b0) ? parallel_input:

(mode_1 == 1'b1) ? latch_out:

1'b1;

assign parallel_output = parallel_output_b;

assign parallel_output_in = parallel_output_in_b;

always @ (posedge clockdr_in or negedge trst_n) begin

if (~trst_n)

serial_output_b <= 1'b0;

else

serial_output_b <= shift_reg_in;

end

always @ (posedge updatedr or ne trst_n) begin

if (~trst_n)

latch_out <= 1'b0;

else

latch_out <= serial_output_b;

end

assign serial_output = serial_output_b;

endmodule

最后

以上就是无奈指甲油最近收集整理的关于SOC——Boundary scan模块的RTL代码设计(三)的全部内容,更多相关SOC——Boundary内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复