在很大规模的IC设计中,往往会有一些各种各样的bug出现,不论是在前期design的过程,还是在post silicon流片回来chip的flaw,都会导致chip的功能的失败,时钟频率无法达到期望频率。

所以,在超大规模集成电路的设计中,DFT就是一门非常重要的方法学,在消费者手中,往往不知道他们的存在,但是在IC工程师眼中,DFT往往会是一个救命的稻草,让我们在芯片出问题的时候,可以知道从哪下手,找到bug的根源。

在DFT中,有几种功能,是常常需要用到的。

1. JTAG/1149.1 :几乎所有的公司都会用JTAG来做DFT的验证,在ATE平台上,通过JTAG接口,将pattern向量通过JTAG接口打入chip,然后驱动chip内部的逻辑,并对chip进行验证。

2. Boundary Scan:DFT书中的定义boundary scan的方法是将一个模块所有的PAD接口全部串到chain上,做一个scan,来检测每个pad是否都可以正常工作。

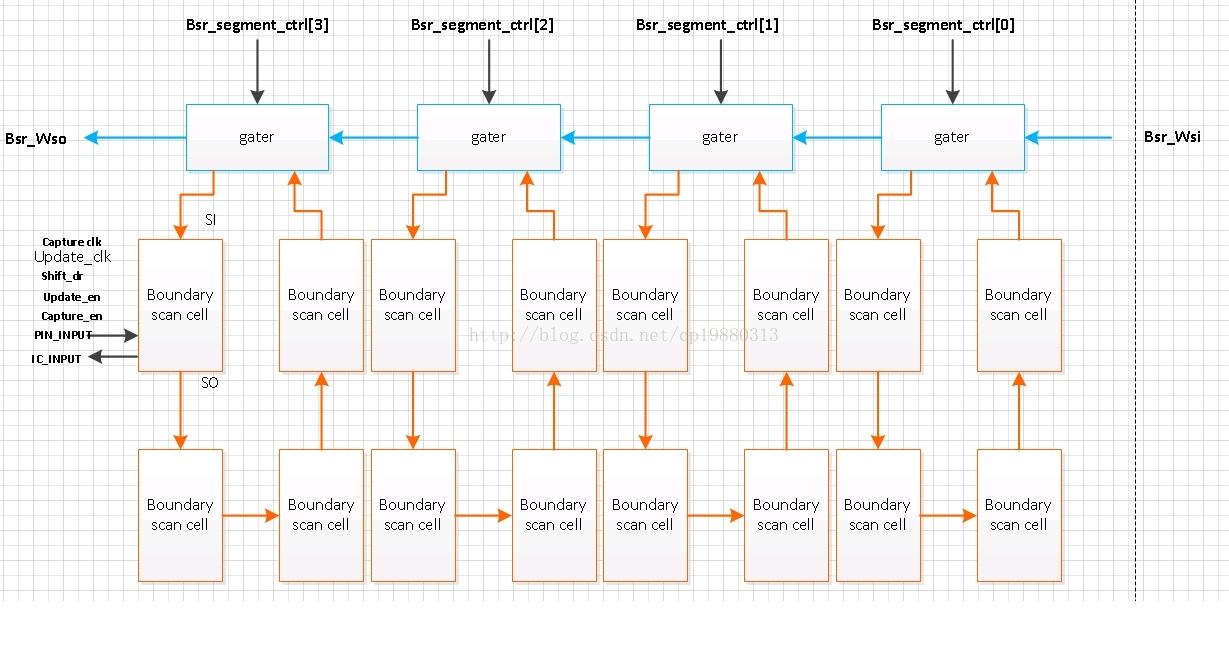

当pad很多的chip,往往不会只有一条scan chain,往往chip面积比较大的情况下,pad分布在各个不同的位置,如果做成一条chain,会导致timing violation,并且耗时比较久,debug起来比较困难,PD的布线也会有很大的问题。

而做成多条scan chain是一个比较好的选择,将所有的pad分成几个segment,每次通过寄存器来控制打开哪个segment,测试对应的一条chain。

最后

以上就是难过过客最近收集整理的关于IC 设计中DFT的Boundary Scan功能的全部内容,更多相关IC内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复