学习记录(持续改进):异步和同步的区别,以及各自的优缺点,以及异步复位和同步释放的实现方法

一.异步

独立于时钟控制的复位控制端。(就是 rst, res_n,这些在always@的敏感信号表里) 这样在任何时刻只要复位信号一来,输出直接清0。

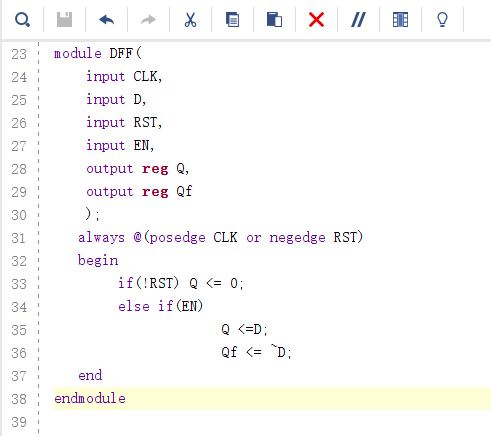

异步清零D触发器Verilog描述

异步复位优缺点:

优点:

a、大多数目标器件库的 DFF 都有异步复位端口,那么该触发器的复位端口就不需要额外的组合逻辑,这样就可以节省资源;

b、设计相对简单;

c、异步复位信号识别方便(电路在任何情况下都能复位而不管是否有时钟出现)。

缺点:

a、最大的问题在于它属于异步逻辑,问题出现在复位释放时,而不是有效时,如果复位释放接近时钟有效沿,则触发器的输出可能进入亚稳态(此时 clk 检测到的 rst_n 的状态就会是一个亚稳态,即是0是1是不确定的),从而导致复位失败。

b、可能因为噪声或者毛刺造成虚假复位信号(比如以前的游戏机玩到一半突然复位)(注意:时钟端口、清零和置位端口对毛刺信号十分敏感,任何一点毛刺都可能会使系统出错,因此判断逻辑电路中是否存在冒险以及如何避免冒险是设计人员必须要考虑的问题);

c、静态定时分析比较困难。

d、对于 DFT (Design For Test可测性设计)设计,如果复位信号不是直接来自于 I/O 引脚,在 DFT 扫描和测试时,复位信号必须被禁止,因此需要额外的同步电路。

二.同步

控制信号只有在时钟边沿到来时才起作用。(控制信号不在always 敏感信号表中) 控制信号来了,不会马上清0,要等到下一个时钟信号到来,才会清零。

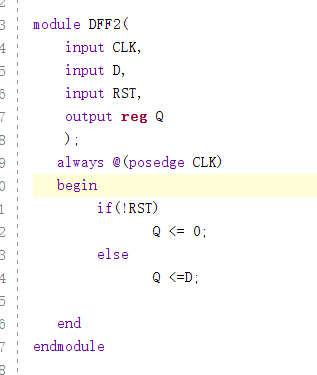

同步清零D触发器Verilog描述

同步电路优缺点:

优点:

a、有利于仿真器的仿真;

b、可以使所设计的系统成为 100% 的同步时序电路,有利于时序分析,而且可综合出较高的 Fmax;

c、由于只在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的复位毛刺。

缺点:

a、复位信号的有效时长必须大于时钟周期,才能真正被系统识别并完成复位任务。同时还要考虑诸如 clk skew 、组合逻辑路径延时 、复位延时等因素(所以复位信号有时需要脉冲展宽,用以保证时钟有效期间有足够的复位宽度);

b、由于大多数的逻辑器件的目标库内的 DFF 都只有异步复位端口,所以,倘若采用同步复位的话,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会一方面额外增加FPGA内部的逻辑资源,另一方面也增加了相应的组合逻辑门时延。

3.异步复位和同步释放实现方法(努力弄懂中!)

代码实现:(Altera 官方资料)

module reset_best(clk,asyn_reset,syn_reset);

input clk;

input asyn_reset;

output syn_reset;

reg rst_s1;

reg rst_s2;

always @( posedge clk ,posedge asyn_reset)

begin

if(asyn_reset)

begin

rst_s1<=1'b0;

rst_s2<=1'b0;

end

else

begin

rst_s1<=1'b1;

rst_s2<=rst_s1;

end

end

assign syn_reset=rst_s2;

endmodule

最后

以上就是羞涩灯泡最近收集整理的关于学习记录(持续学习中):异步清零和同步清零区别和各自优缺点。 异步复位和同步释放实现方法。的全部内容,更多相关学习记录(持续学习中):异步清零和同步清零区别和各自优缺点。内容请搜索靠谱客的其他文章。

发表评论 取消回复