异步和同步的概念简单的说就是时钟信号是不是同一个,但是异步的下一级时钟信号到底是接上一级的正输出还是反输出,一定要接上一级的输出吗?这些问题一直困扰着我对异步的理解。回过看才发现我看的都是同一个博主的文章,不得不说这些文章思路真的很清晰。以下便是我基于这位博主文章的三进制计数器的学习记录。

同步三进制加法计数器:

经典同步时序逻辑电路分析汇总(第一道)(同步三进制加法计数器)

因为这篇文章是电路分析,所以分析流程与设计的流程是反着的,但整体没影响。总的来说就不用分析时钟信号,直接按照套路来:画出电路的状态转换图和时序图——写出电路的驱动方程、状态方程和输出方程——连接电路

异步三进制加法计数器:

首先我是先学习了博主的这两篇文章:

异步时序逻辑电路设计方法(统一使用上升沿触发的触发器)

异步十二进制加法计数器(统一使用上升沿触发的D触发器)设计

其实看这两篇文章并跟着分析一遍完全就可以理解异步。可当我用这种方法来设计异步三进制加法器时发现出现了问题。

按照文章中的的分析办法,Q2从1变为0的那次跳变是发生在时钟的上升沿且Q1并没有发生改变,因此并不能用Q1来作为Q2的时钟信号,那这样Q2就得与Q1用同一时钟,就成了同步了。

为什么会出现这样的情况,经过分析,不难发现问题就出在Q1应该在Q2的那个从1变为0的跳变时有个下降沿(能是上升沿吗?我认为不能,因为上次Q2的跳变就发生在Q1的下降沿)

那为什么会少一个下降沿(准确的说应该时上升沿)。

因为它是奇数次模值计数。导致最后一个计数回到起始状态时它会有两个连续的低电平状态。

所以想通过这样方法是没办法让它三个状态的循环。

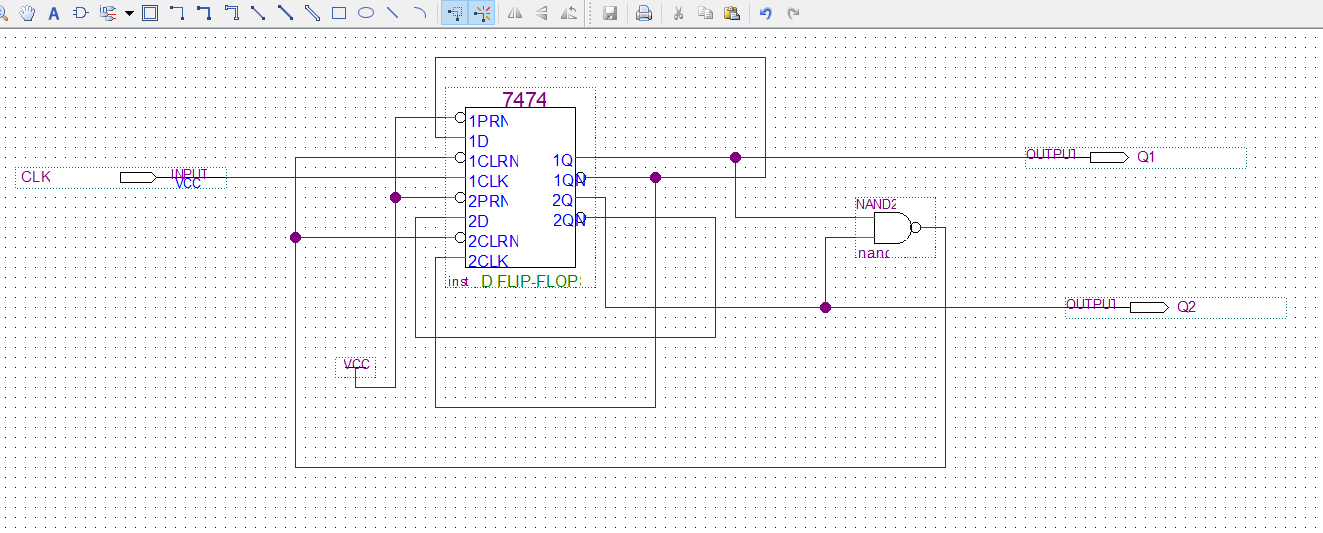

再次经过分析后(哈哈哈)为什么我不能用后面74163、161那一系列的清零的方法呢,到3的时候就让它清零。经过实验仿真也证明这种方法是可行的。

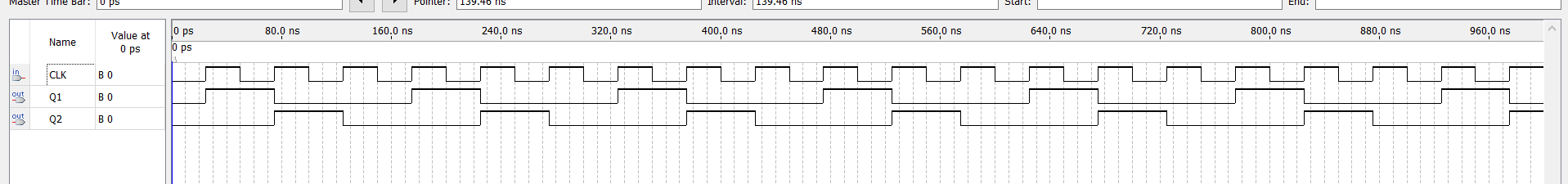

下面是电路图和仿真结果

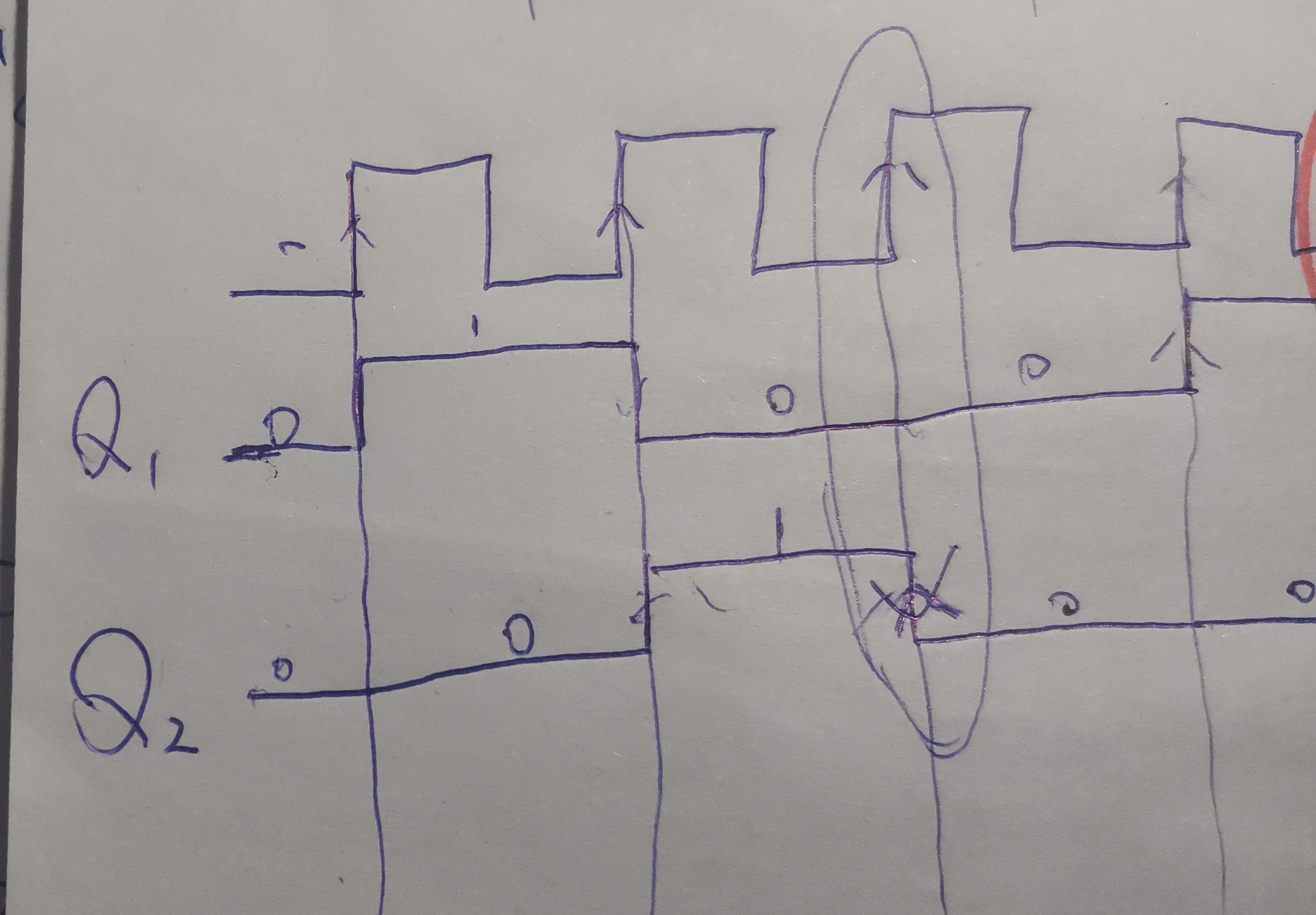

电路连接整体思路就是构造一个异步四进制计数器,然后将Q1反和Q2正与非连起来接到两个清零信号。

小经验:如果用的是时钟的上升沿触发,异步连接时都是上级的Q反接下一级的时钟

最后

以上就是超帅鼠标最近收集整理的关于7474触发器 异步三进制加法计数器的全部内容,更多相关7474触发器内容请搜索靠谱客的其他文章。

发表评论 取消回复