用verilog实现带进位的4进制计数器,不知道怎么写关于进位的计数器没关系,你一定见到过verilog写全加器,对的,进位位是单独的output,没错,博主脑子不够灵光,一开始在这里卡住了。

module JSQ (

clk,

rst,

in_ena,

rst,

in_ena,

cnt,

carry_in

carry_in

);

input clk;

input rst;

input in_ena;

input rst;

input in_ena;

output [3:0]cnt;

output carry_in;

output carry_in;

reg [3:0]cnt;

reg carry_in;

always@(posedge clk or negedge rst)

begin

if(!rst)

cnt<= 4'b0;

else if (in_ena && cnt==4'b100)

cnt<= 4'b0;

else

cnt<= cnt+1'b1;

end

always @(posedge clk or negedge rst)

begin

if(!rst)

carry_in<=4'b0;

else if(in_ena && cnt==4'b100)

carry_in<= 1;

else

carry_in <= 0;

end

begin

if(!rst)

cnt<= 4'b0;

else if (in_ena && cnt==4'b100)

cnt<= 4'b0;

else

cnt<= cnt+1'b1;

end

always @(posedge clk or negedge rst)

begin

if(!rst)

carry_in<=4'b0;

else if(in_ena && cnt==4'b100)

carry_in<= 1;

else

carry_in <= 0;

end

endmodule

就是这么简单,是我想的太复杂了

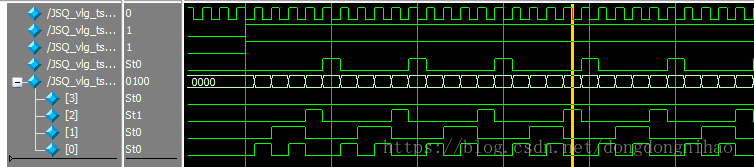

下面是仿真结果:

最后

以上就是温暖小丸子最近收集整理的关于verilog实现带进位的4进制计数器的全部内容,更多相关verilog实现带进位内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复