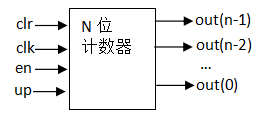

目的:设计一个带使能输入的同步清0的增1/减1的通用(带类属说明)的计数器(8位)。

本程序使用了类属说明语句,可以通过改变类属说明语句中变量的大小进而改变内部电路结构和规模。

程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity counter is

generic(n : integer := 8); --generic类属说明,确定计数器的位数

port(

--clr-清零,clk-时钟信号,en-使能,up-模式选择(1-加,0-减)

clr,clk,en,up :in std_logic;

output :out std_logic_vector(7 downto 0)

);

end counter;

architecture behave of counter is

signal count :std_logic_vector(7 downto 0);

begin

process(clk)

begin

if(clk'event and clk = '1') then --上升沿检测

if(clr = '1') then --清0

count <= "00000000";

elsif (en = '1') then --使能端使能

if(up = '1') then --加1计数

count <= count + 1;

elsif(up = '0') then --减1计数

count <= count - 1;

end if;

end if;

end if;

output <= count;

end process;

end behave;

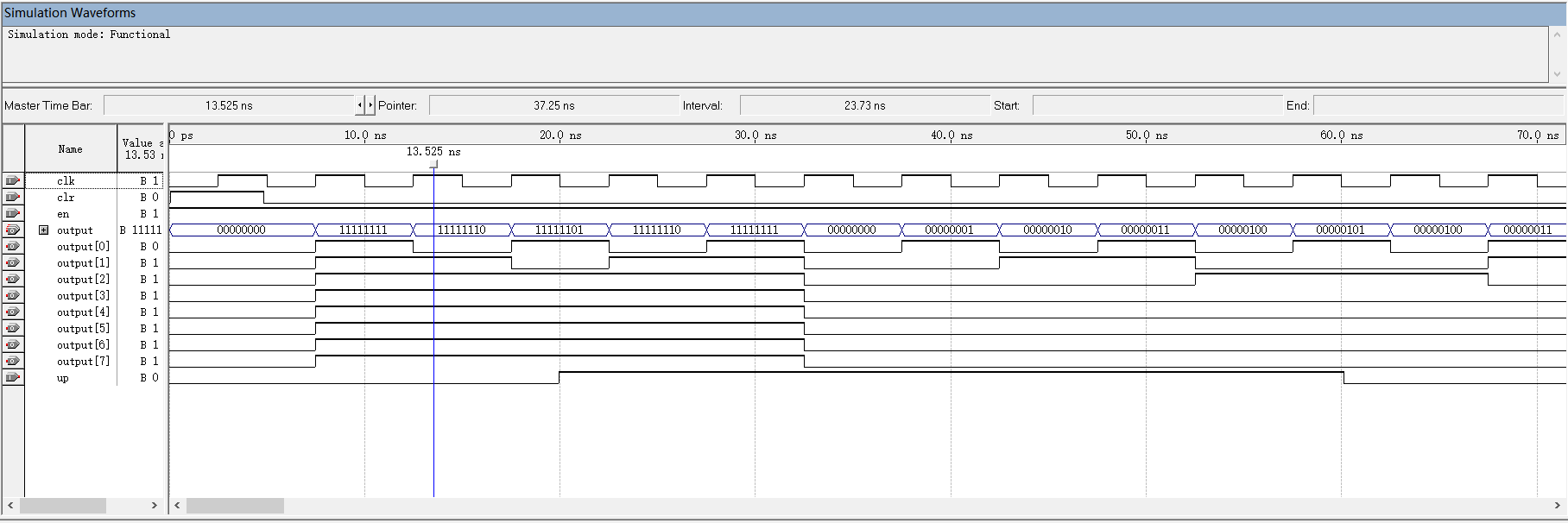

波形仿真图

最后

以上就是深情牛排最近收集整理的关于【VHDL语言学习笔记(六)】 计数器的全部内容,更多相关【VHDL语言学习笔记(六)】内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复