1、T触发器介绍

T触发器是一种边沿敏感的存储单元。只有一个信号输入端T,在时钟有效边沿到来时,T端输入有效信号,则触发器翻转,否则触发器保持不变。因此T触发器能够实现有效的计数功能,常用于实现数字计数器。T触发器可以由J-K触发器的J,K输入端与T输入端相连得到。J-K触发器见触发器详解——(二)J-K触发器

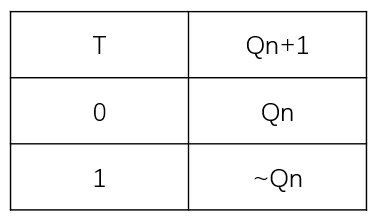

T触发器逻辑功能为:当T=0时,触发器状态不变Qn+1=Qn;而当T=1时,在脉冲有效边沿到来时翻转。触发器的特性表如表1-1所示:

表1-1:

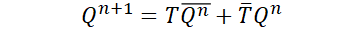

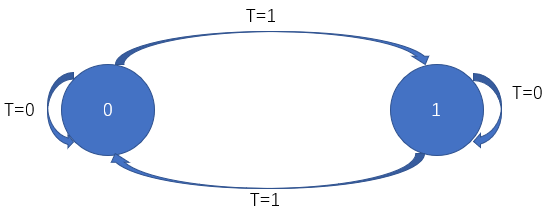

由触发器的特性表可以得特性方程以及状态转换图:

图1-1状态转换图

2、Verilog HDL语言实现

T触发器

module t(clk,rst,T,Q);

input clk,rst,T;

output Q;

reg Q;

always@(posedge clk or posedge rst)

begin

if (rst==1'b1) Q<=1'b0;

else if (T==1'b1) Q=~Q;

else Q=Q;

end

endmodule

测试代码

module t_t;

reg clk,rst,T;

wire Q;

initial

begin

clk=1'b0;

forever #10 clk=~clk;

end

initial

begin

rst=1'b0;T=1'b0;

#10 rst=1'b1;T=1'b1;

#10 rst=1'b0;T=1'b1;

#20 T=1'b1;

#20 T=1'b0;

#20 T=1'b1;

end

t u1(.clk(clk),.rst(rst),.T(T),.Q(Q));

endmodule

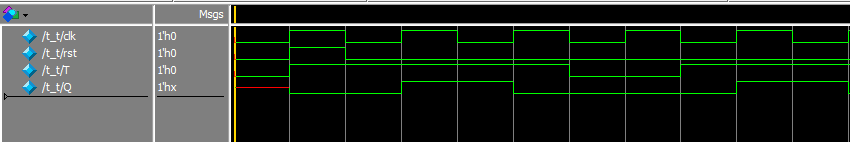

仿真结果

最后

以上就是拉长寒风最近收集整理的关于触发器详解——(三)T触发器的全部内容,更多相关触发器详解——(三)T触发器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复