提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

- Verilog学习

- 一、T触发器介绍

- 二、Verilog 语言实现

- 总结

Verilog学习

记录个人学习Verilog的过程以及遇到的问题。

一、T触发器介绍

T触发器(Toggle Flip-Flop,or Trigger Flip-Flop)只有一个信号输入端T,在时钟有效边沿到来时,T端输入有效信号,则触发器翻转,否则触发器保持不变。因此T触发器能够实现有效的计数功能,常用于实现数字计数器。(维基百科:设有一个输入和输出,当时钟由0转为1时,如果T和Q不相同时,其输出值会是1。输入端T为1的时候,输出端的状态Q发生反转;输入端T为0的时候,输出端的状态Q保持不变)

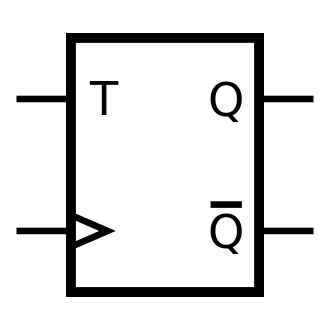

图:T触发器符号

图:T触发器符号

T触发器的特征方程:

Q

n

+

1

=

T

Q

n

′

+

T

′

Q

n

=

T

⊕

Q

n

Q_{n+1} = T Q_{n} ' +T ' Q_{n}= T⊕Q_{n}

Qn+1=TQn′+T′Qn=T⊕Qn

T触发器的特征表:

| T T T | Q Q Q | Q ˉ bar{Q} Qˉ |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

二、Verilog 语言实现

代码如下(示例):

module t(clk,rst,T,Q);

input clk,rst,T;

output reg Q;

always@(posedge clk or negedge rst)

begin

if(!rst)

Q<=1'b0;

else if(T)

Q<=~Q;

else

Q<=Q;

end

endmodule

总结

简单介绍了T触发器,以及verilog语言实现T触发器的功能。

练习:牛客网-VL2 异步复位的串联T触发器

最后

以上就是迅速口红最近收集整理的关于Verilog学习——T触发器Verilog学习一、T触发器介绍二、Verilog 语言实现总结的全部内容,更多相关Verilog学习——T触发器Verilog学习一、T触发器介绍二、Verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复