我是靠谱客的博主 谨慎羽毛,这篇文章主要介绍※用D触发器和必要的门电路设计一个同步3位右移移位寄存器. 在此基础上再加必要的门电路构成序列信号发生器, 产生序列信号00010111,现在分享给大家,希望可以做个参考。

之前我们已经学习过该如何使用74160/74163实现序列信号发生器的方法, 下面我们再学习另一种实现序列信号发生器的设计方法——这种方法比用74160/74163加门电路/74151/74153的设计方法难度要大, 须大家仔细推敲.

要设计一个同步3位右移移位寄存器, 应像下面这样绘制状态表.

| 状态表 | ||

| Q0* | Q1* | Q2* |

| R | Q0 | Q1 |

由上面的状态表, 绘制状态激励表.

| 状态激励表 | ||

| D0 | D1 | D2 |

| R | Q0 | Q1 |

根据状态激励表中的反馈逻辑, 实现同步3位右移移位寄存器.

在此基础上, 我们要实现序列信号发生器. 我们以Q2端作为序列信号产生端, 据此推理D0的反馈逻辑.

| 状态表(行不通) | ||||

| CLK顺序 | Q0 | Q1 | Q2 | D0 |

| 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | |

| 2 | 1 | 1 | 0 | |

| 3 | 0 | 1 | 1 | |

| 4 | 0 | |||

| 5 | 1 | |||

| 6 | 1 | |||

| 7 | 1 | |||

| 8 | 0 | 0 | 0 | |

| 状态表(行不通) | ||||

| CLK顺序 | Q0 | Q1 | Q2 | D0 |

| 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | |

| 2 | 0 | 1 | 0 | |

| 3 | 0 | 0 | 1 | |

| 4 | 1 | 0 | 0 | |

| 5 | 1 | |||

| 6 | 1 | |||

| 7 | 1 | |||

| 8 | 0 | 0 | 0 | |

| 状态表(行不通) | ||||

| CLK顺序 | Q0 | Q1 | Q2 | D0 |

| 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | |

| 2 | 0 | 1 | 0 | |

| 3 | 1 | 0 | 1 | |

| 4 | 0 | 1 | 0 | |

| 5 | 1 | |||

| 6 | 1 | |||

| 7 | 1 | |||

| 8 | 0 | 0 | 0 | |

| 状态表(行不通) | ||||

| CLK顺序 | Q0 | Q1 | Q2 | D0 |

| 0 | 0 | 0 | 0 | |

| 1 | 1 | 0 | 0 | |

| 2 | 0 | 1 | 0 | |

| 3 | 1 | 0 | 1 | |

| 4 | 1 | 1 | 0 | |

| 5 | 0 | 1 | 1 | |

| 6 | 0 | 0 | 1 | |

| 7 | 1 | |||

| 8 | 0 | 0 | 0 | |

经过上面4种尝试, 我们得到符合题目要求的状态表.

| 状态表(最终答案) | ||||

| CLK顺序 | Q0 | Q1 | Q2 | D0 |

| 0 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 1 |

| 3 | 1 | 0 | 1 | 1 |

| 4 | 1 | 1 | 0 | 1 |

| 5 | 1 | 1 | 1 | 0 |

| 6 | 0 | 1 | 1 | 0 |

| 7 | 0 | 0 | 1 | 0 |

| 8 | 0 | 0 | 0 | 1 |

这里很有必要对判断状态表的取值是否符合题目要求做出一点说明: 我们判断出某种取值方案不合理的依据是, 比如100的下一状态为××1(应为×10)或按照该种取值方案进行设计后, 无法满足序列信号数量的循环状态.

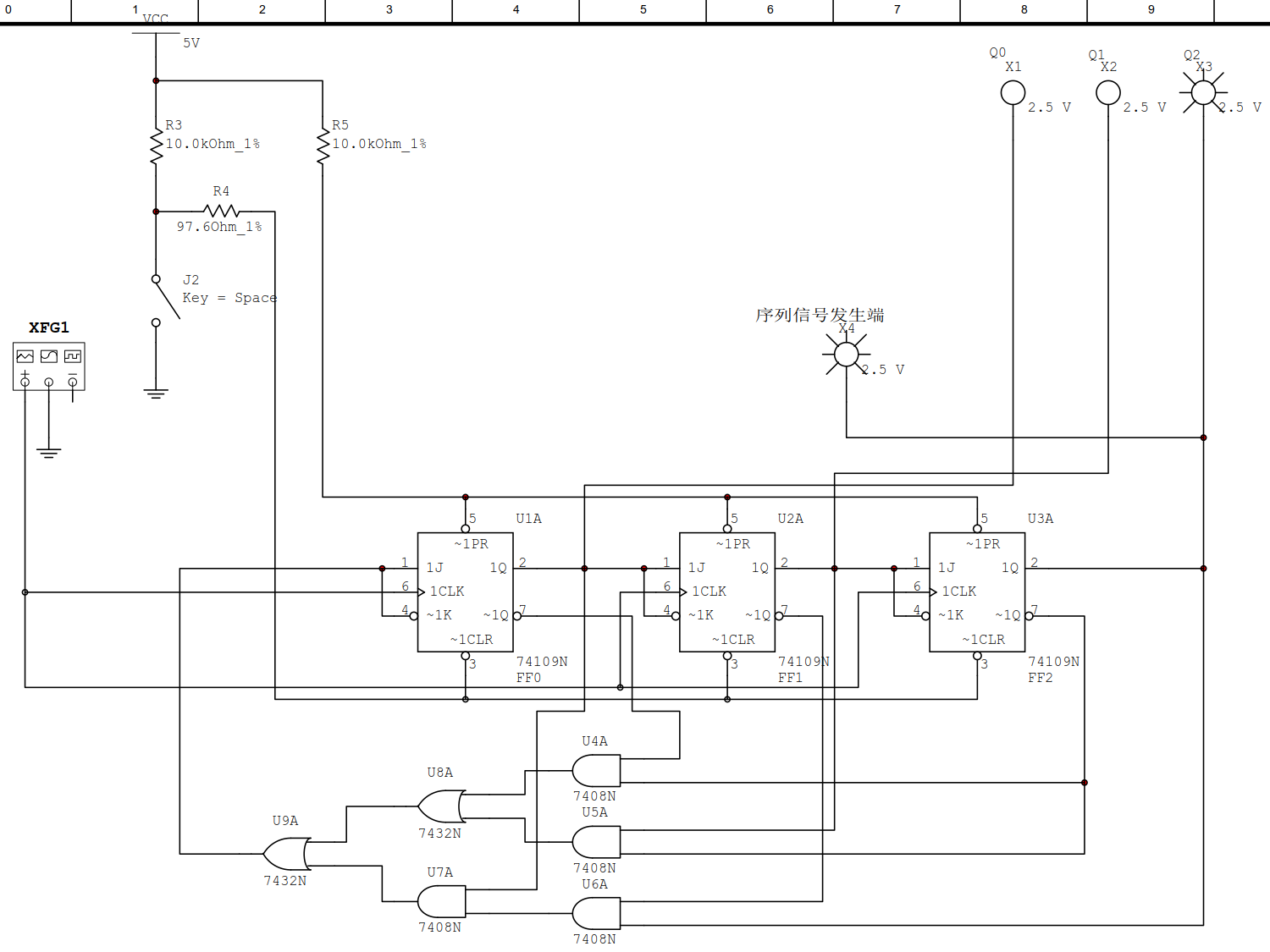

根据上面的状态表(最终答案), 可以得知 D0=Q0'Q2'+Q1Q2'+Q0Q1'Q2, 据此对电路进行改造, 绘制最终电路原理图.

通过上面完整的设计过程, 我们可以看出, 用同步右移移位寄存器实现序列信号发生器的关键在于选择正确的状态序列.

最后

以上就是谨慎羽毛最近收集整理的关于※用D触发器和必要的门电路设计一个同步3位右移移位寄存器. 在此基础上再加必要的门电路构成序列信号发生器, 产生序列信号00010111的全部内容,更多相关※用D触发器和必要的门电路设计一个同步3位右移移位寄存器.内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复