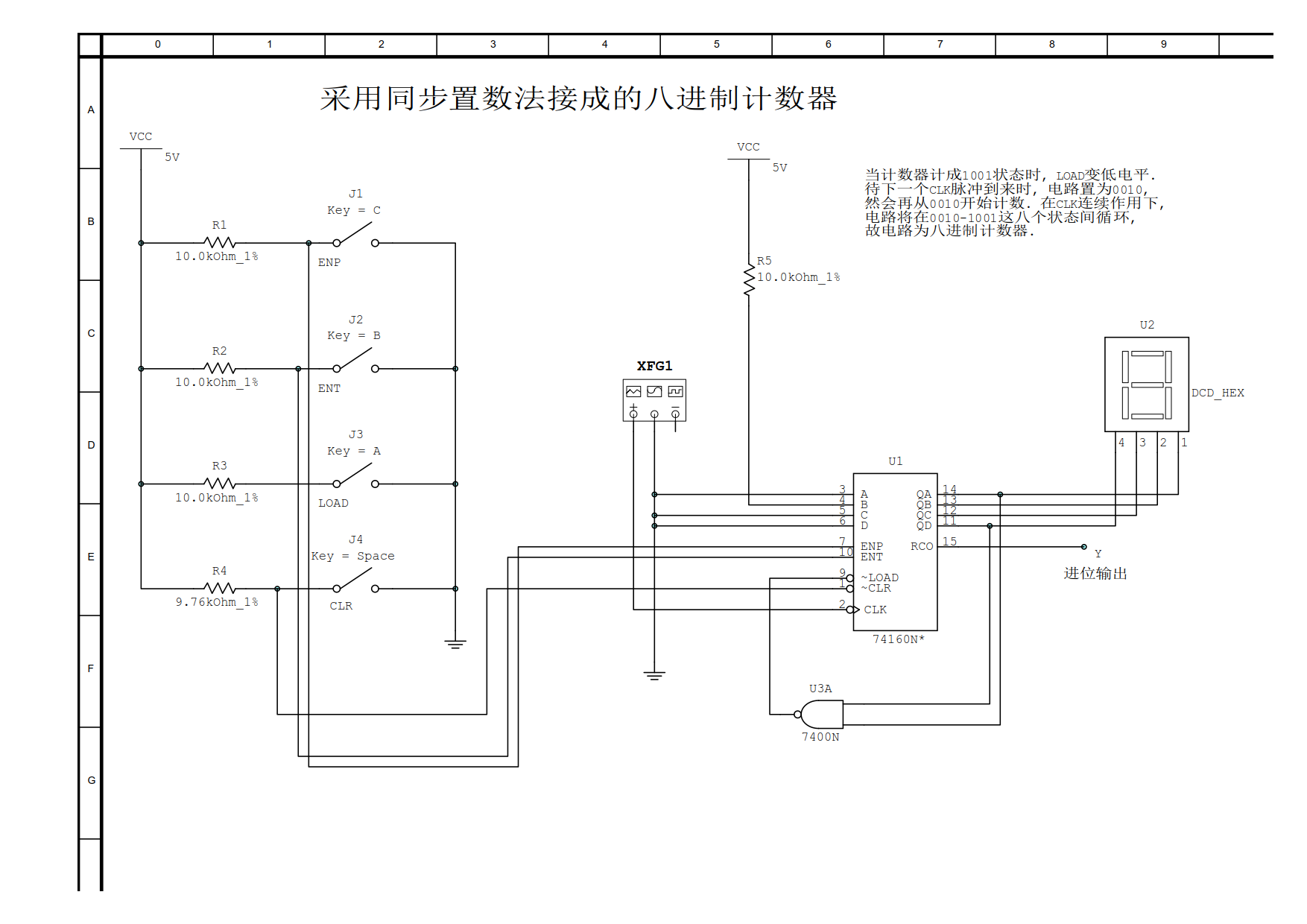

我们先来看一下电路逻辑图, 从中提取核心信息:

① 将QD、QC、QB、QA接成0010是为了配合LOAD引脚使用, 以将74160的状态置为0010.

②计数器的最大状态为1001, 当74160到达1001时, 通过7400N与非门将LOAD引脚置为0, 当下一个CLK上升沿到来时, 74160的状态即被置为0010; 当电路的状态到达0010时, LOAD引脚恢复高电平, 之后若干个CLK上升沿 74160正常计数.

③当QD、QC、QB、QA到达1001时, 计数器产生进位信号, 即RCO=1: 这正好与74160本身的性质一致, 所以可直接将74160的RCO引脚作为计数器输出引脚.

可能产生的疑问:

①ENT和ENP引脚是不是有些多余?

答: 不多余. ENT和ENP引脚有一个为低电平时, 74160即处于保持状态——后续要更新的博客"ENT引脚设计法解析"就是用这两个引脚的巧妙配合, 实现同步100进制加法计数器的功能.

②QD、QC、QB、QA被置为0010前后, 74160是如何工作的?

答: (QD, QC, QB, QA) = (1,0,0,0) -> 系统CLK上升沿到来 -> (QD, QC, QB, QA) = (1,0,0,1) -> LOAD 由 1->0 -> 系统CLK上升沿到来 -> (QD, QC, QB, QA) = (D, C, B, A) = (0,0,1,0) -> LOAD 由 0->1 -> 系统CLK上升沿到来 -> (QD, QC, QB, QA) = (0,0,1,1) -> ...... -> (QD, QC, QB, QA) = (1,0,0,0). 74160按照上述描述循环变化. 补充说明一下, 当 (QD, QC, QB, QA) = (1,0,0,1)时, RCO =1, 其余状态下RCO=0.

③用触发器和逻辑门设计同步N进制计数器时就对进位的设置有疑惑, 为什么是电路状态到达1001时 RCO=1, 而不是电路状态到达0000时 RCO=1?

答: 这个问题也一直困惑着我, 但从74160的使用中我得出了可靠的结论. 我们来分析一下进位引脚RCO的变化情况: 电路状态到达1000(RCO=0) -> 系统CLK上升沿到来 -> 电路状态到达1001(RCO=1) -> 系统CLK上升沿到来 -> 电路状态到达0000(RCO=0), 根据上述过程, 若将RCO引脚引出, 加到非门的输入, 再将非门的输出接到高位74160的CLK引脚, 那么过程将是这样的: 电路状态到达1000(RCO=1) -> 系统CLK上升沿到来 -> 电路状态到达1001(RCO=0) -> 系统CLK上升沿到来 -> 电路状态到达0000(RCO=1). 从这里可以看出, 现在的进位逻辑符合我们的认知了.

④只要是用74160以同步置数法设计N进制计数器, 都可以直接将RCO引脚拉出来作为进位输出引脚吗?

答: 不可以. 只有当我们设计的电路的最后一个状态为1001时, 才可以这样做: 否则, 就要重新设计输出引脚. 比如电路的状态从0011依次递增到1000, 那么进位输出引脚应该在电路到达1000时变为高电平——所以可以将QD引脚直接引出, 作为进位输出引脚即可.

⑤为什么上面电路中将QD和QA引脚接到7400N与非门的两输入端, 输出端就可以直接接到LOAD引脚, 而不是需要将QD、QC、QB、QA按照1001的状态, 使LOAD=QD·QC'·QB'·QA呢?

答: 如此考虑说明你是一个严谨的人, 但这并不是最简单的解法, 即要浪费一个或多个逻辑门. 我们来看一下74160的状态变化过程: 0000 -> 0001 -> 0010 -> 0011 -> 0100 -> 0101 -> 0110 -> 0111 -> 1000 -> 1001 -> 0000. 显然, 只有状态为1001时, QD和QA才同时为高电平. 所以可以按照上面电路图中的接法来接线. 但对于74163(十六进制加法计数器)就要多考虑一些情况: 比如用同步置数法, 当电路状态到达1101时(比如电路状态从0100开始), LOAD引脚置为0. 那么这里就不能只将QC和QA引出, 接到与非门的两输入端, 输出端接到LOAD引脚了: 而是应该将QD、QC和QA引出, 接到与非门的三输入端, 输出端接到LOAD引脚. 这里需读者自行体会, 且需要根据实际情况来做出相应的设计.

⑥以74160为核心部件, 再辅以合适的逻辑门, 可以构成具有何种功能的电路呢?

答: 可以用三片74160和合适的逻辑门接成N(101≤N≤1000)进制加法计数器, 或者用其它方法接成相应功能的电路. 若能灵活使用74160, 那么在设计时序逻辑电路时的效率会大大提升.

⑦为什么我把同步置数法放在74160应用介绍部分的第一篇, 是不是有一定的用意呢?

答: 是的. 我最喜欢以同步置数法设计电路, 因为在设计电子表时, 我发现用同步置数法得到的数字显示是最稳定的, 也是最贴合实际要求的. 若用异步清零法来设计电路, 那么在高低位数字进位的一瞬间, 显示的数字在一小段时间内会经历两次变化, 即会使使用者感到眼花缭乱. 既然同步置数法和异步清零法都可以实现某种功能, 那么为何不用显示最为稳定的那种方法(同步置数法)呢. 当然, 还有ENT引脚设计法没有给大家介绍. ENT引脚设计法大多用于级联74160以构成更高进制的计数器电路, 所以可以说, 要想掌握ENT引脚设计法, 就必须先将单片74160的设计方法弄懂; 否则是行不通的.

⑧为什么我将设计的电路称为"同步八进制计数器", 而不是"同步八进制加法计数器"呢?

答: 若产生该疑惑, 则说明对于用触发器和逻辑门来设计同步时序逻辑电路这一部分尚未完全掌握, 需回过头去复习这一部分的内容. 由于电路的初始状态为0010, 即第一个状态不是0, 不符合日常加法计数的状态规律(不是从0000开始), 所以称之为"同步八进制计数器".

⑨什么时候用N进制计数器, 什么时候用N进制加法计数器呢?

答: 这个问题问得好. 如果我们需要将状态显示出来, 或电路的计算需要用到从零开始计数的状态, 那么就必须用N进制加法计数器. 如果只是记录某个动作的发生次数, 当次数到达一定数量时产生输出信号, 那么用N进制计数器即可.

最后

以上就是完美河马最近收集整理的关于74160同步置数法解析(以接成同步八进制计数器为例)的全部内容,更多相关74160同步置数法解析(以接成同步八进制计数器为例)内容请搜索靠谱客的其他文章。

发表评论 取消回复