文章目录

(一)半加器

- 使用算术操作符实现半加器

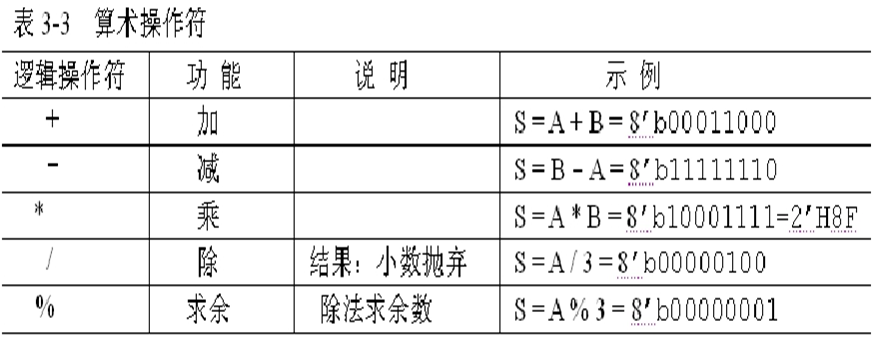

- 算术操作符的简述

- 使用库元件实现半加器

(二)半减器

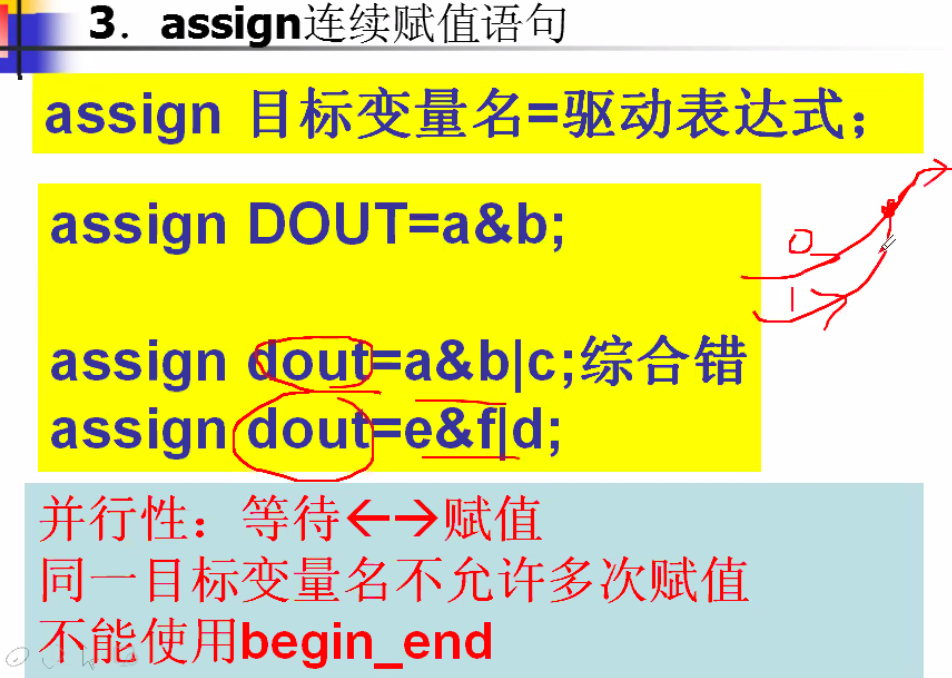

- assign语句的注意事项

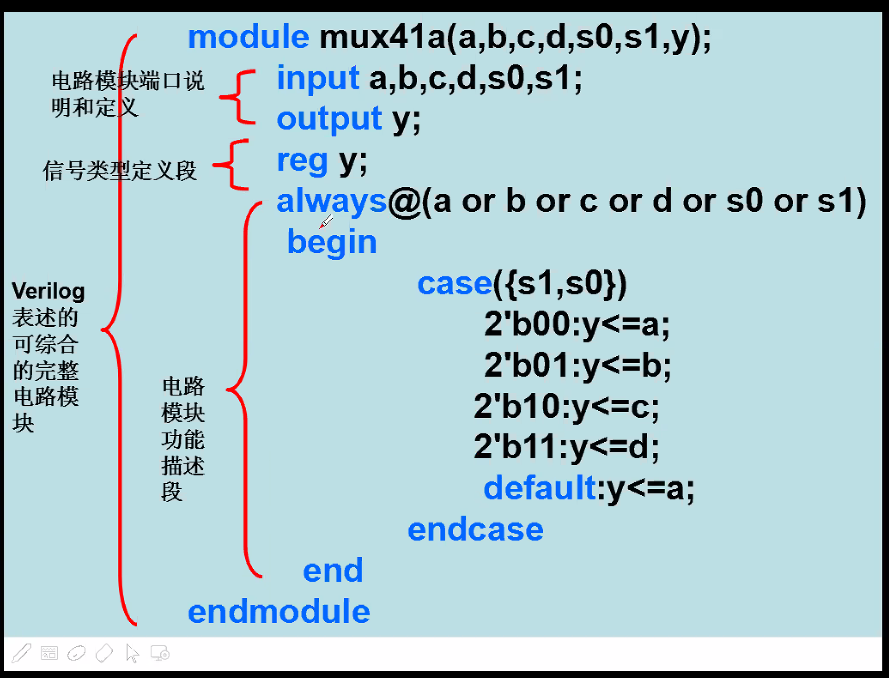

(三)4选1多路选择器

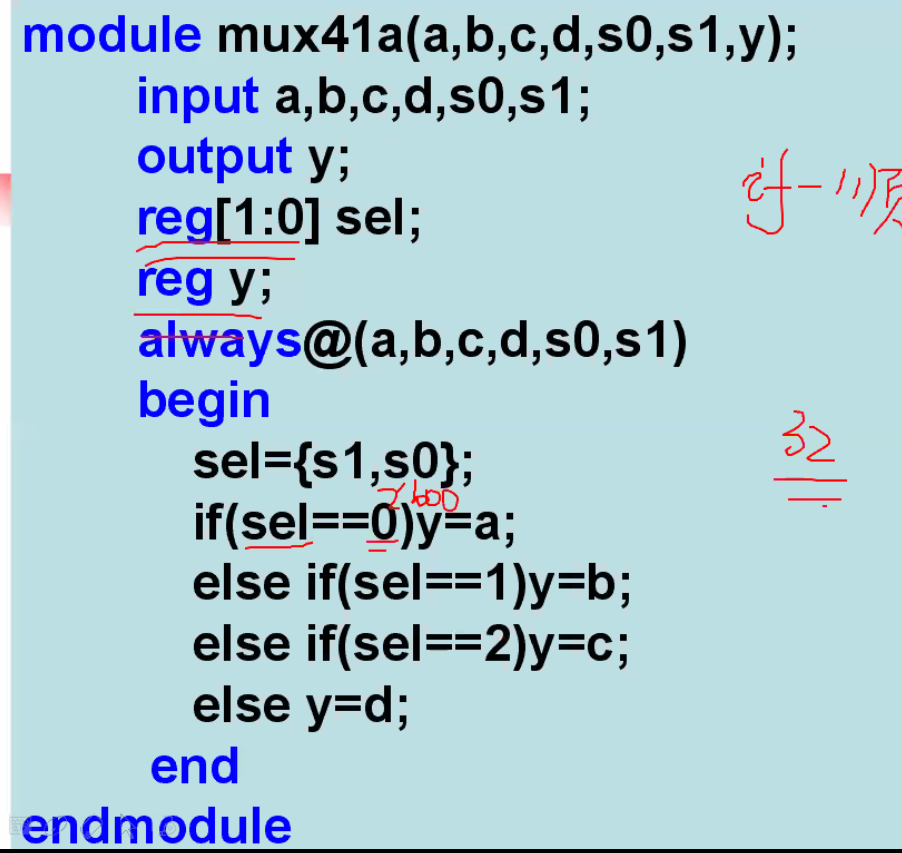

- always、case和reg的简单使用

- case的4种情况

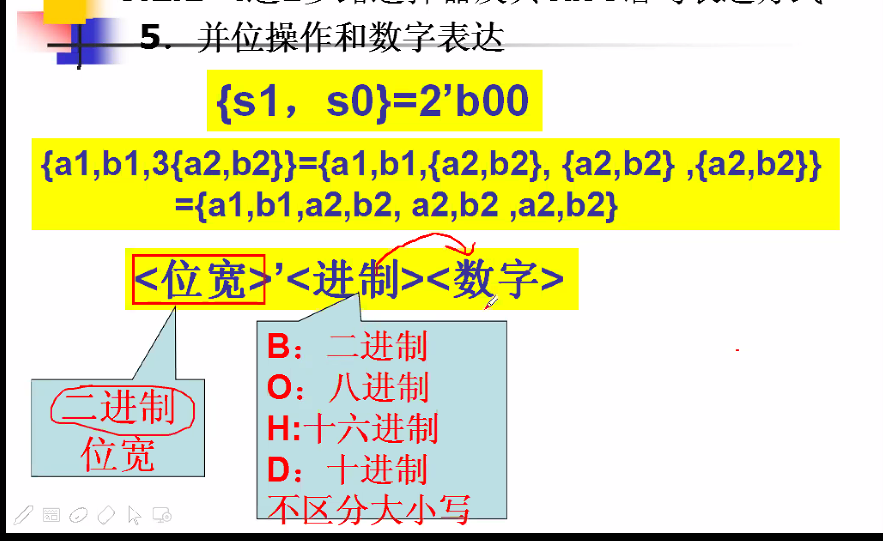

- 并位操作符

- wire[1:0]的写法

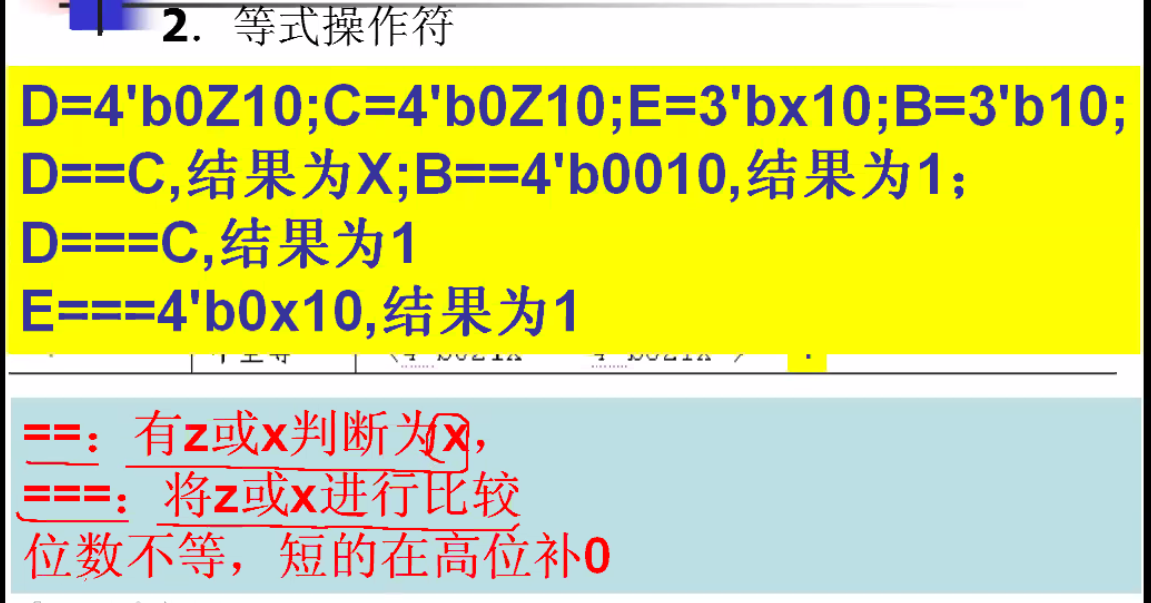

- 等式操作符

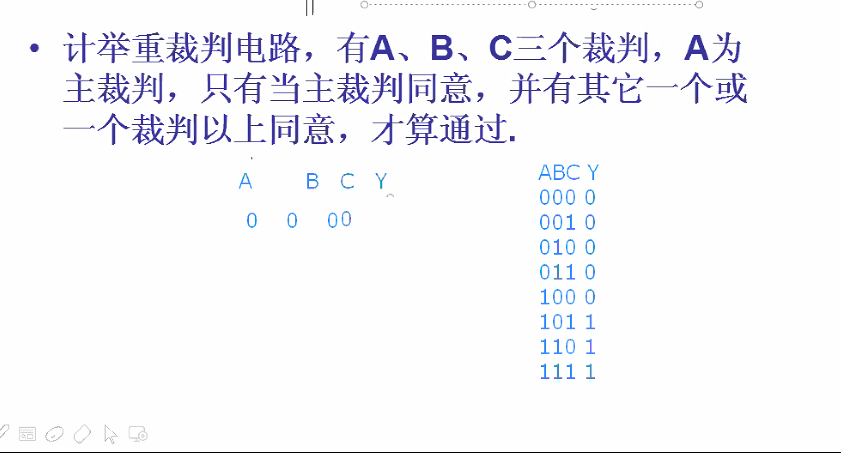

(四)举重裁判电路

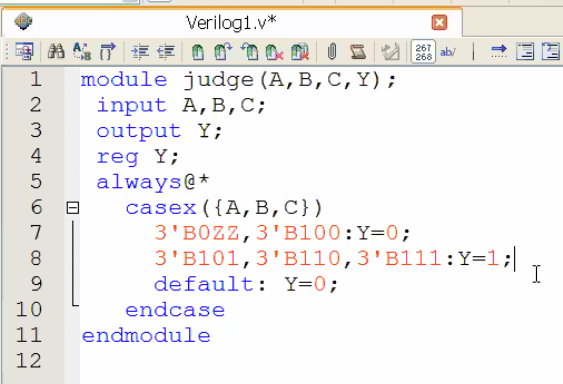

(五)利用半加器和或门实现全加器

(六)利用半减器和或门实现全减器

(七)使用算术操作符实现8位加法器

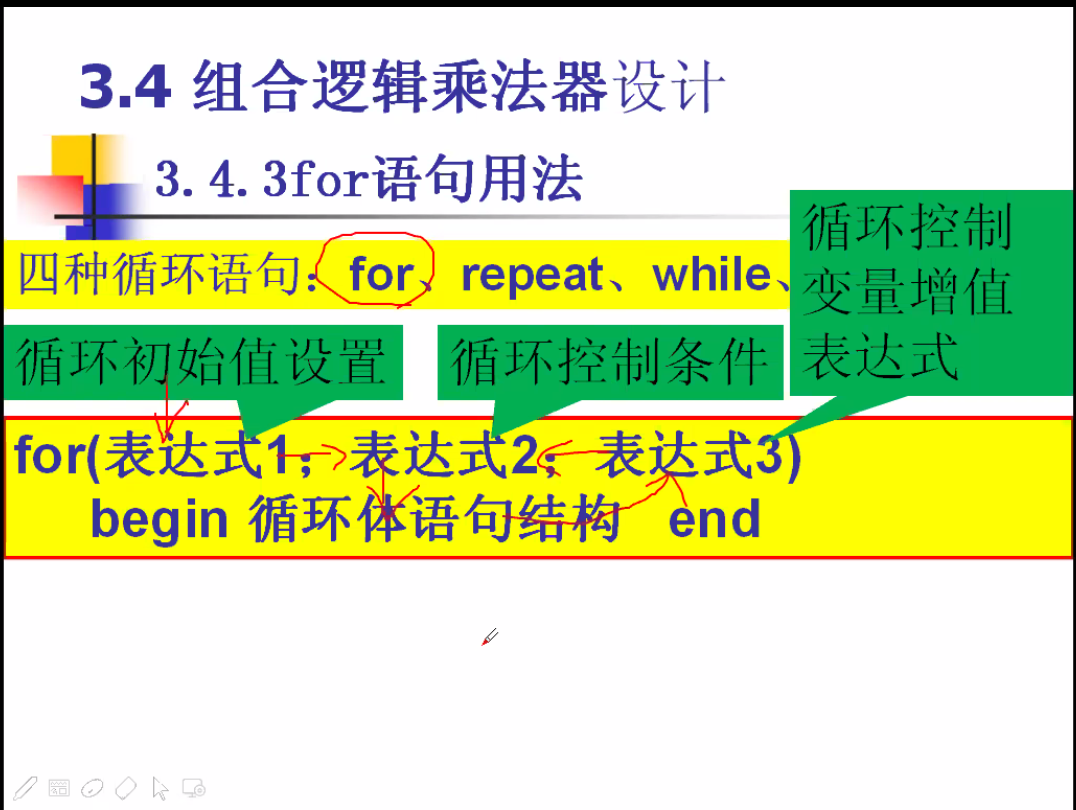

(八)乘法器的设计

- parameter和localparam

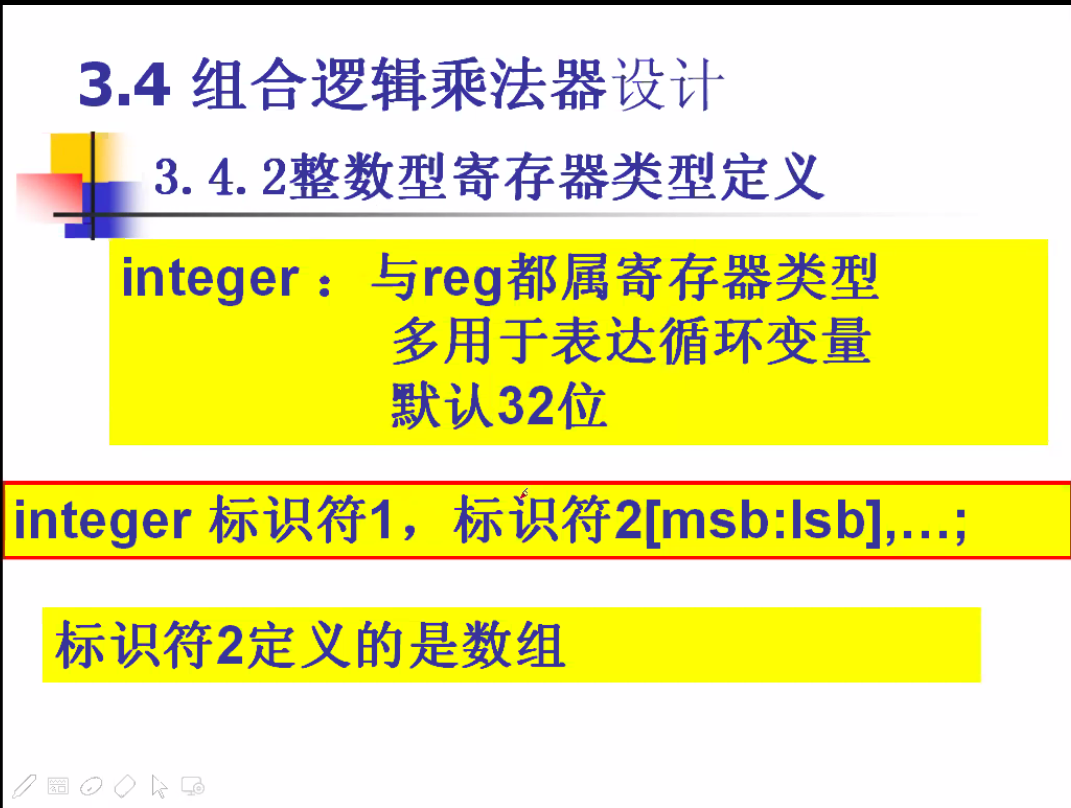

- integer

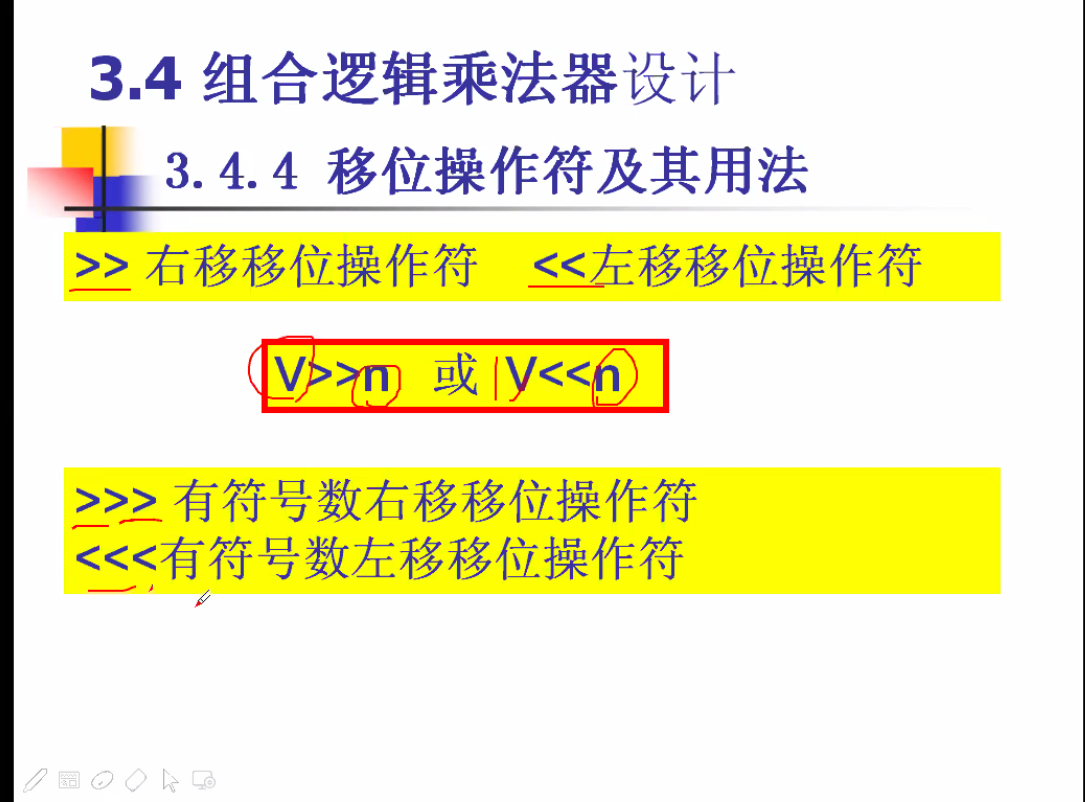

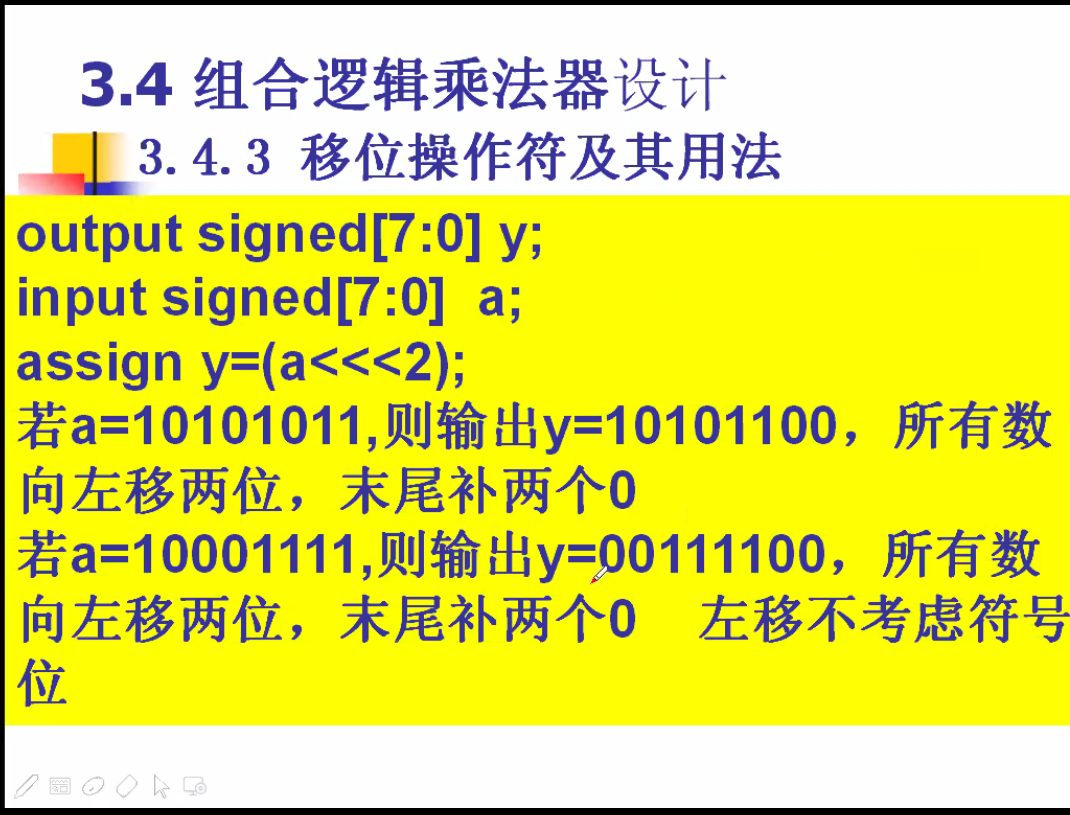

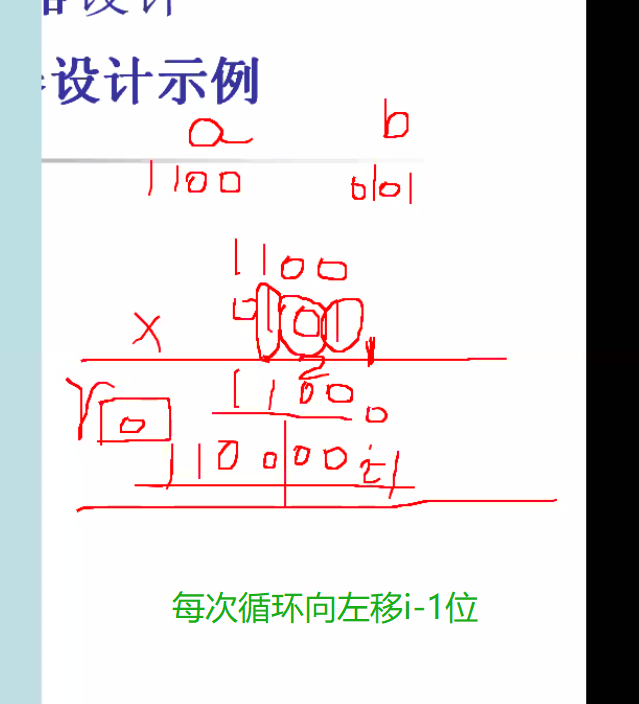

- 移位操作:左移

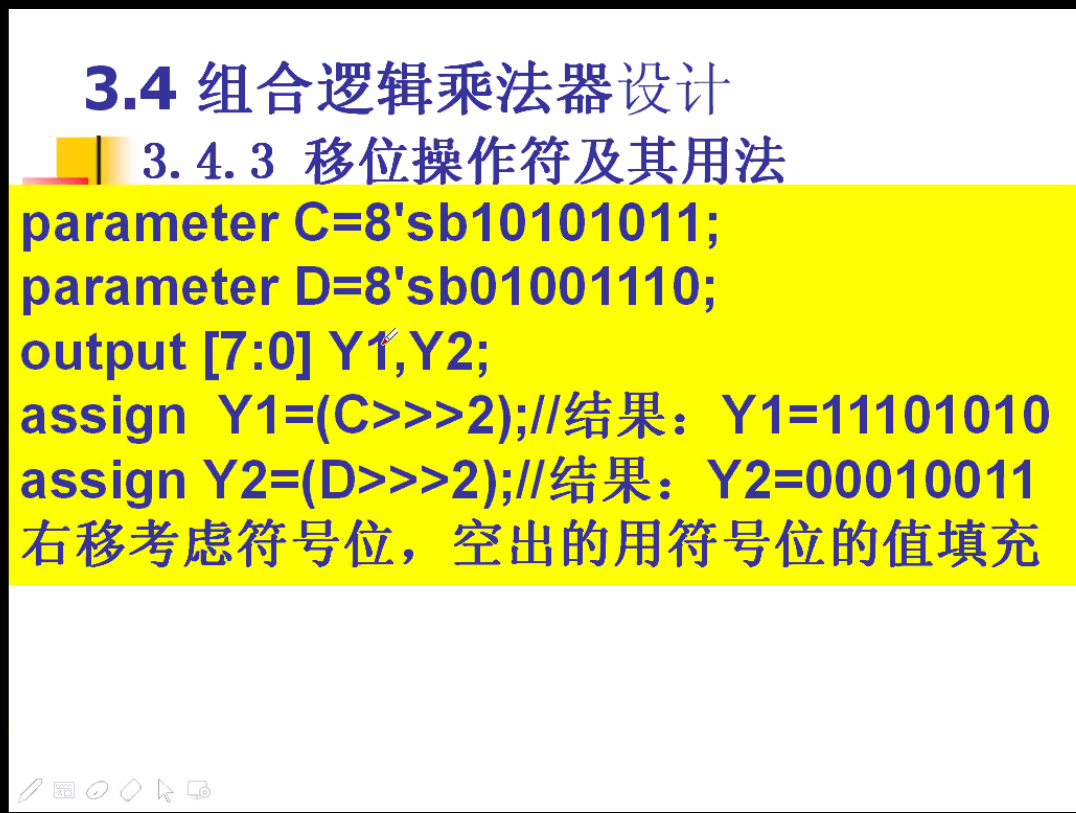

- 移位操作:右移

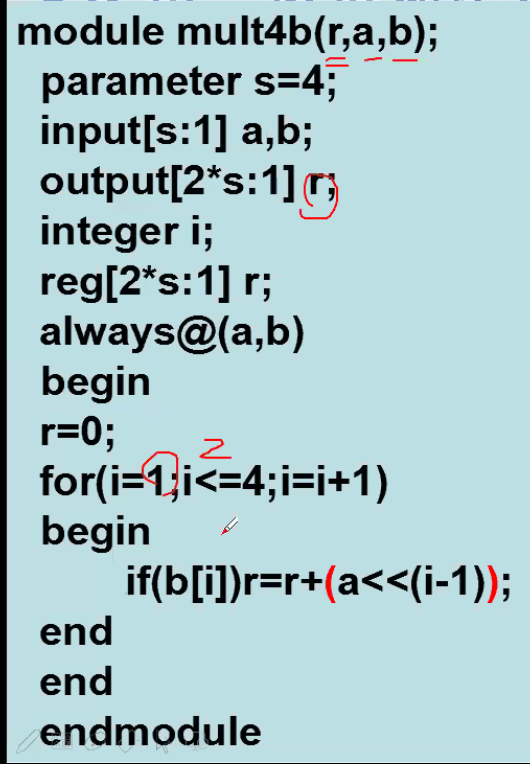

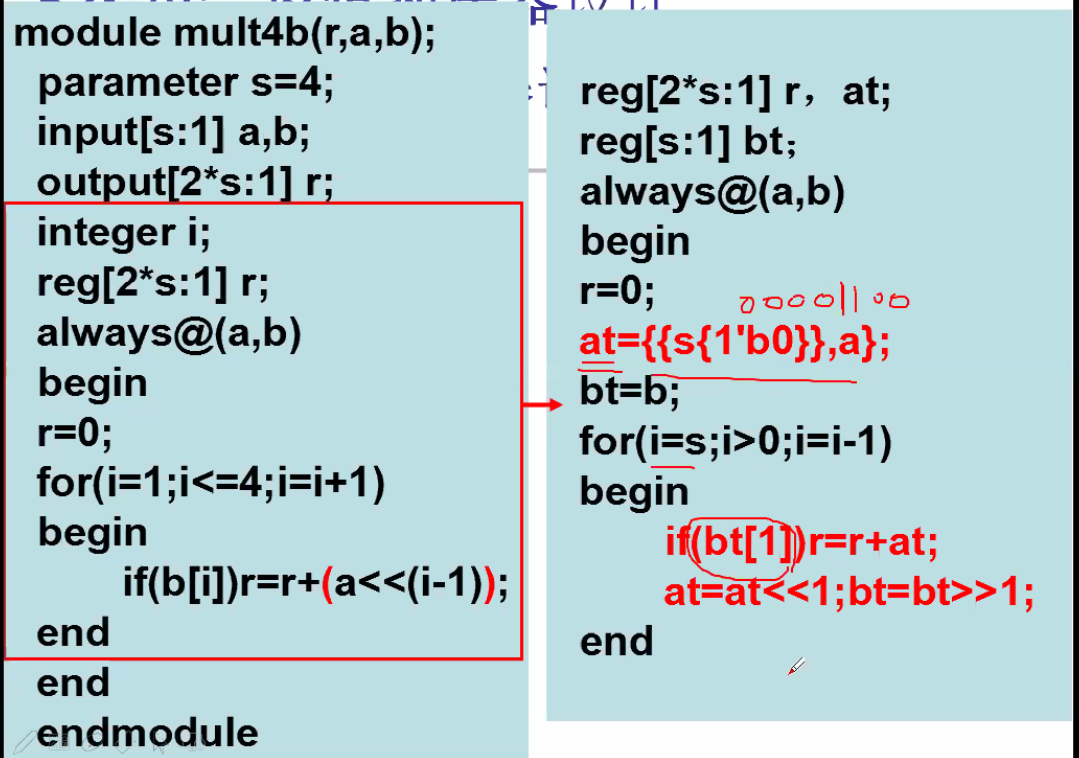

- 使用for循环实现乘法器

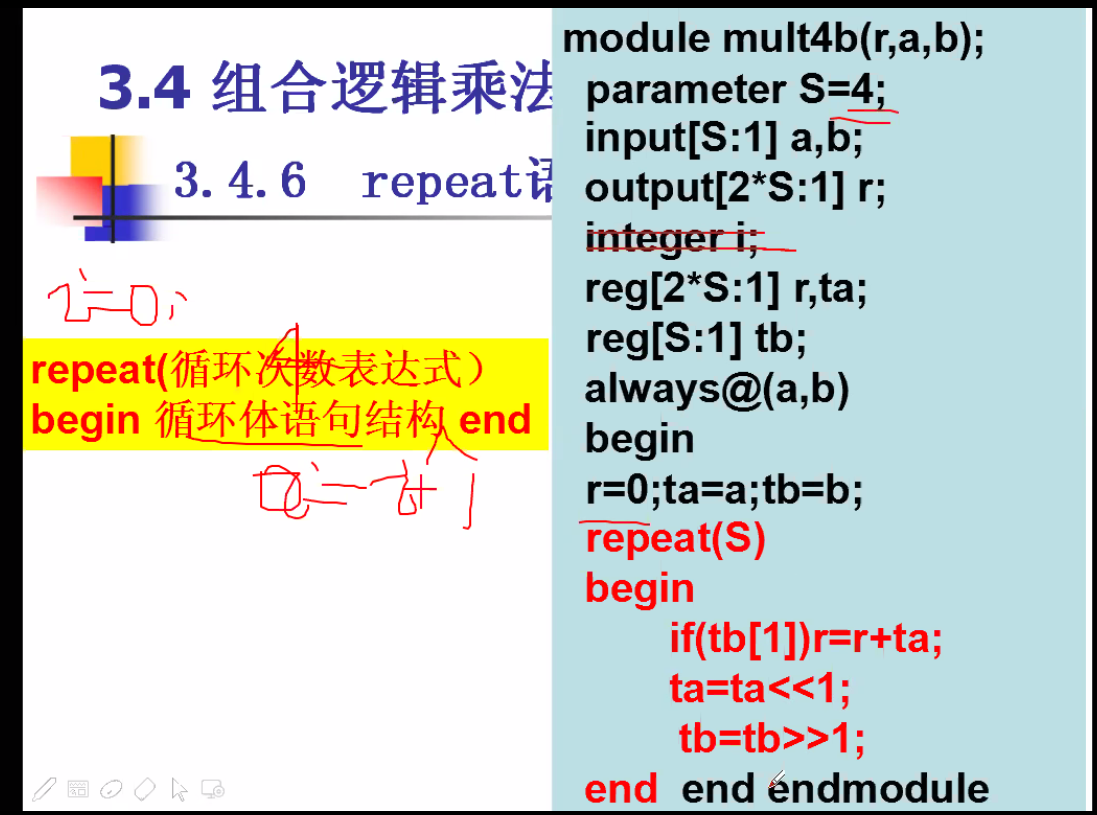

- 使用repeat循环实现乘法器

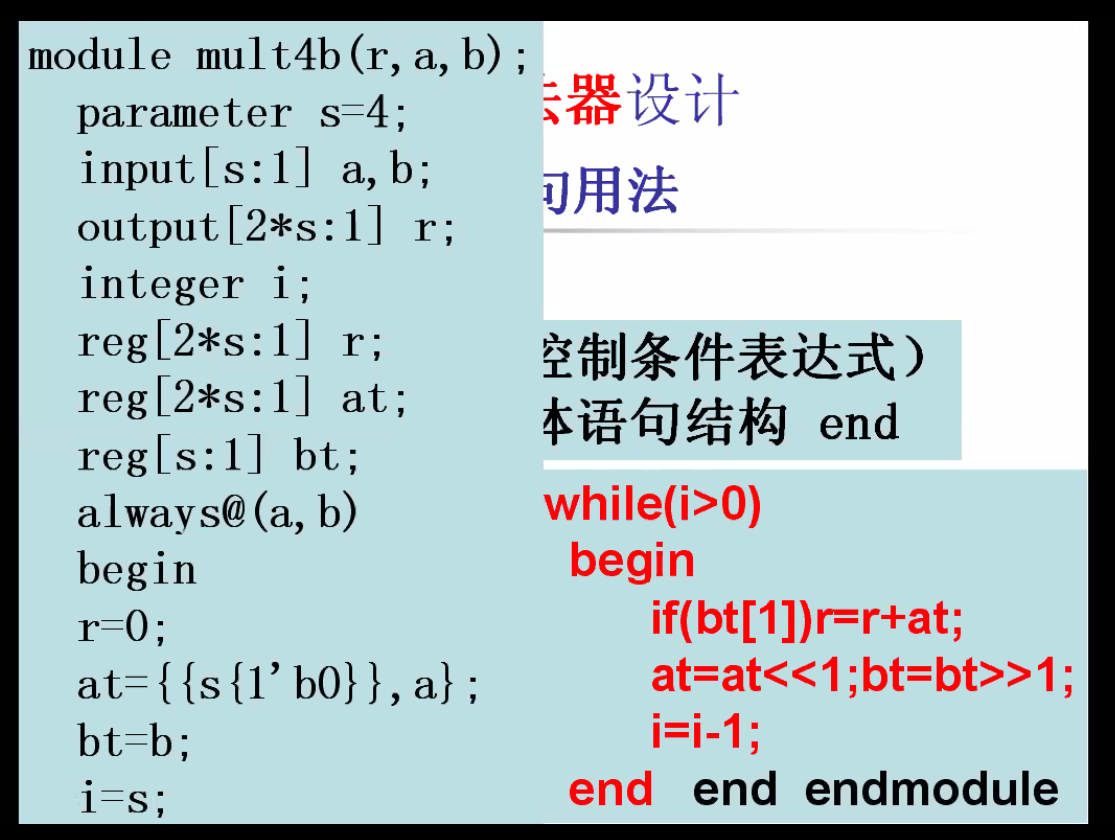

- 使用while循环实现乘法器

(九)练习:一个电路有32位输入,该电路输出输入端口1的个数

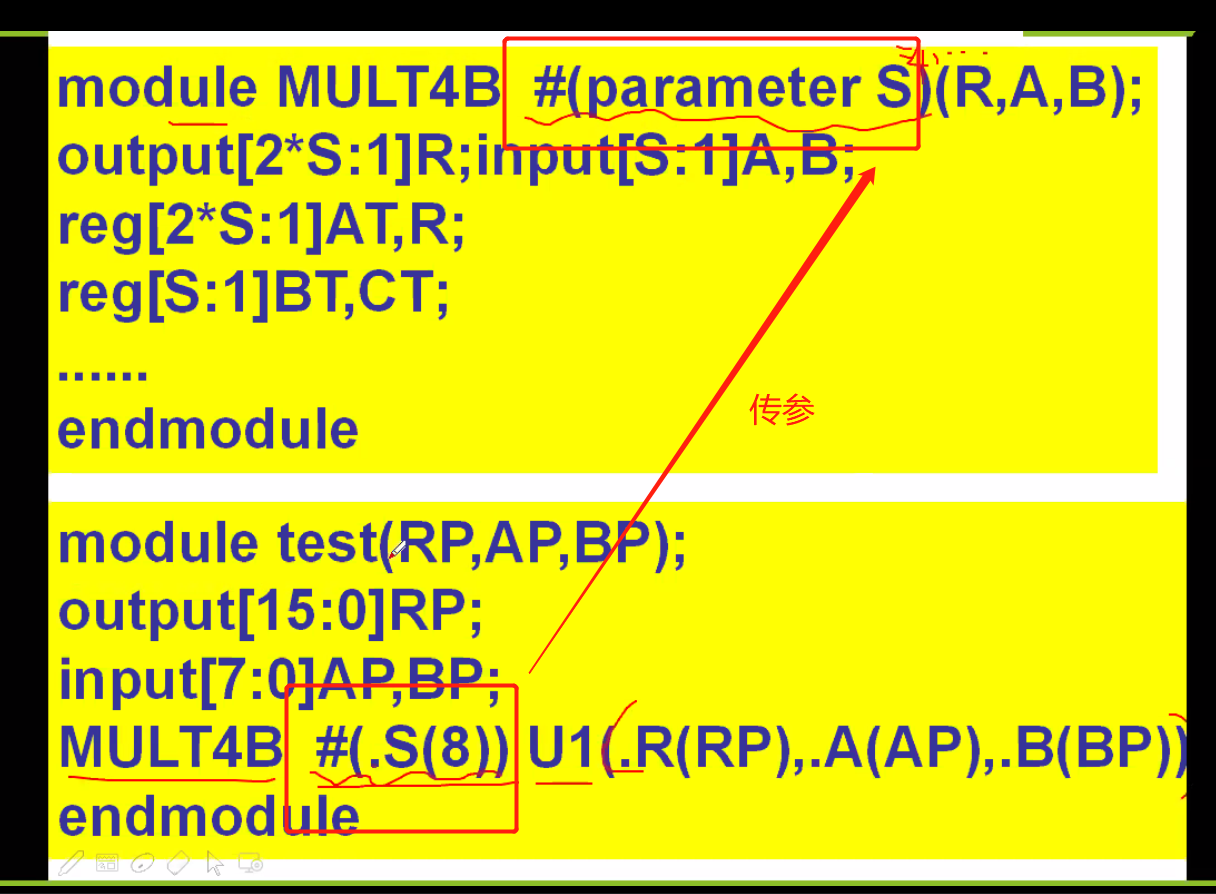

(十)参数传递语法

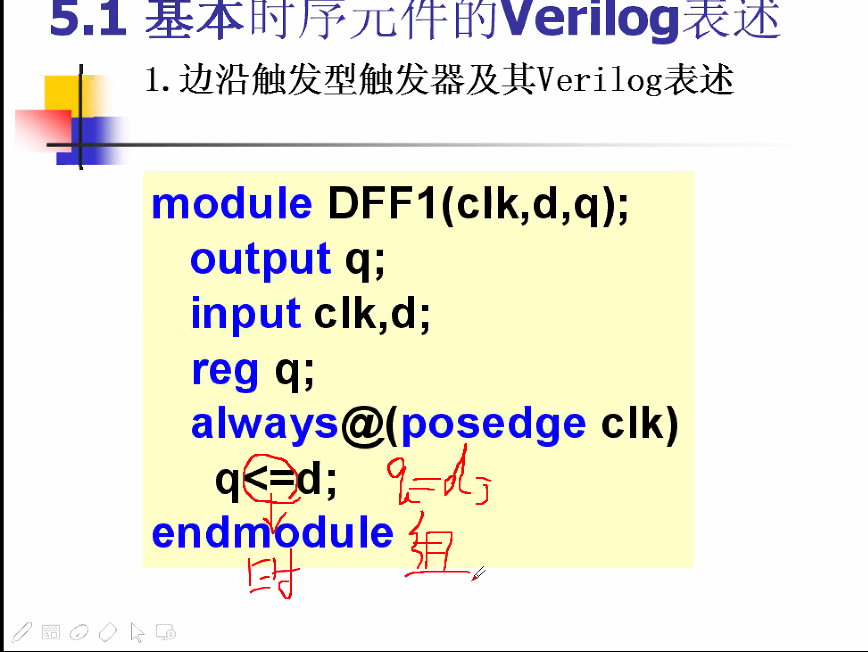

(十一)==和<=的区别

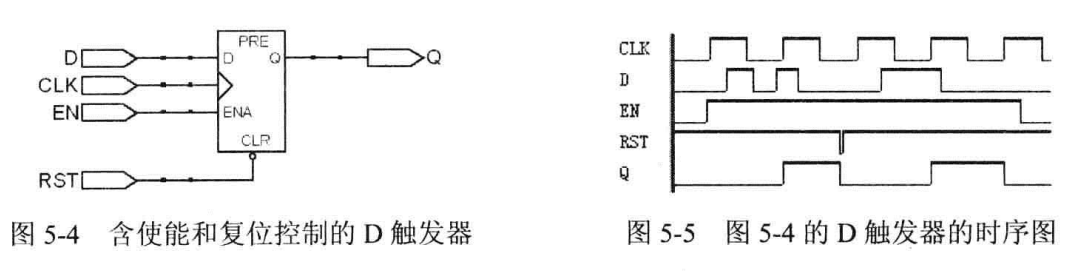

(十二)含异步清0和同步使能控制的D触发器

(十三)含同步清0的D触发器

(十四)D触发器的练习题

(十五)同步清0的例题

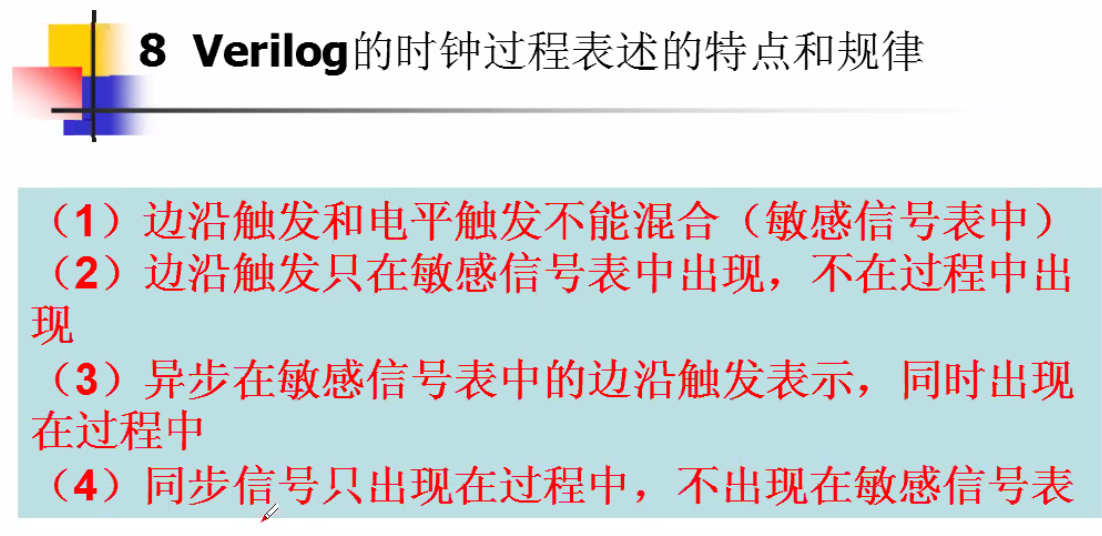

(十六)时序电路描述的一些特点和规律

(十七)例题:16进制计数器

(十八)练习:60进制计数器

(十九)基于16进制计数器加以增加模可控的功能

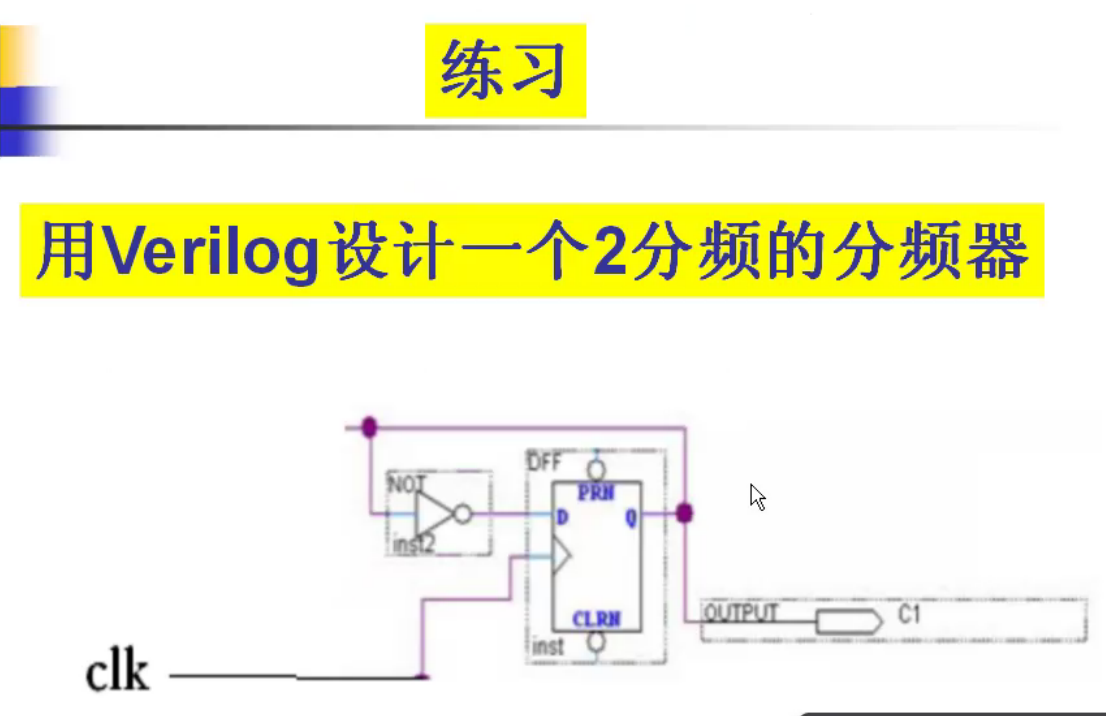

(二十)练习:设计一个2分频的分频器

半加器

- 真值表

| x | y | so | co |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

- 代码

(注意^是异或,|是或)

module h_adder(a,b,co,so);

output co,so;

input a,b;

assign so=a^b;

assign co=a&b;

endmodule

- 使用算术操作符实现半加器

module h_adder(a,b,co,so);

output co,so;

input a,b;

assign {co,so}=a+b;

endmodule

- 算术操作符的简述

- 使用库元件实现半加器

module h_adder(A,B,SO,CO);

input A,B;

output SO,CO;

xor u1(SO,A,B);

and u2(CO,A,B);

endmodule

使用库元件的话可以使用省略写法,如下:

module h_adder(A,B,SO,CO);

input A,B;

output SO,CO;

xor(SO,A,B);

and(CO,A,B);

endmodule

半减器

- 真值表

| x | y | diff | s_out |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

- 代码

(注意^是异或,|是或)

module h_suber(x,y,diff,s_out);

output diff,s_out;

input x,y;

assign diff=x^y;

assign s_out=(~x)&y;

endmoudle

注意:assign不能多次赋值

4选1多路选择器

- 代码

- always类似于监听器,括号里面的变量任意一个发生改变,就执行后面的代码

- always可以用省略写法,后面直接写

*,如:always@* case({s1,s0})有四种取值情况,分别是:00、01、11、10- 默认变量都是wire类型,被赋值的变量需要是寄存器类型

reg y;意思是把y声明成寄存器类型

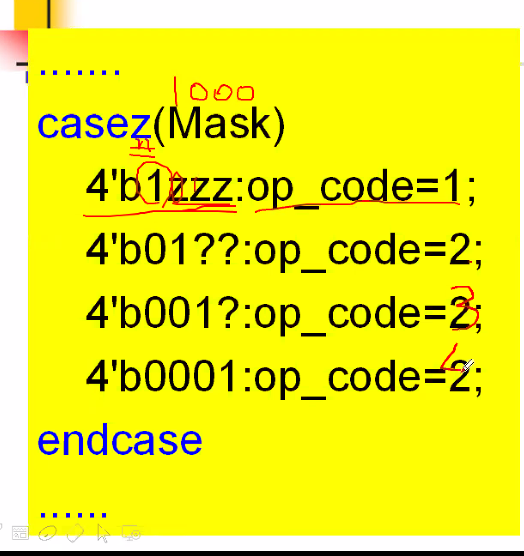

case的4种情况详解:

先看一个例子

忽略z,所以1000可以匹配第一种情况

?是不考虑的,所以0100可以匹配第二种情况

总结:

- case语句的表达式的值有4种情况:0、1、z、x,4种是不同的

故表达式要严格的相等才可以操作分支语句 - casez语句中的表达式情况有3种:0、1、x,不用关心z,z可以和任何数值相等

即z=0,z=1,z=x - casex语句的表达式情况有2种:0、1,不用关心x和z

即x=z=0,x=z=1

并位操作详解:

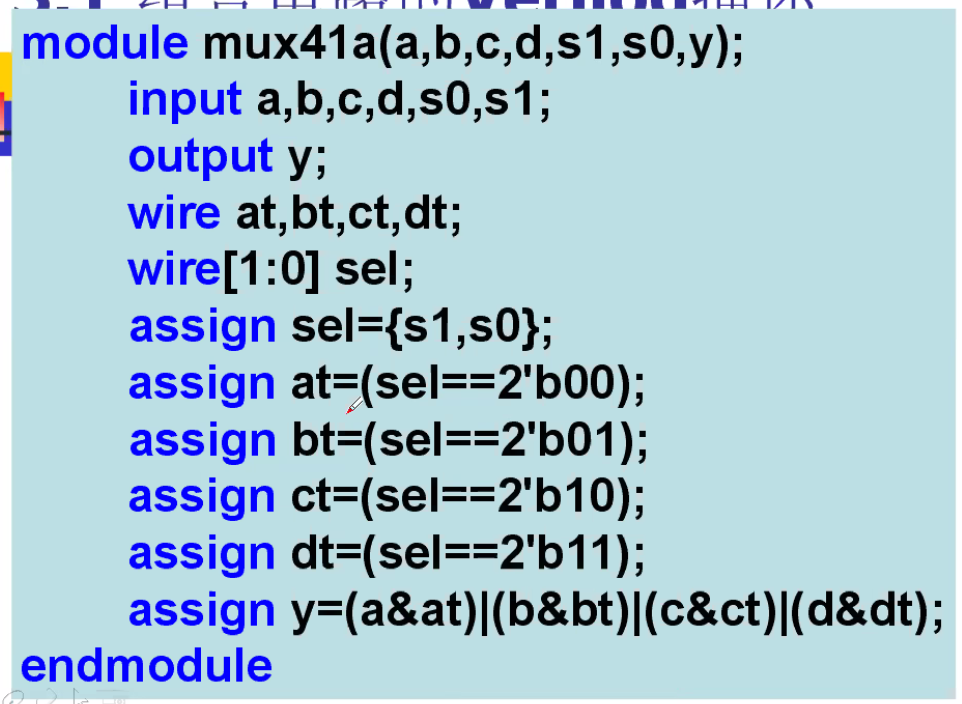

- 四选一电路的第二种写法

注意:wire[1:0] sel;是两位寄存器,最低位是wire[0],最高位是wire[1],即取值为0~2

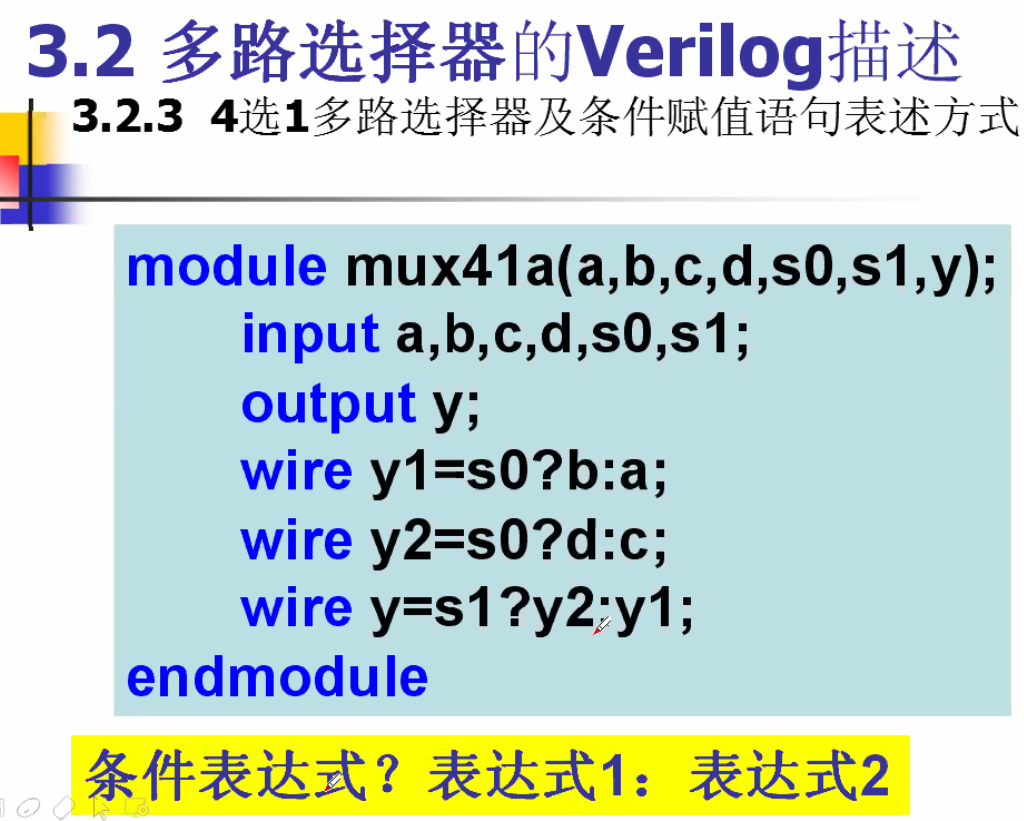

- 四选一电路的第三种写法

- 四选一电路的第四种写法

注意:等式操作符会自动补零,短的在高位补零,直到一样长

举重裁判电路

- 代码(自己写的)

注意:=是立即赋值,而<=会出现一些问题,以后都用=

module judge(A,B,C,Y);

input A,B,C,Y;

output Y;

reg Y;

always@(A or B or C or Y)

begin

case({A,B,C})

3'b000:Y<=0;

3'b001:Y<=0;

3'b010:Y<=0;

3'b011:Y<=0;

3'b100:Y<=0;

3'b101:Y<=1;

3'b110:Y<=1;

3'b111:Y<=1;

default:Y<=0;

endcase

end

endmodule

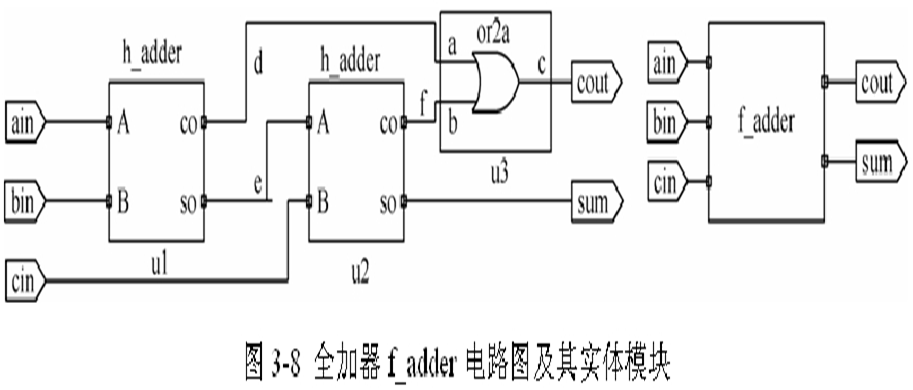

- 代码(老师写的)

(五)利用半加器和或门实现全加器

半加器代码之前已经写过了,下面写一下或门的代码

module or2a(a,b,c);

output c;

input a,b;

assign c=a|b;

endmodule

- 全加器电路图

- 全加器代码

module f_adder(ain,bin,cin,cout,sum);

output sum,cout;

input ain,bin,cin;

wire d,e,f;

h_adder u1(.a(ain),.b(bin),.co(d),.so(e));

h_adder u2(.a(e),.b(cin),.co(f),.so(sum));

or2a u3(.a(d),.b(f),.c(cout));

endmodule

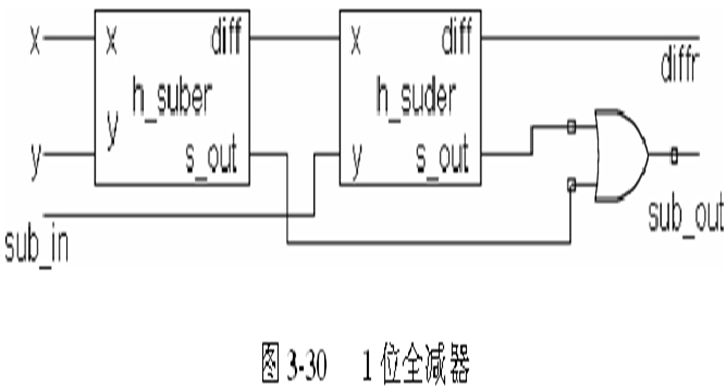

(六)利用半减器和或门实现全减器

- 全减器电路图

- 全减器代码

(注意^是异或,|是或)

module f_suber(x,y,sub_in,diffr,sub_out)

output diffr,sub_out;

input x,y,sub_in;

wire e,f,g;

h_suber u1(.x(x),.y(y),.diff(e),.s_out(g));

h_suber u2(.x(e),.y(sub_in),.diff(diffr),.s_out(f));

assign sub_out=f|g;

endmoudle

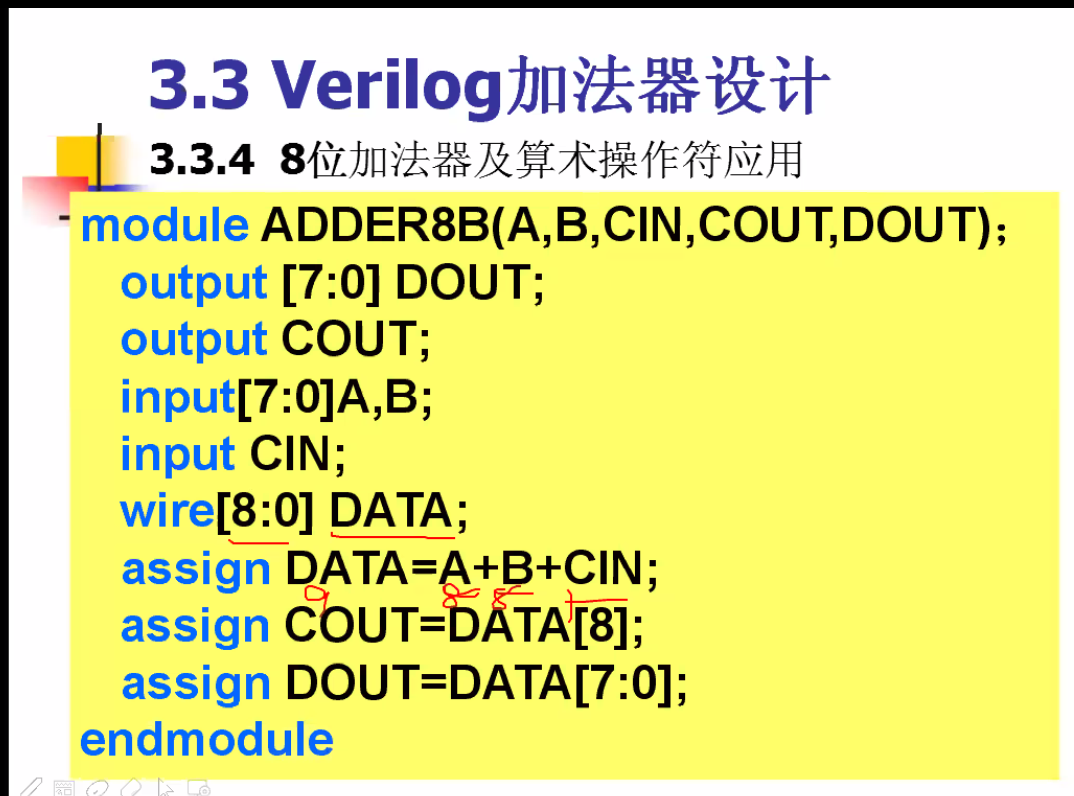

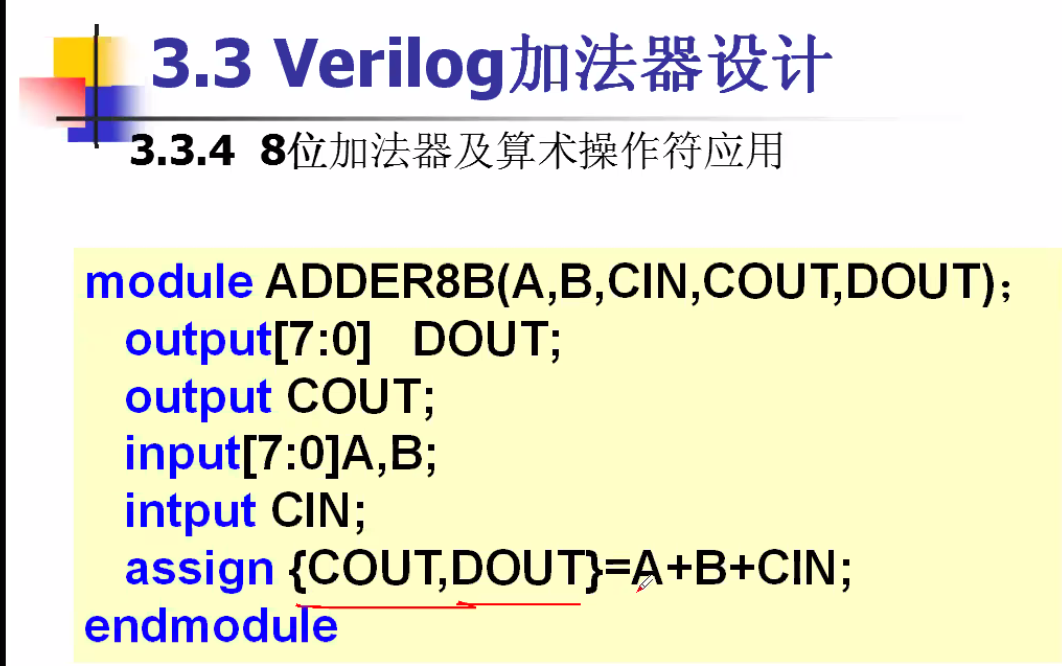

(七)使用算术操作符实现8位加法器

可以使用并位操作符简化

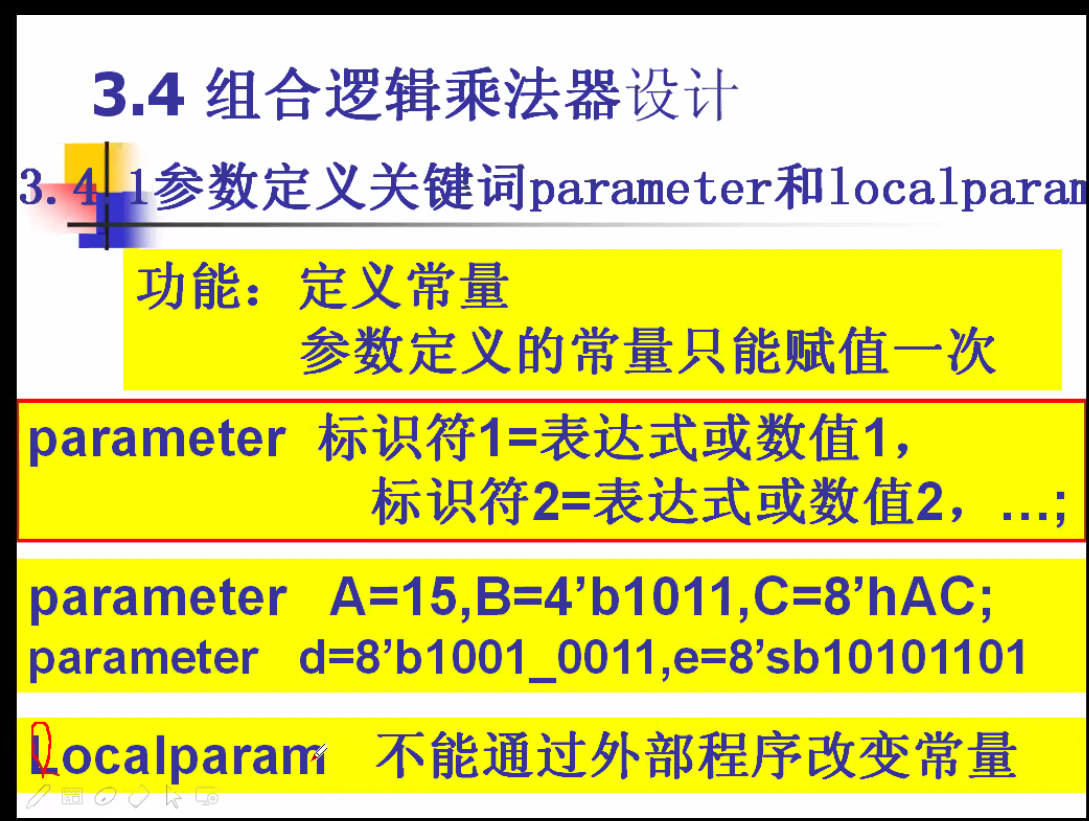

(八)乘法器的设计

在设计乘法器之前先介绍一系列概念

- parameter和localparam

注意:带s是指带符号位

- integer

- 移位操作:左移

移位操作简介

左移

- 移位操作:右移

- 使用for循环实现乘法器

简化写法如下:

- 使用repeat循环实现乘法器

- 使用while循环实现乘法器

(九)练习:一个电路有32位输入,该电路输出输入端口1的个数

- 题目

- 代码

module test(a,y);

parameter S=32;

input[S:1] a;

output[6:1] y;

reg[S:1] at;

reg[6:1] y;

y=0;

at=a;

always@*

begin

repeat(S)

if(a[1]) y=y+1;

at=at>>1;

end

endmodule

(十)参数传递语法

(十一)==和<=的区别

时序逻辑电路使用非阻塞,组合逻辑电路使用阻塞

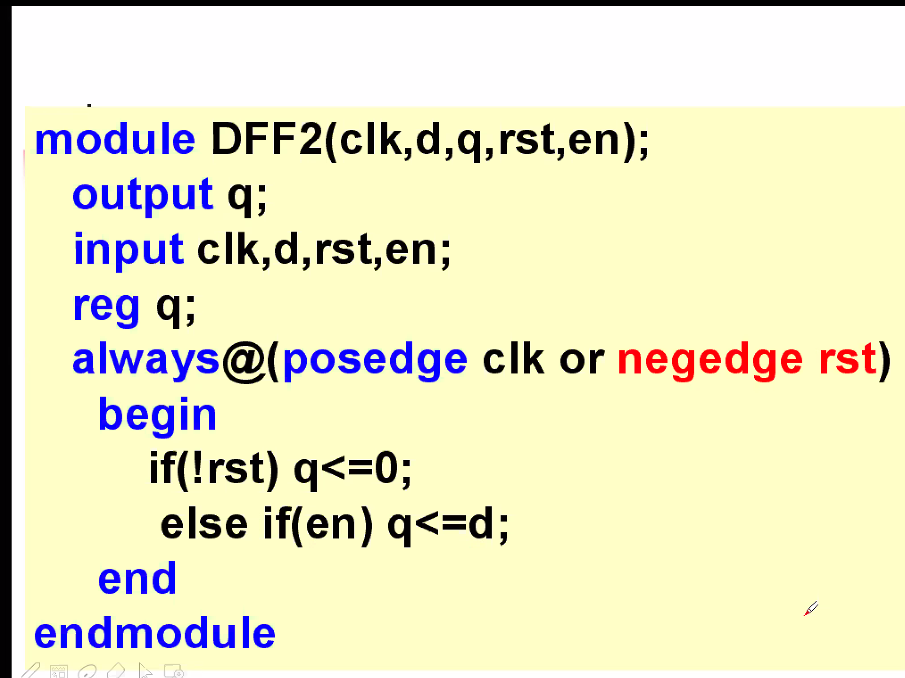

(十二)含异步清0和同步使能控制的D触发器

题目说明:

- 该题目RST是低电平有效,低电平才能实现清0

- 该题目EN是高电平有效

- posedge:下降沿变成上升沿

- negedge:上升沿变成下降沿

- 所以高电平有效就posedge、低电平有效就negedge

- 时钟默认是高电平有效,所以clk使用posedge

代码如下:

代码说明:

- 异步信号优先级比同步信号高,所以同步信号(en)要放在异步信号(rst)的判断之后

- if后面一定要是else if而不能是if(原因百度)

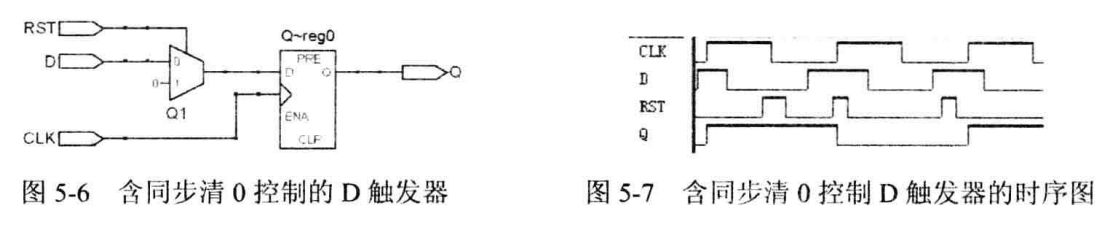

(十三)含同步清0的D触发器

题目说明:

- 上一个题目是异步清0,因为它不受时钟约束;但是本题目是同步清0,必须要CLK配合才可以

- Q1是2选1多路选择器,当RST=1时,选通“1”端的数据0,使数据0进入触发器的D输入端,如果这时候CLK有一个上升沿,就可以把该数据0送往输出端Q,这就实现了清零的功能

代码如下:

代码说明:

- 因为clk是异步信号,优先级较高,所以我们只有当clk处于上升沿时才进行同步信号的判断

- 如果clk处于上升沿时rst正好为高电平,则清零;否则,则保持

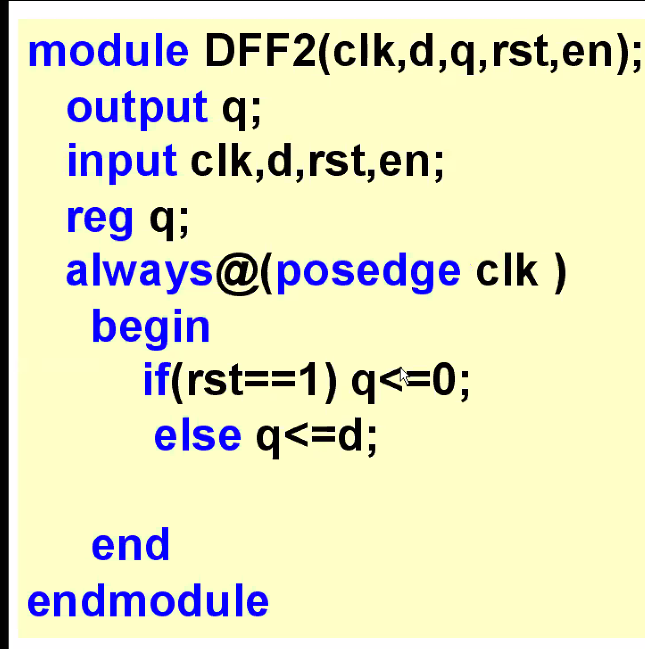

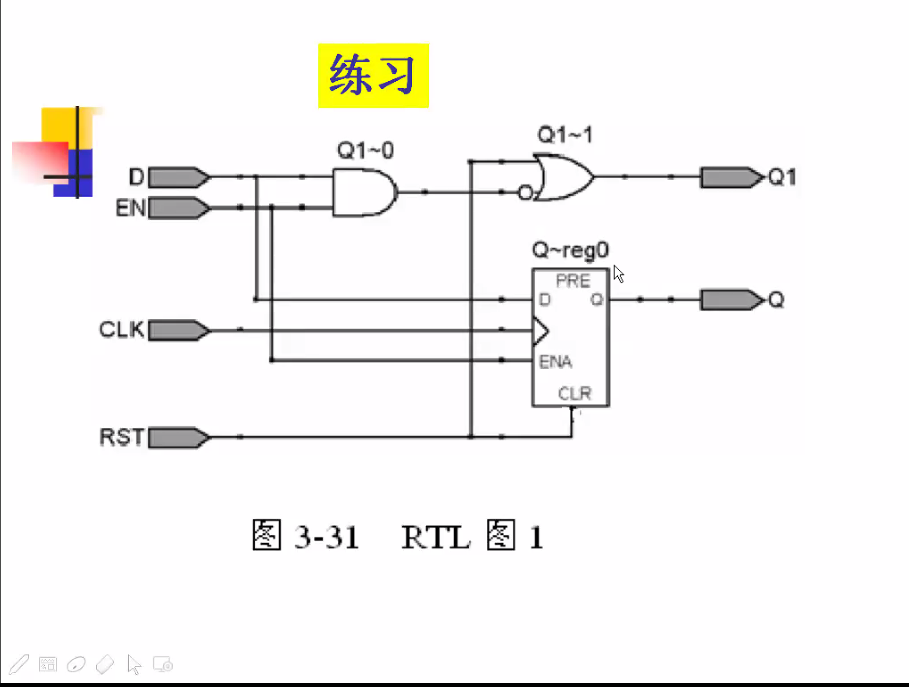

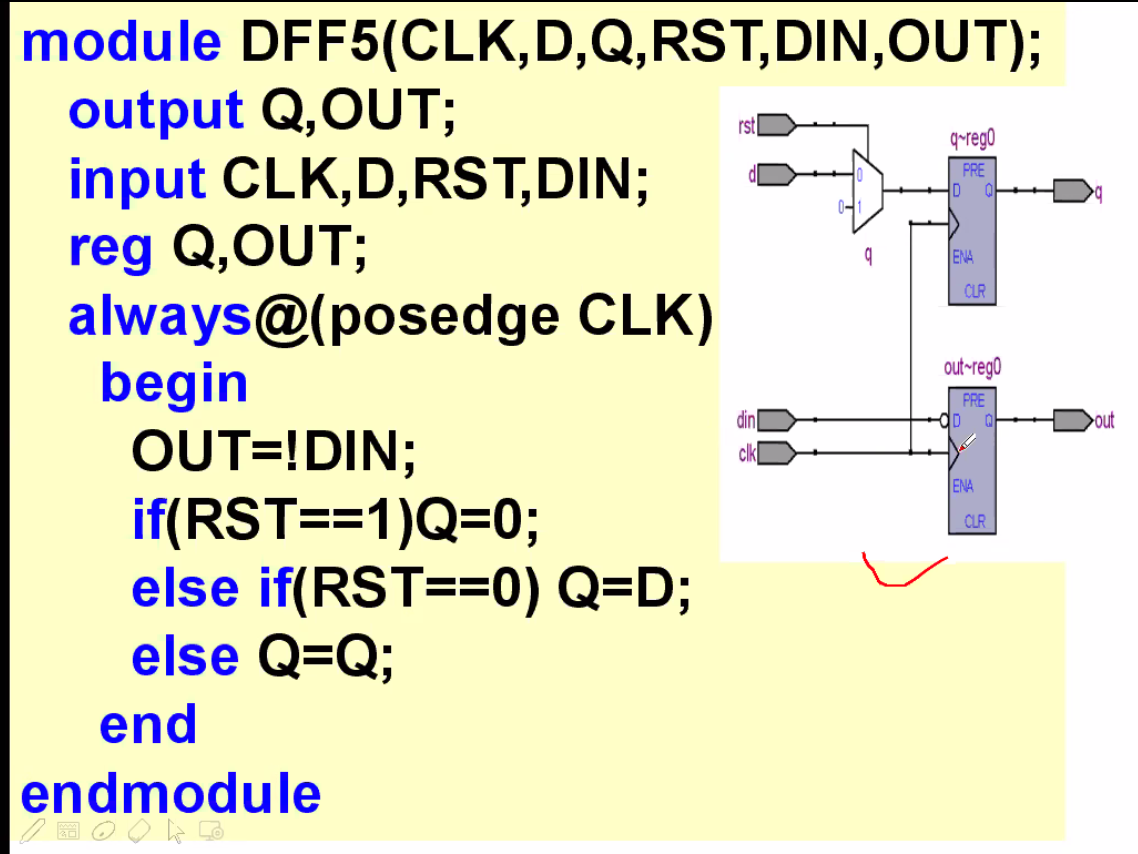

(十四)D触发器的练习题

题目说明:

- 该题目为异步清零和同步使能的D触发器

- RST任意时刻都可以清零

代码如下:

module DFF2(d,en,clk,rst,q1,q);

output q1,q;

input d,en,clk,rst;

reg q;

wire n;

assign n=d&en;

assign q1=(~n)|rst;

always@(posedge clk or posedge rst)

begin

if(rst) q<=0;

else if(en) q<=d;

end

endmodule

(十五)同步清0的例题

注意:考试重点考察同步清零

(十六)时序电路描述的一些特点和规律

注意:考试不考察电平触发,只考察边沿触发

(十七)例题:16进制计数器

说明:16进制计数器(0000~1111)

注意:计数器不需要赋初值,如果初值是1001 就变成1010(无论如何都是在16个状态内循环)

module cnt16(clk,q);

input clk;

output [3:0]q;

reg [3:0]qq;

always@(posedge clk)

qq<=qq+1;

assign q=qq;

endmodule

由于计数器不受控,我们通常加一个异步清零(rst)和同步使能(en)等等去加以控制

其中load为初值,d为中间量

我们假设控制信号(load、en和rst)均高电平有效、load优先级高于en的优先级

module cnt16(clk,q,rst,en,load,d);

input clk,rst,en,load;

input [3:0]d;

output [3:0]q;

reg [3:0]qq;

always@(posedge clk,posedge rst)

if(rst) qq<=0;

else if(load) qq<=d;

else if(en) qq<=qq+1;

else qq<=qq; (en使能信号没有使能,只能保持原样了)

assign q=qq;

endmodule

加上溢出信号

module cnt16(clk,q,rst,en,load,d,count);

input clk,rst,en,load;

input [3:0]d;

output [3:0]q;

output count;

reg [3:0]qq;

always@(posedge clk,posedge rst)

if(rst) qq<=0;

else if(load) qq<=d;

else if(en) qq<=qq+1;

else qq<=qq;

assign q=qq;

assign count=(qq==4'b1111);

endmodule

(十八)练习:60进制计数器

我们最好是加上count

刚才的16进制计数器因为4个1刚好是15,所以无需加以判断,但是6个1并不等于59

module cnt60(clk,q,rst,en,load,d,count);

input clk,rst,en,load;

input [5:0]d;

output [5:0]q;

output count;

reg [5:0]qq;

always@(posedge clk,negedge rst)

if(!rst) qq<=0;

else if(!load) qq<=d;

else if(!en)

if(qq<59) qq<=qq+1;

else qq<=0;

else qq<=qq;

assign q=qq;

assign count=(qq==6'b111011);

endmodule

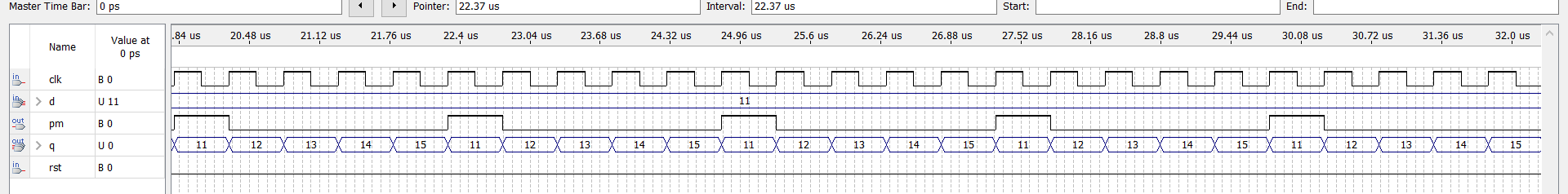

(十九)基于16进制计数器加以增加模可控的功能

module cnt16(clk,q,rst,d,pm);

input clk,rst;

input [3:0]d;

output [3:0]q;

output reg pm;

reg [3:0]qq;

wire load;

always@(posedge clk,posedge rst)

begin

if(rst) begin qq<=0;pm<=0;end

else if(load) begin qq<=d;pm<=1;end

else begin qq<=qq+1;pm<=0;end

end

assign load=(qq==4'b1111);

assign q=qq;

endmodule

(二十)练习:设计一个2分频的分频器

module div_2(q,clk,reset);

output q;

input reset;

input clk;

reg q;

always@(posedge clk or posedge reset)

if(reset)

q<=1'b0;//复位置零

else

q<=~q;//否则q信号翻转

endmodule

最后

以上就是害怕宝马最近收集整理的关于Verilog学习笔记文章目录半加器半减器4选1多路选择器举重裁判电路(五)利用半加器和或门实现全加器(六)利用半减器和或门实现全减器(七)使用算术操作符实现8位加法器(八)乘法器的设计(九)练习:一个电路有32位输入,该电路输出输入端口1的个数(十)参数传递语法(十一)==和<=的区别(十二)含异步清0和同步使能控制的D触发器(十三)含同步清0的D触发器(十四)D触发器的练习题(十五)同步清0的例题(十六)时序电路描述的一些特点和规律(十七)例题:16进制计数器(十八)练习:60进制计数器(十的全部内容,更多相关Verilog学习笔记文章目录半加器半减器4选1多路选择器举重裁判电路(五)利用半加器和或门实现全加器(六)利用半减器和或门实现全减器(七)使用算术操作符实现8位加法器(八)乘法器内容请搜索靠谱客的其他文章。

发表评论 取消回复