同步计数器

- 同步计数器

- 同步二进制计数器(控制输入端T)

- 扩展

- 同步二进制计数器(控制时钟信号)

- 同步二进制减法计数器

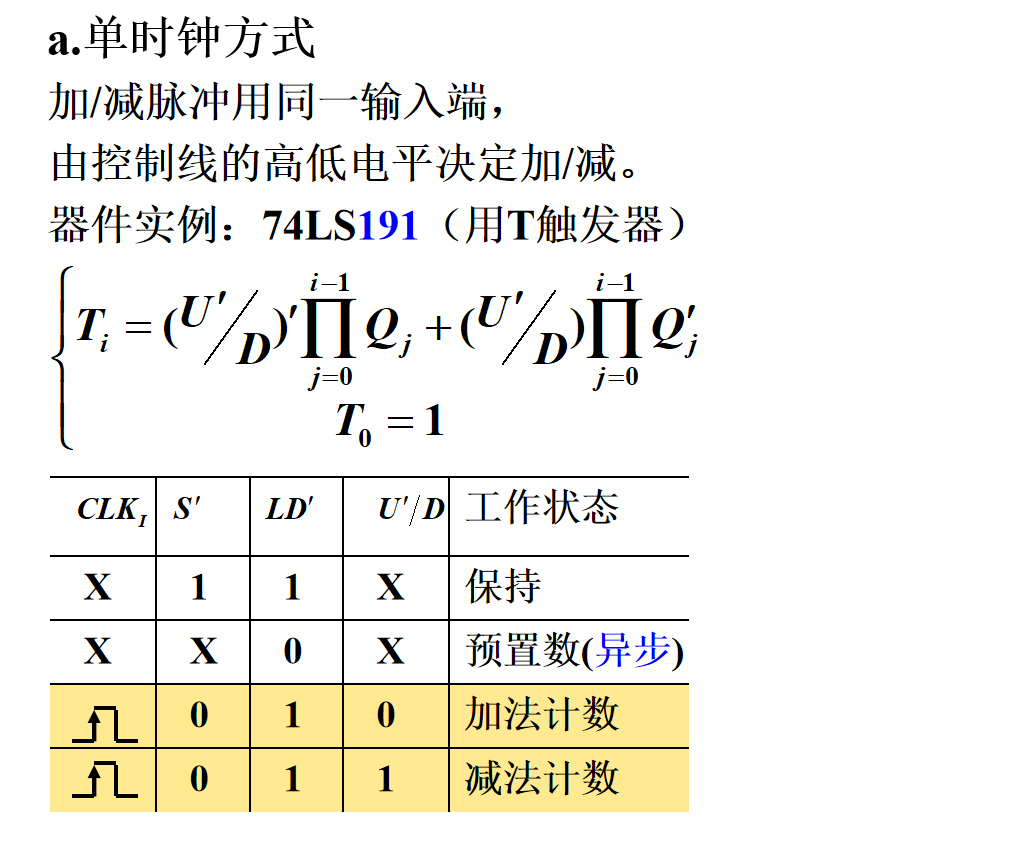

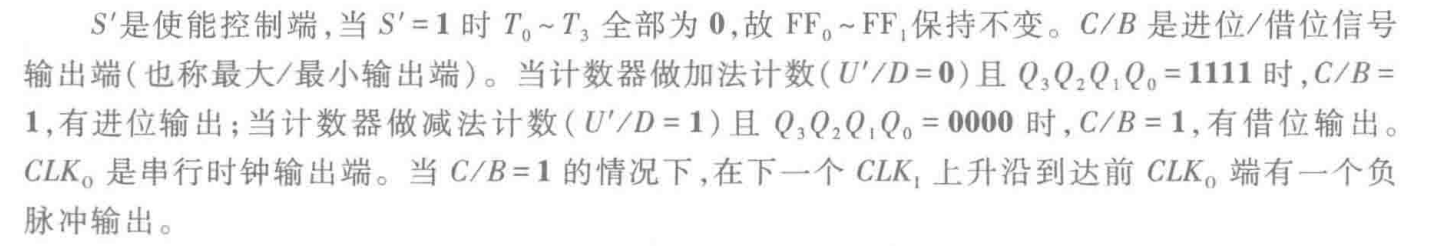

- 同步加减法计数器

- 单时钟结构

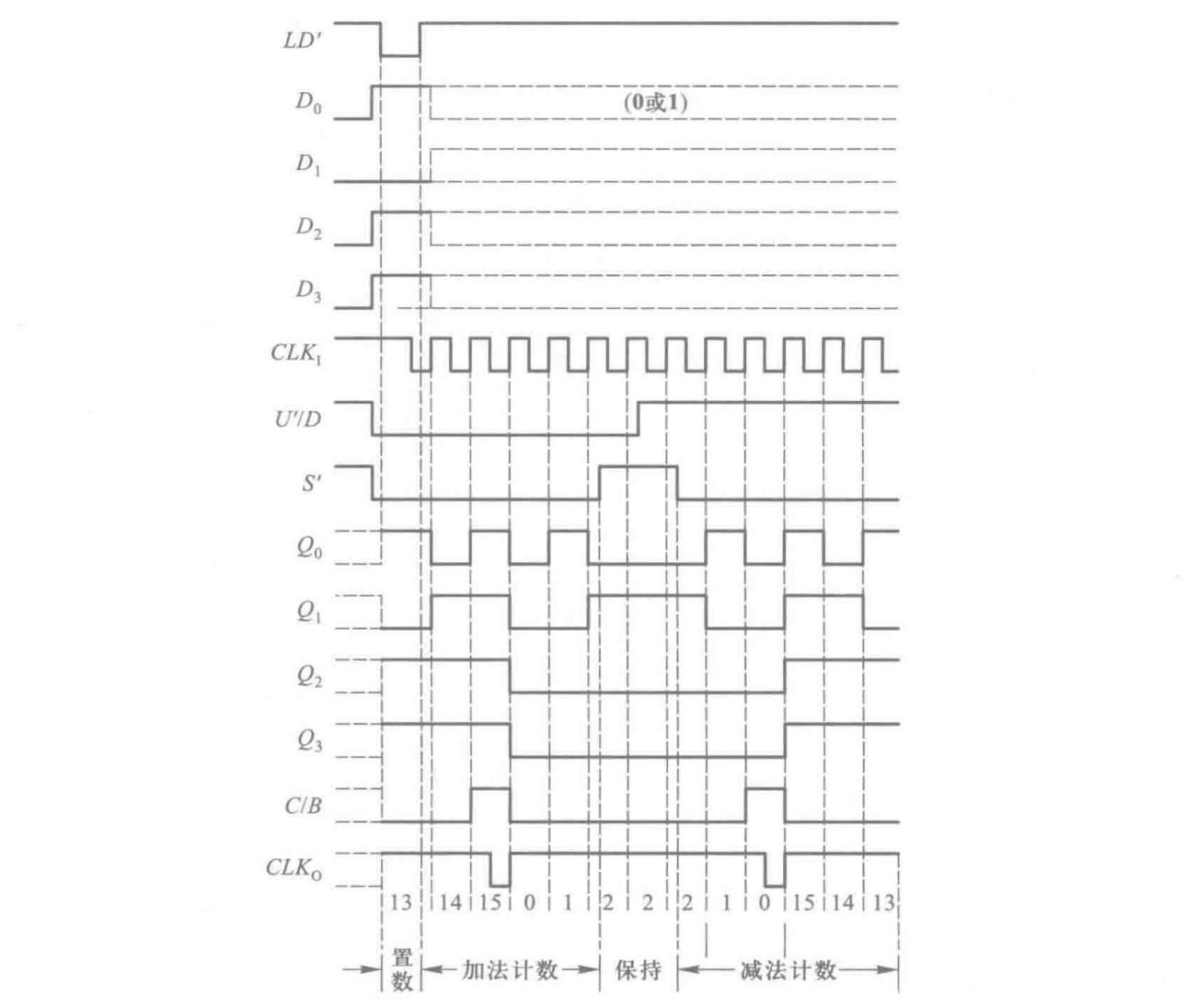

- 双时钟方式

- 同步十进制加法计数器

- 同步十进制减法计数器

功能

记忆输入脉冲的个数。

应用

用于计数、分频、定时、产生节拍脉冲等。

种类

按时钟分:

同步(触发器都受同一时钟脉冲的控制,触发器的翻转是同时的,故被称为“同步计数器”。)、

异步(触发器的翻转有先有后,不是同时发生的,故被称为“异步计数器”)

数字增减:加法、减法、可逆

计数容量:二进制、十进制、任意进制

数字编码:二进制、二-十进制、循环码…

同步计数器

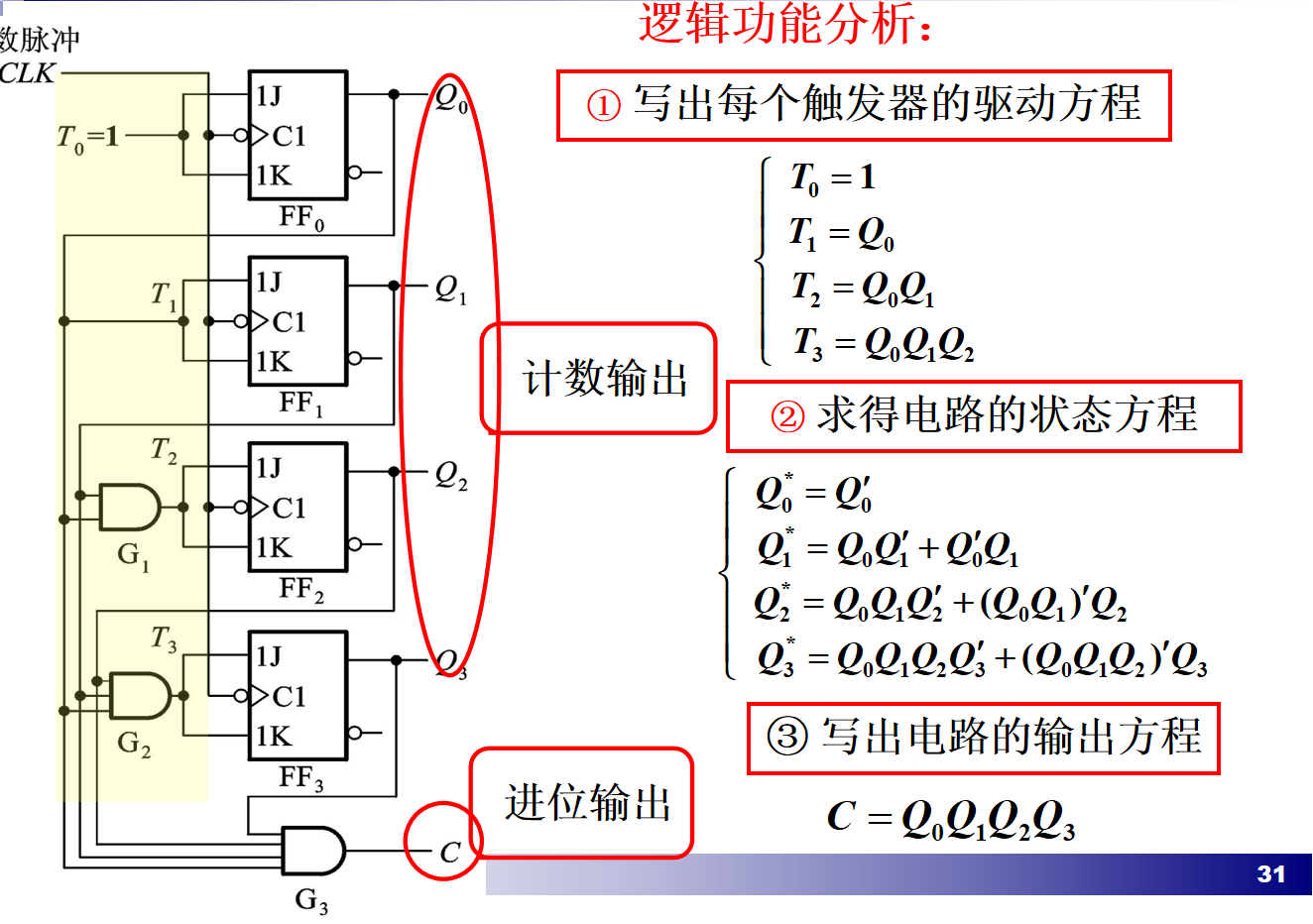

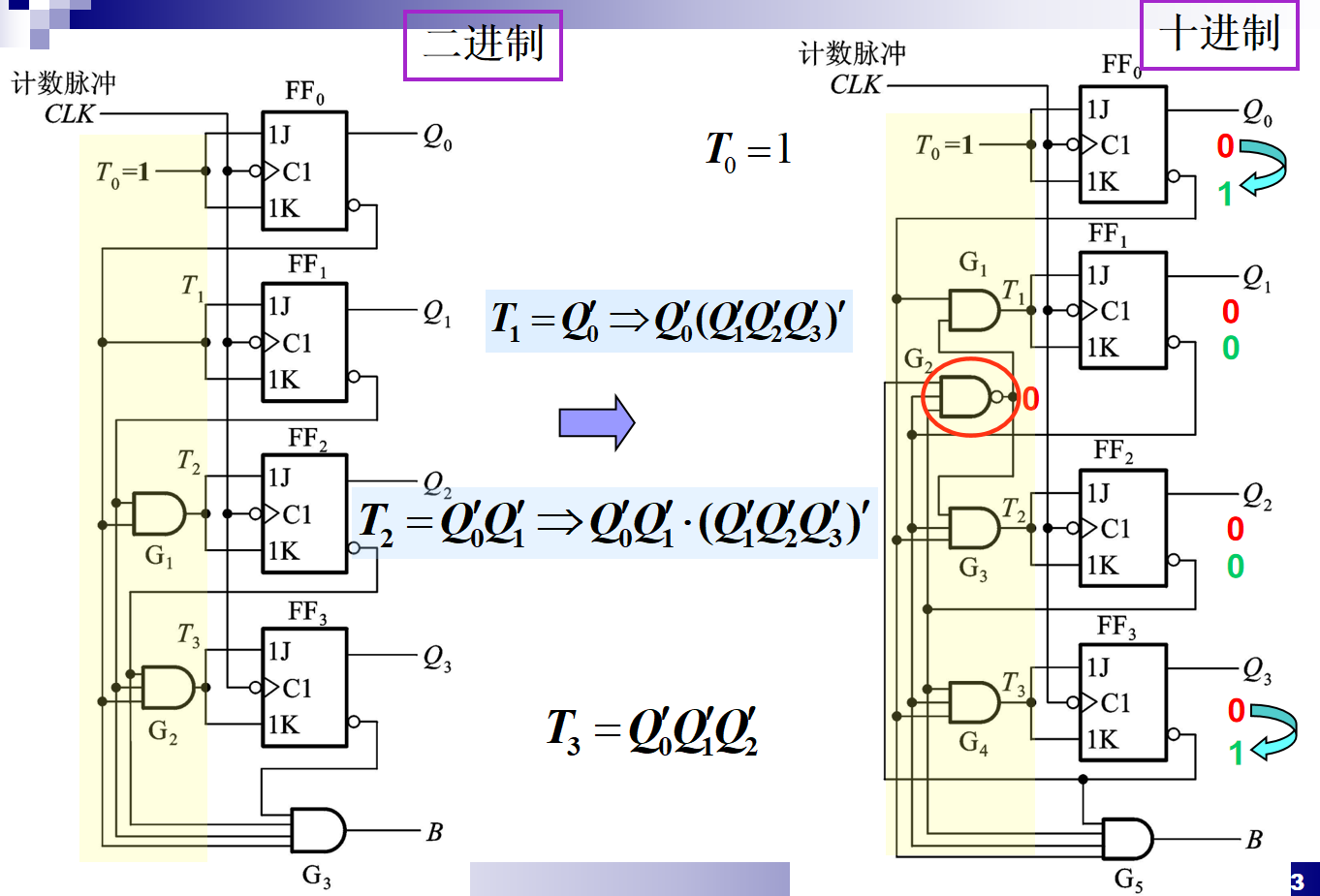

同步二进制计数器(控制输入端T)

原理:根据二进制加法运算规则可知,在多位二进制数末位加1,若第i位以下皆为1时,则第i位应翻转。由此得出规律,若用T触发器构成计数器,则第i位触发器输入端Ti的逻辑式应为:

由JK触发器组成的T触发器。

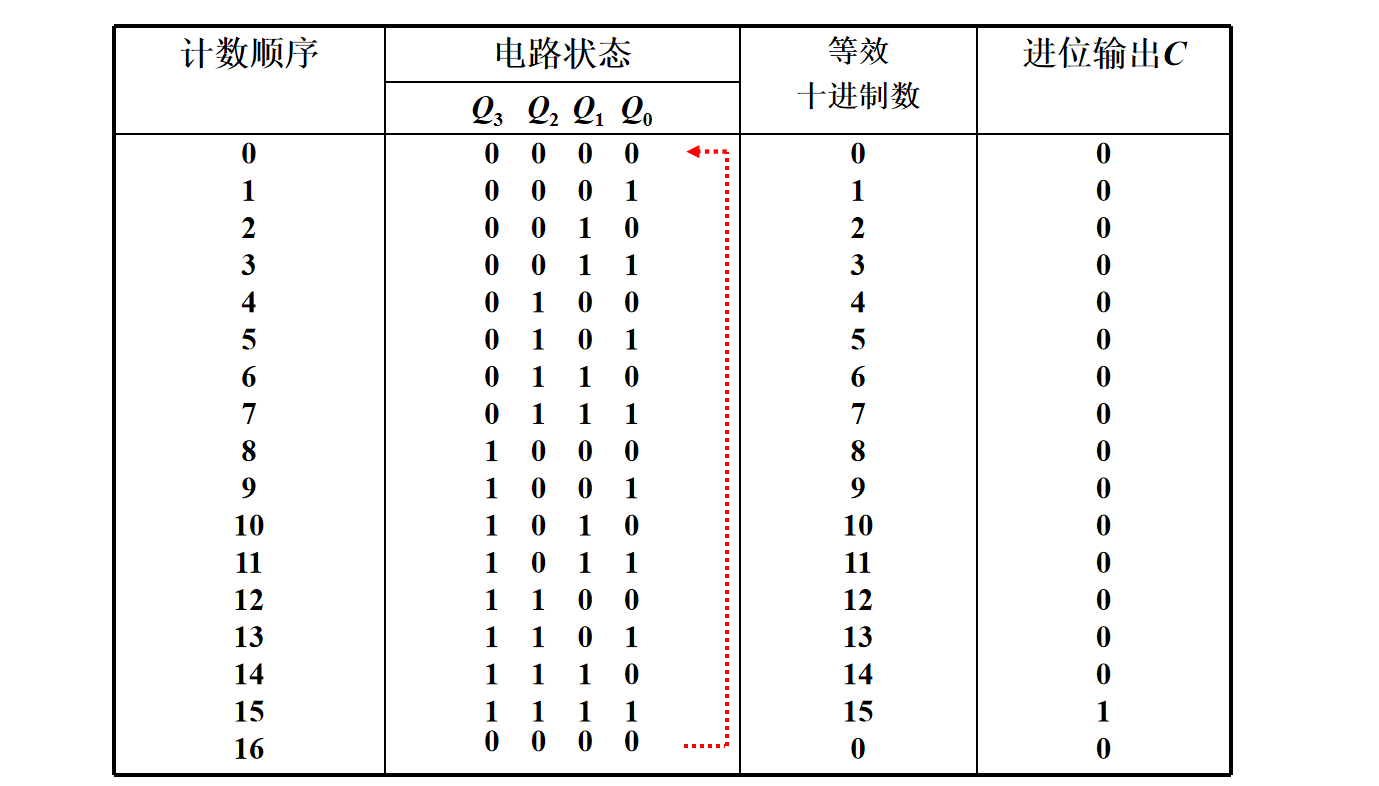

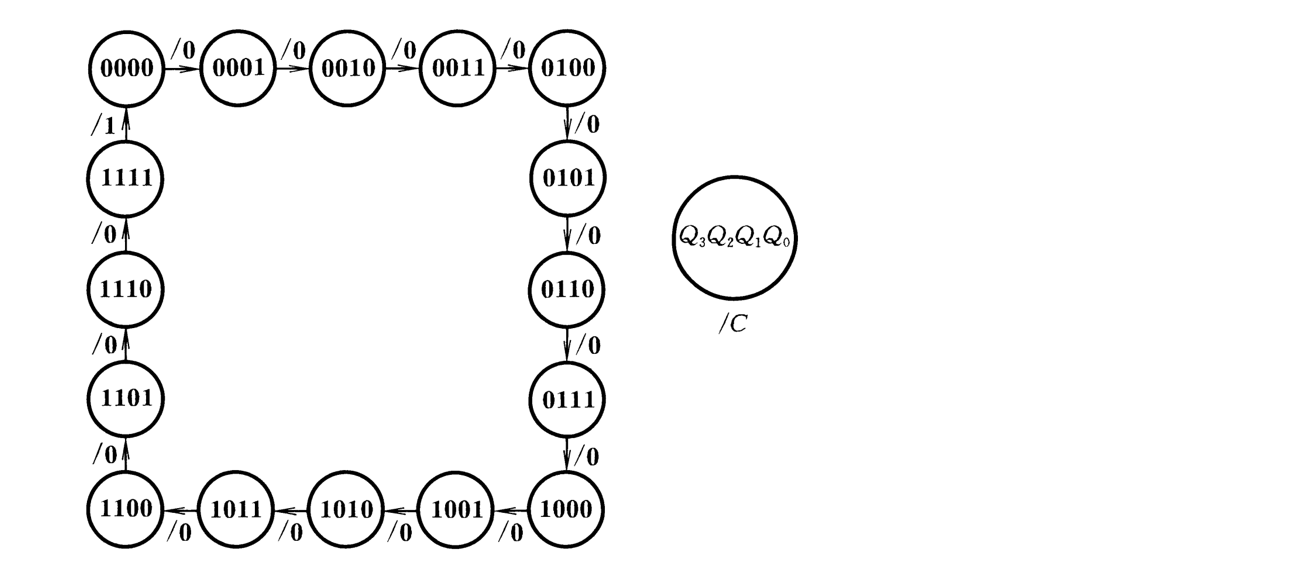

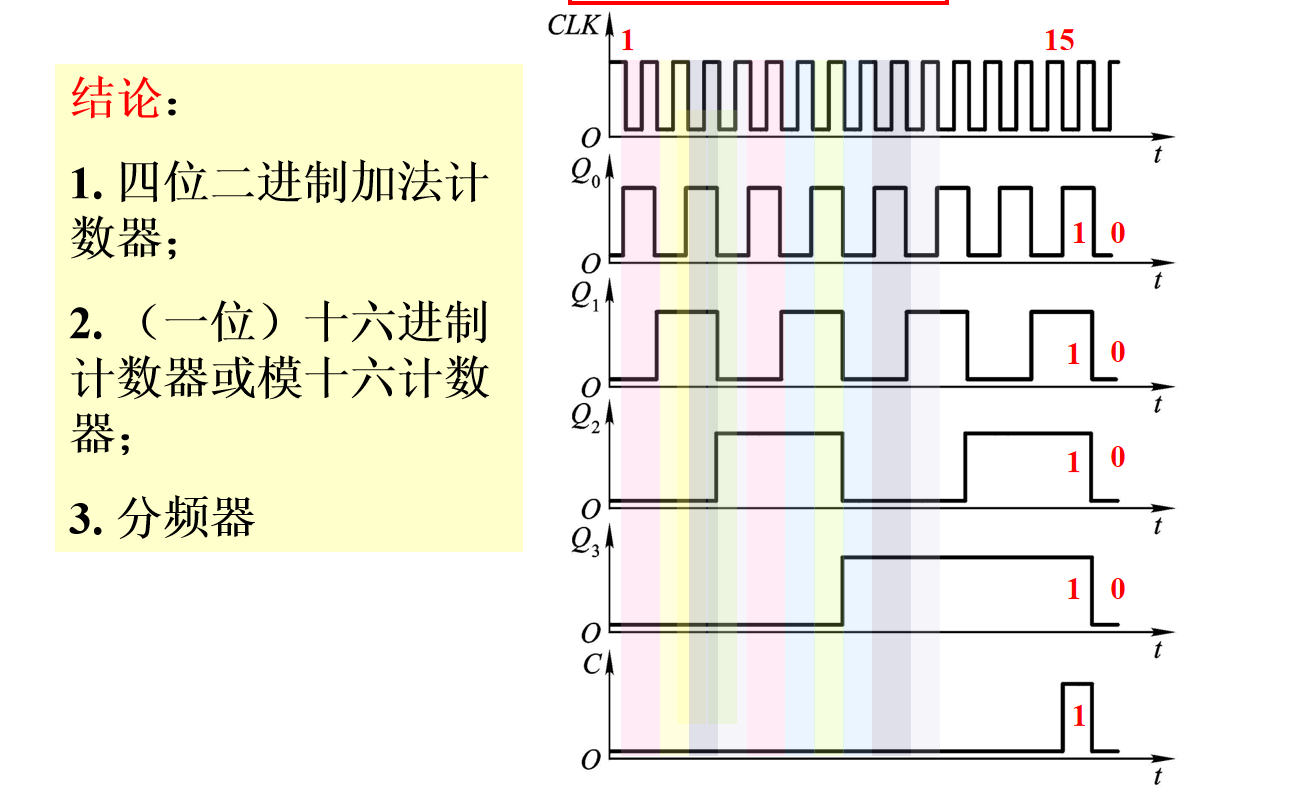

1.其实,由时序图也可以看出,Q0、Q1、Q2、Q3输出的脉冲频率依次为1/2f0 1/4f0 1/8f0 1/16f0

也就是说,它可以实现分频功能,我们称其为分频器。

2.每输入16个脉冲计数器实现一次工作循环,并在Q3产生一个进位信号。

称为16进制计数器。

扩展

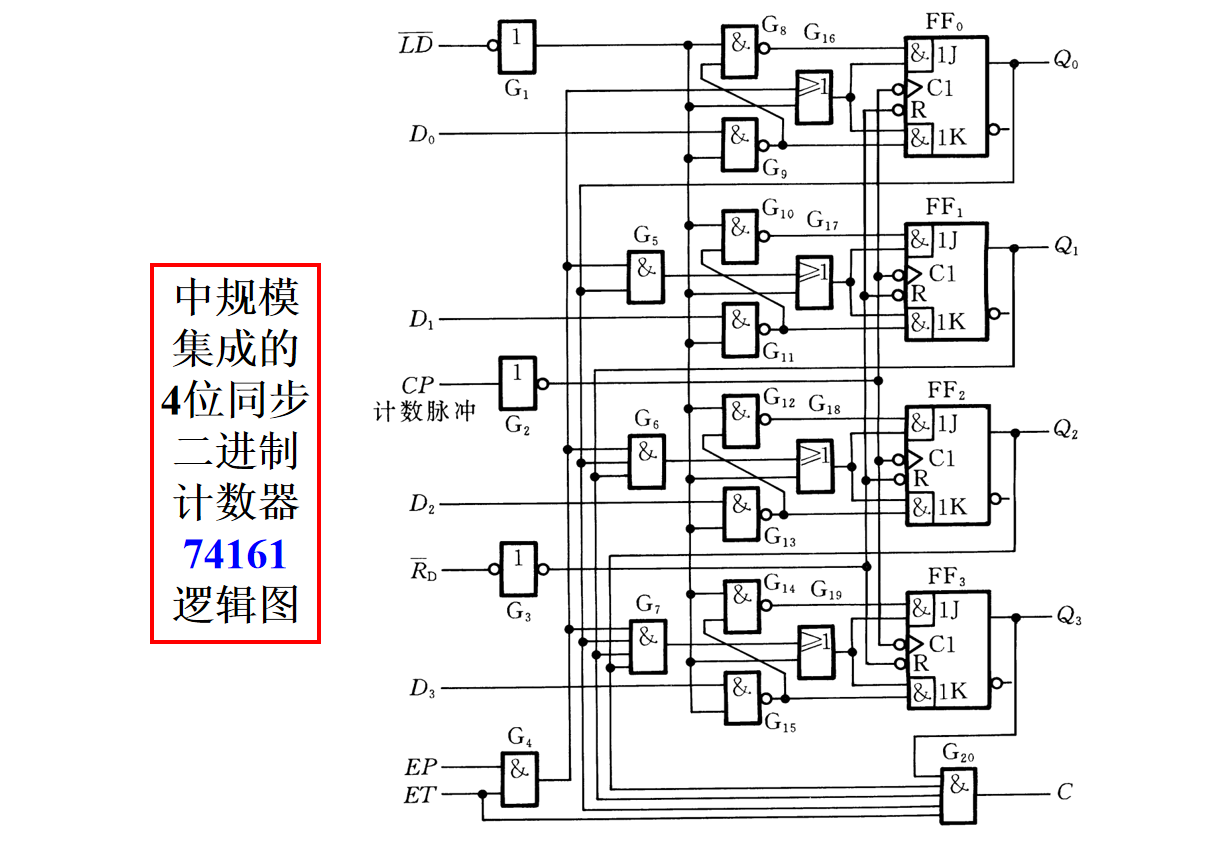

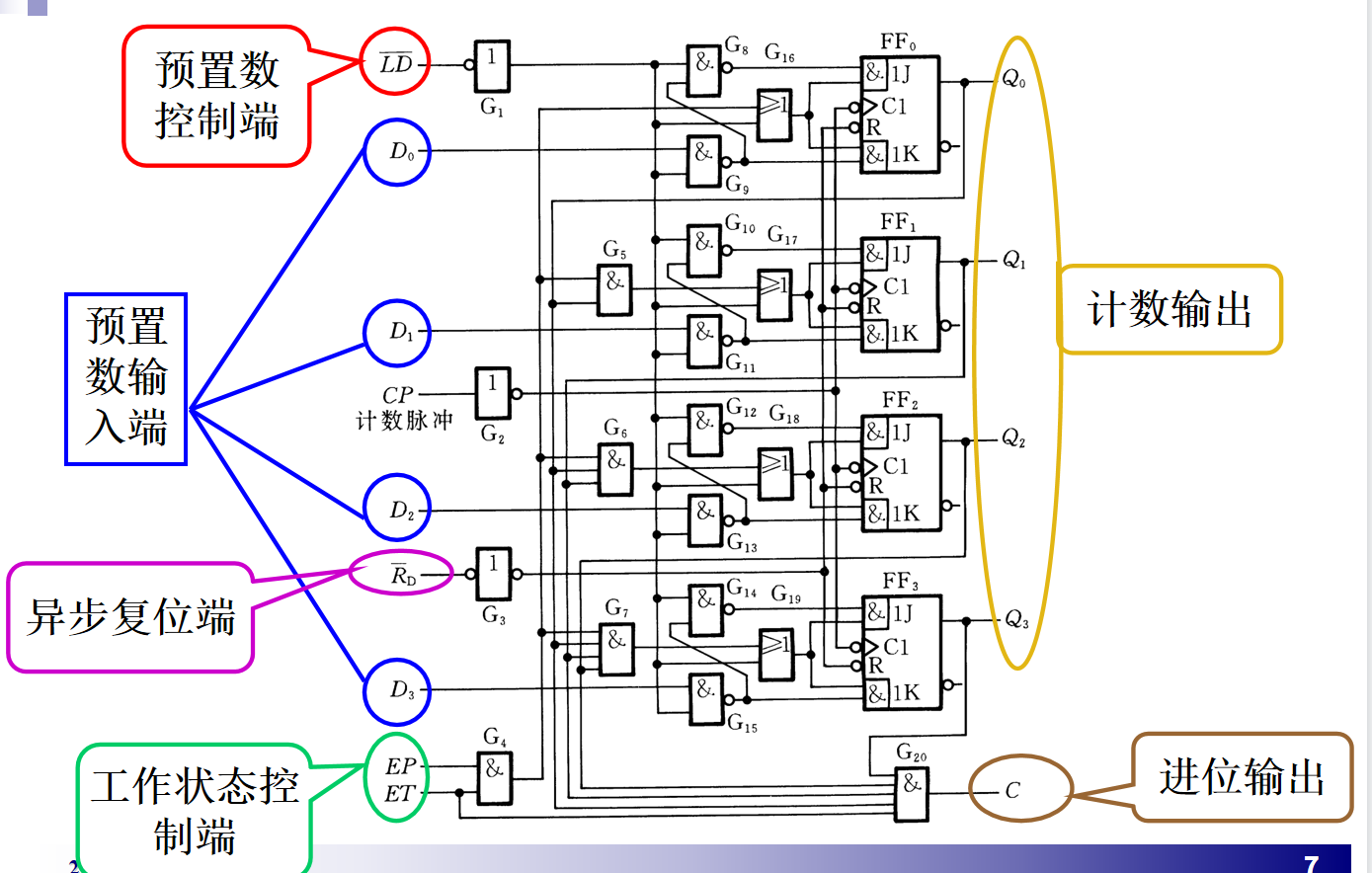

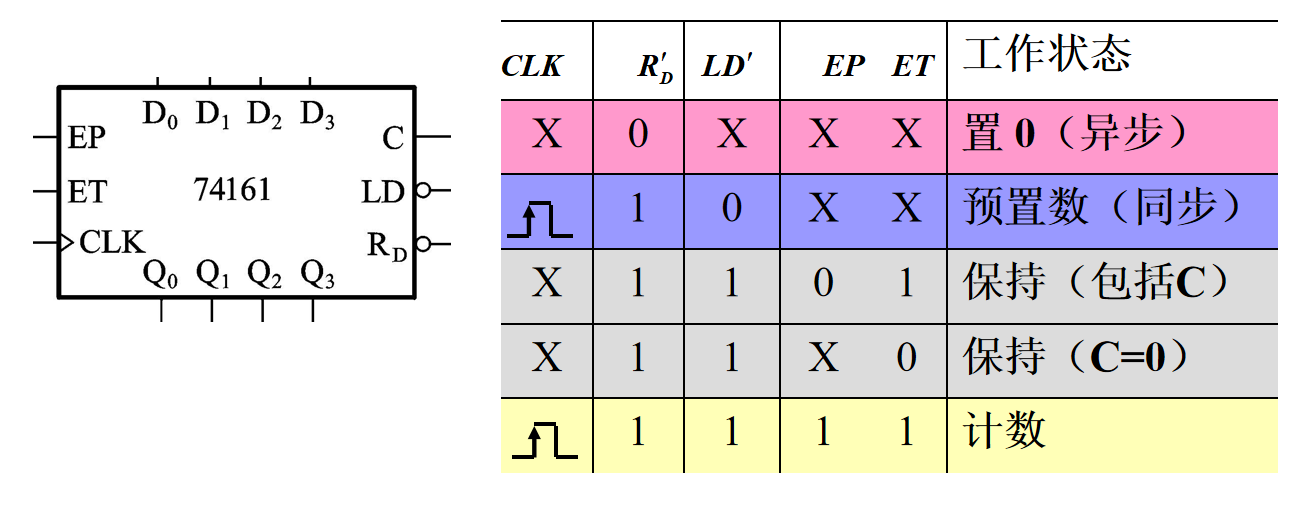

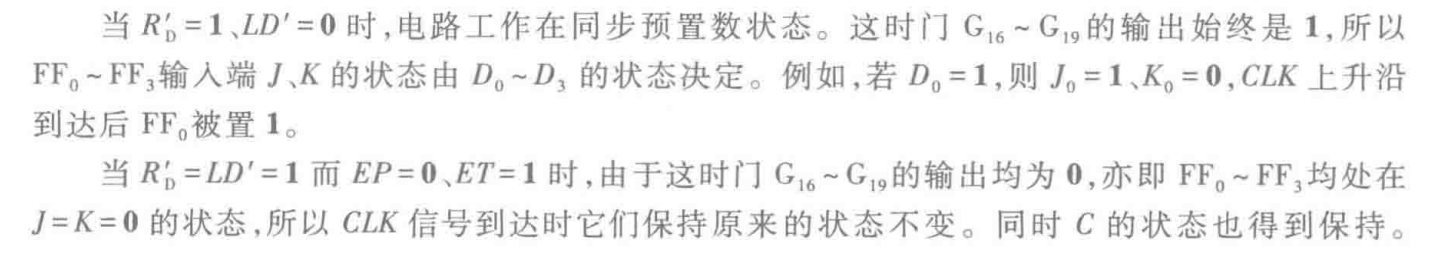

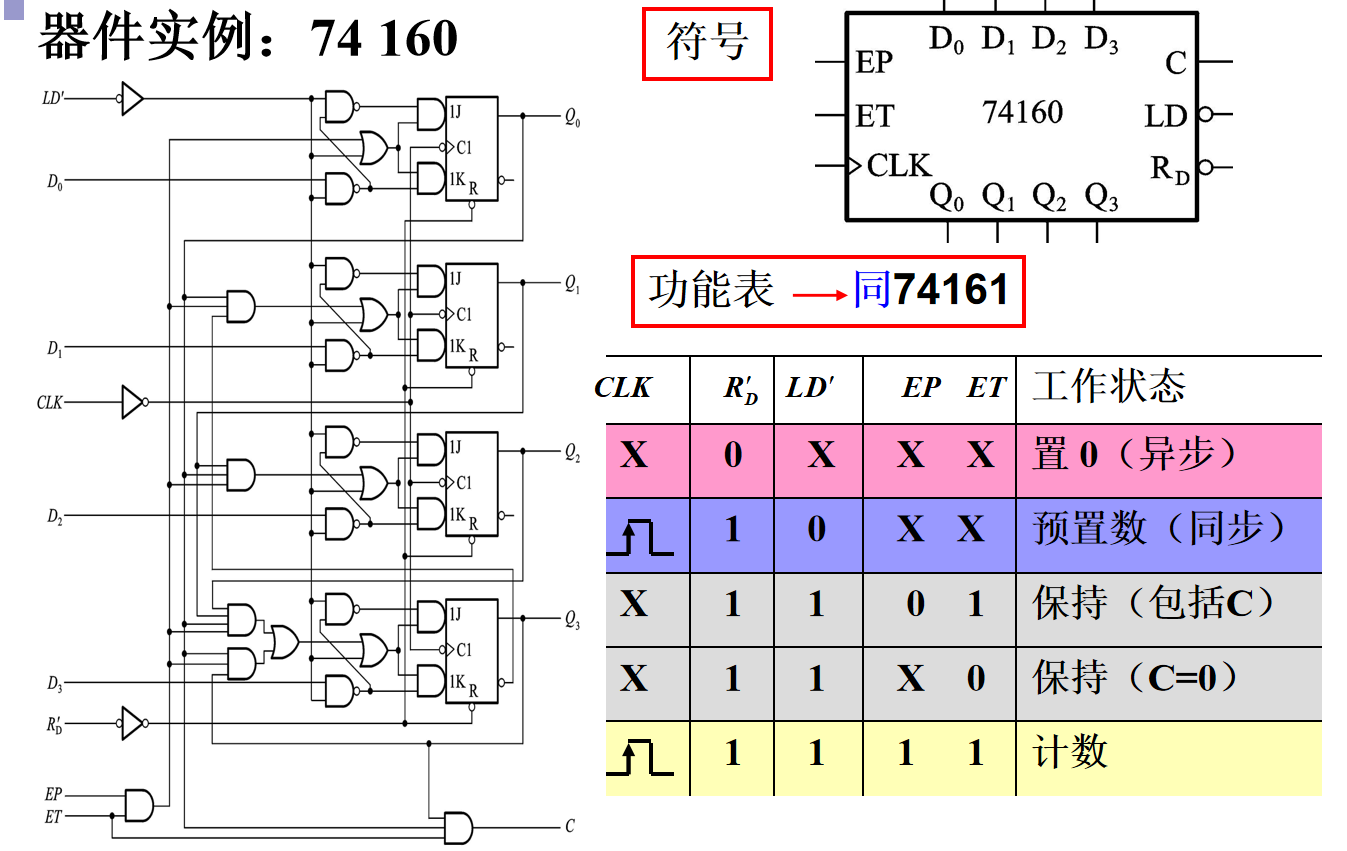

但在实际生产的计数器芯片中,往往会加入一些控制电路。

这个电路除了二进制加法计数功能,还有预置数、保持和异步置0功能

置数是指预置数,在计数器的使用中,有时候需要预先设定为一个值,然后让计数器从这个值开始跑,这就是(预)置数。

预置数是动宾结构把输出数给置成准备开始计数的初始数的意思;预置数状态是指输出Q和由输入D决定(计数器时Q和D的值一样)。输出由输入决定在组合逻辑电路中没错,但在时序电路中就要小心了,时序电路中有很多状态控制端常常可以封锁输入让输入不起作用的,这时候输出就不是由输入决定了。比如计数器不在预置数状态时是来一次技术脉冲输出加1,和输入端D没关系;只有当在预置数状态输出端Q才由D决定(此时Q和D的值一样)。

此外,有些 同步计数器采用同步置0方式,此时,RD‘出现低电平后要等下一个CLK时钟信号到来后才能将触发器置0。

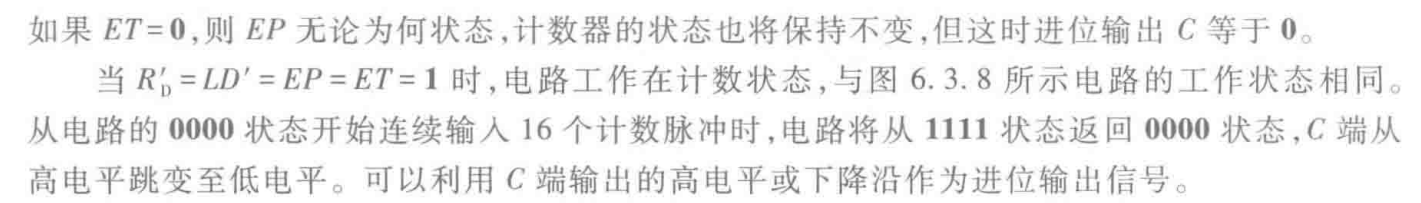

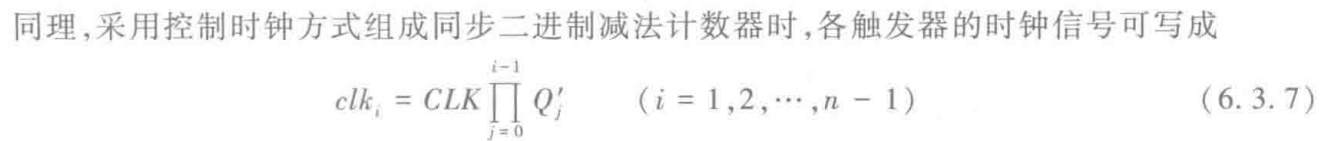

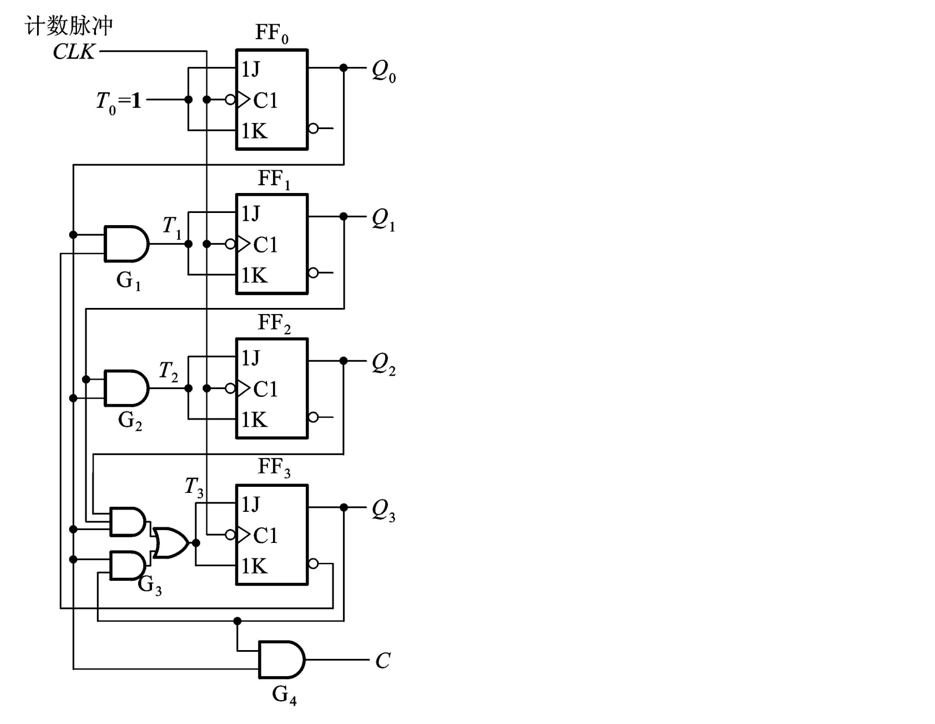

同步二进制计数器(控制时钟信号)

由T触发器构成的4位同步二进制计数器,每个触发端的输入端恒为1,则只要Cl端每加一个时钟脉冲,则触发器就要翻转一次。由图可见,除FF0外,只有低位触发器全为1时,CLK才能通过G1G2G3进入触发器输入端。

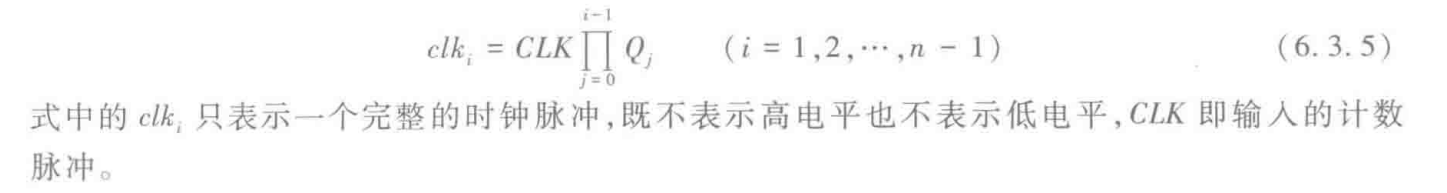

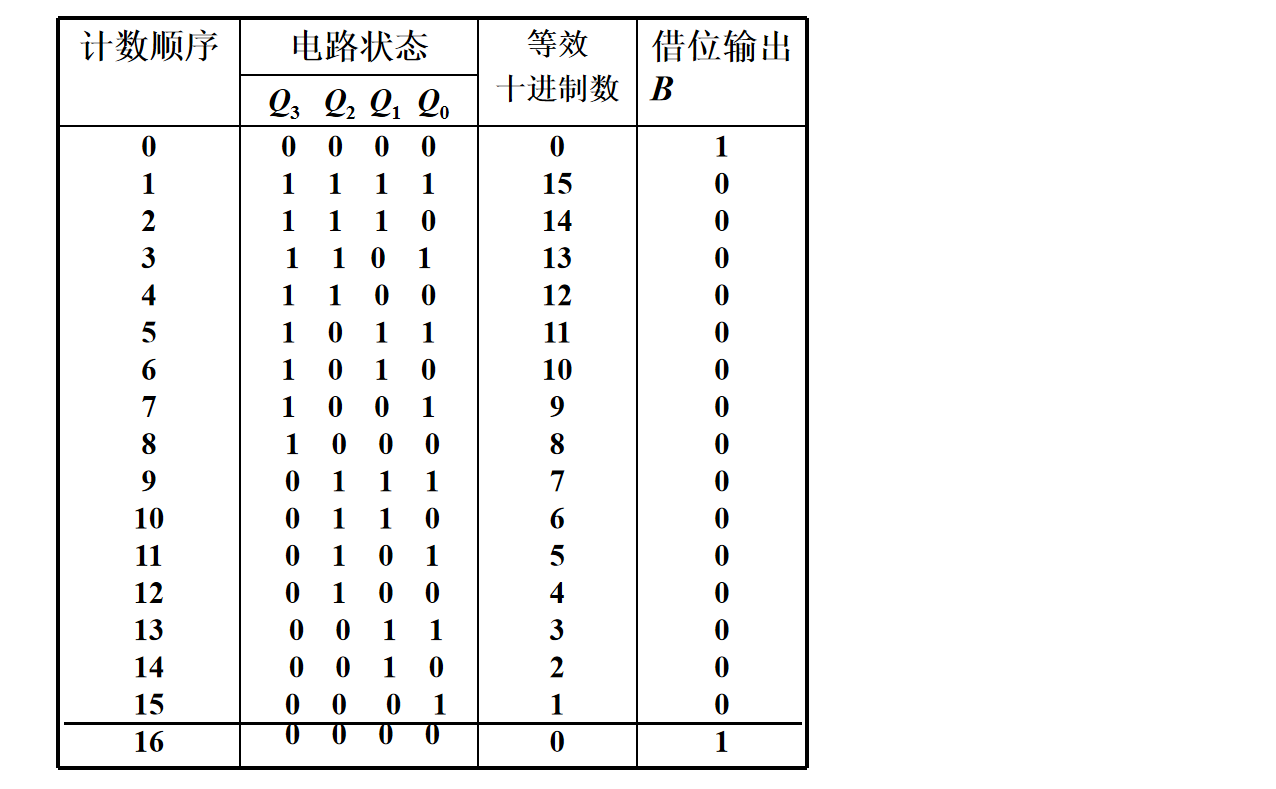

同步二进制减法计数器

其中的T触发器是由JK接在一起实现,前面也讲过如何通过JK触发器改造各种触发器的原理。

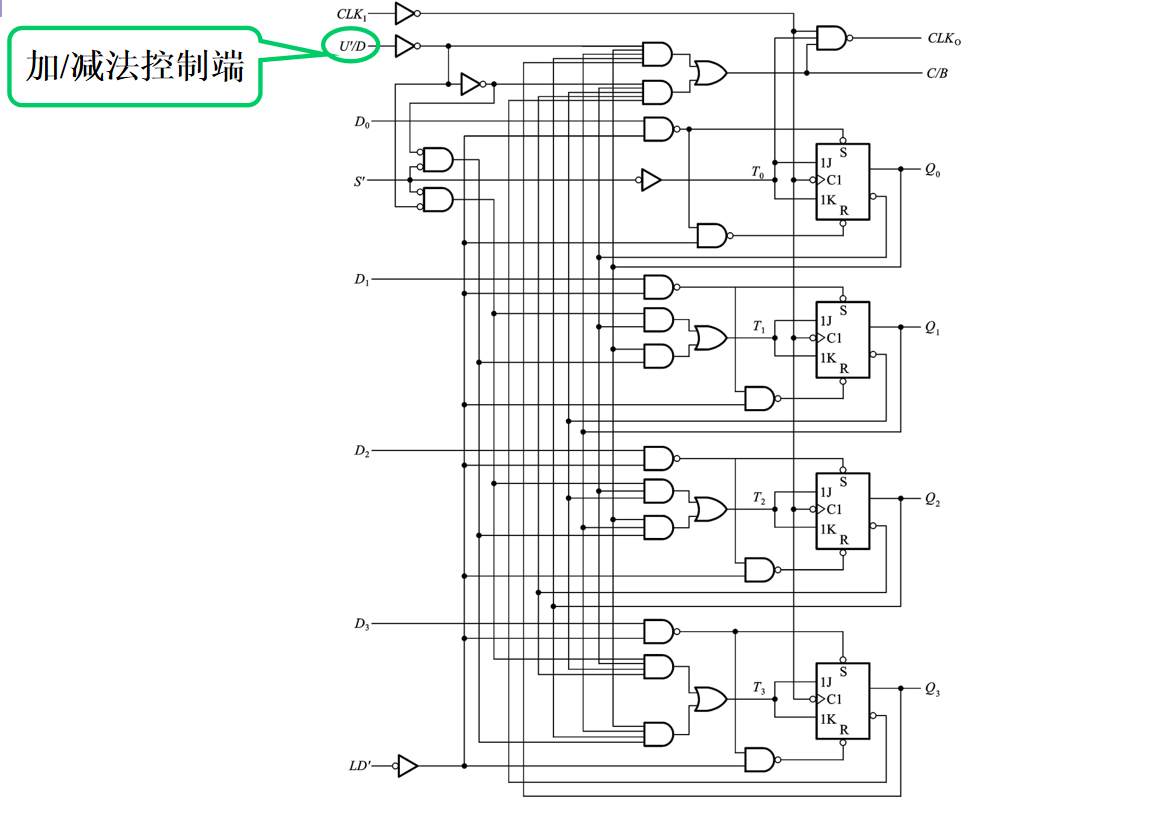

同步加减法计数器

单时钟结构

在某些场合,既要求能递增计数,又要求能递减计数。

LD’=0,电路处于预置数状态,D0~D3数据被置入触发器中,而不受时钟信号的控制。因此,它的预置数是异步式的。

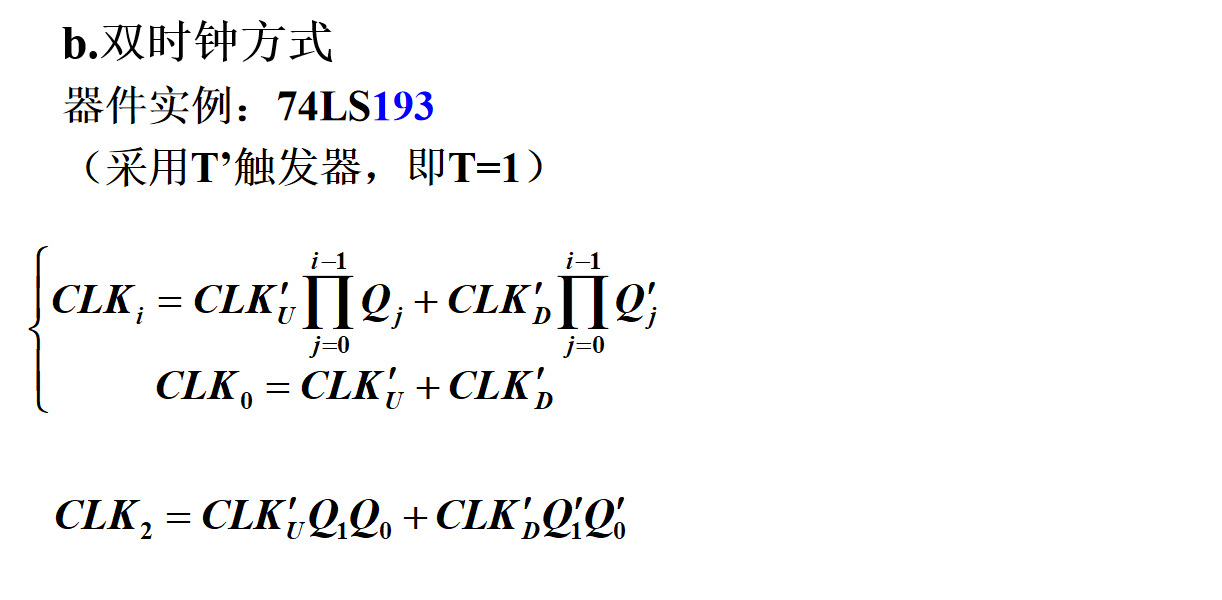

双时钟方式

意思是加法计数脉冲和减法计数脉冲来自两个不同的时钟源。

4个触发器均工作在T=1状态,只要有时钟信号加在触发器上就翻转。

CLKU有脉冲输入,做加法计数;

CLKD有脉冲输入,做减法计数。

但加在两端的计数脉冲时间应该错开。

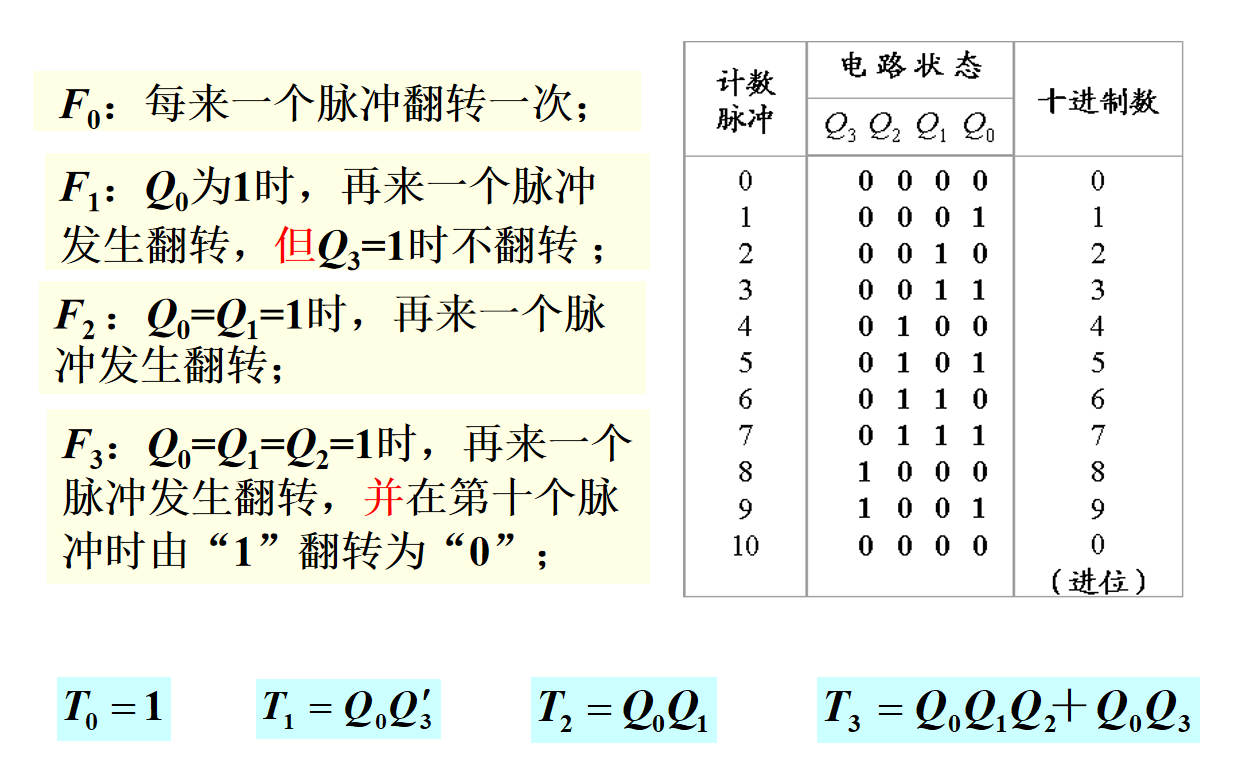

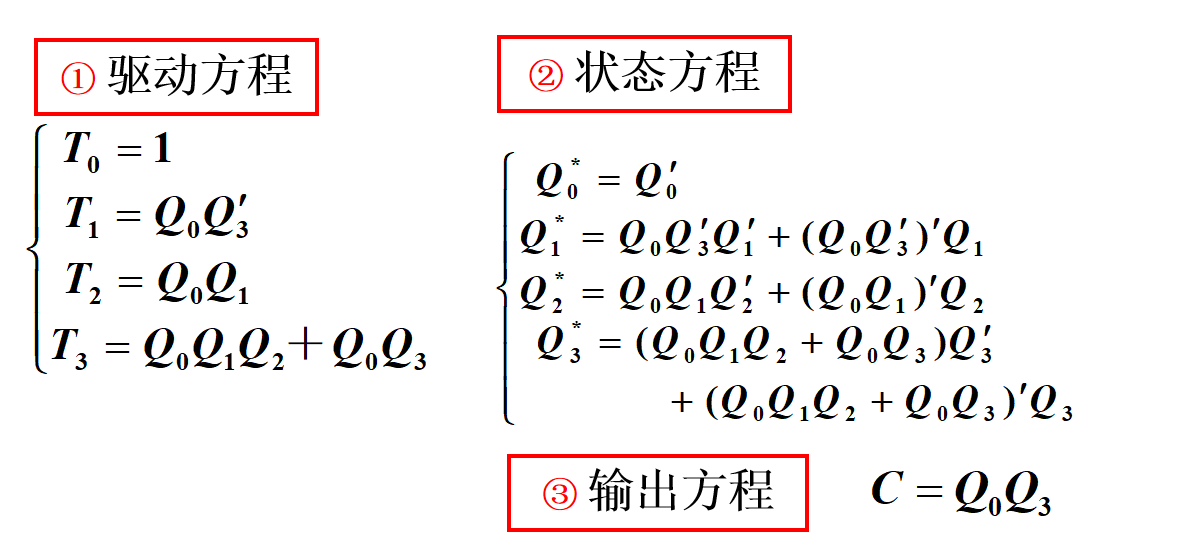

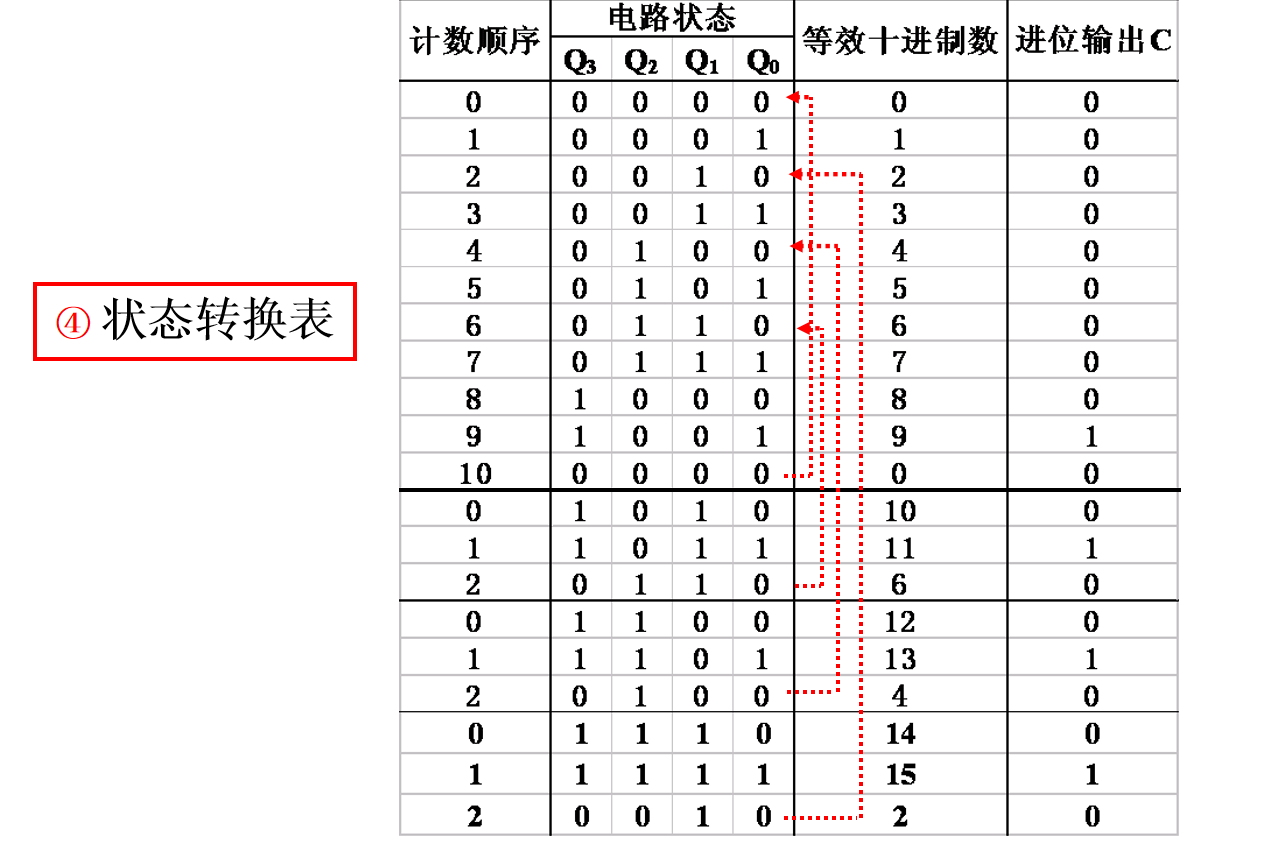

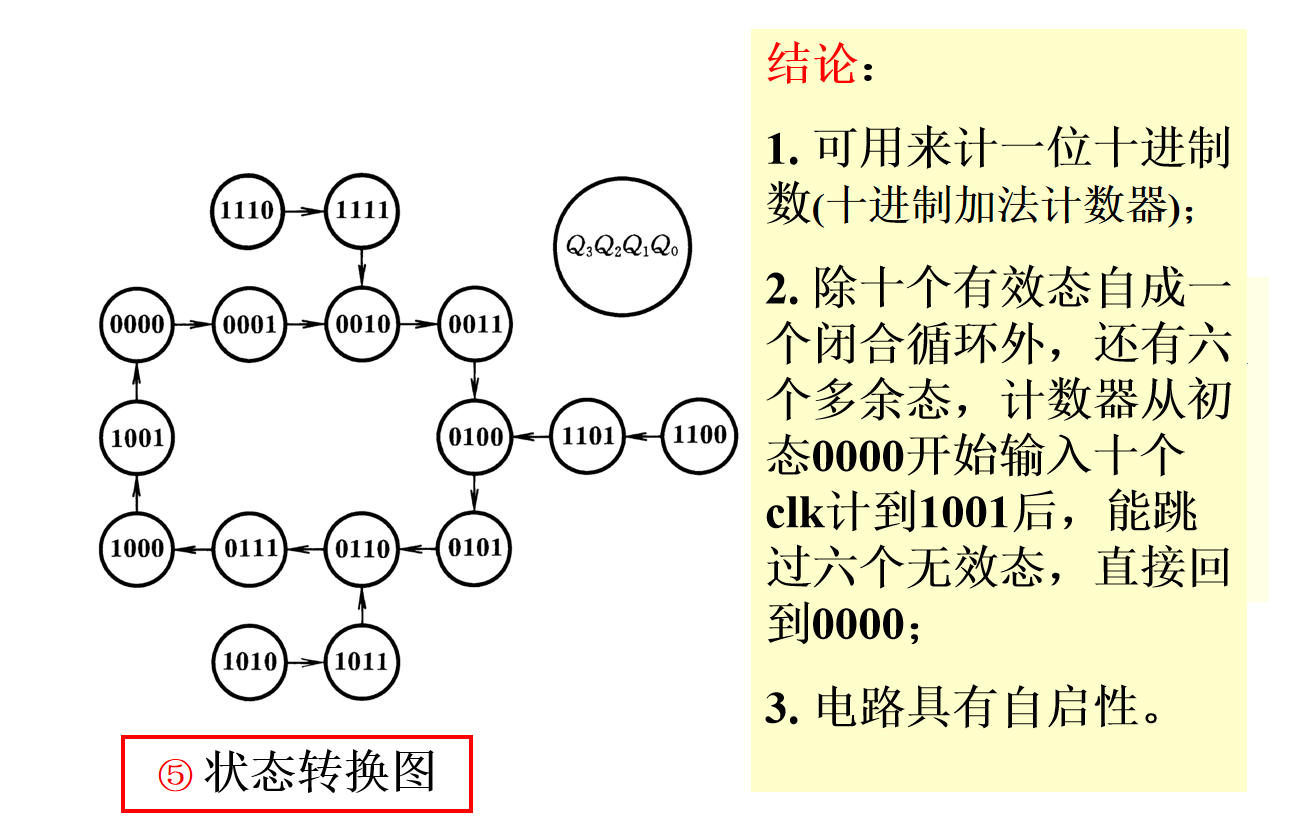

同步十进制加法计数器

我们想让他实现的任务是:在四位二进制计数器基础上修改,当计到1001时,则下一个CLK电路状态回到0000。

在实际应用中,增加了同步预置数、异步置零、保持功能。

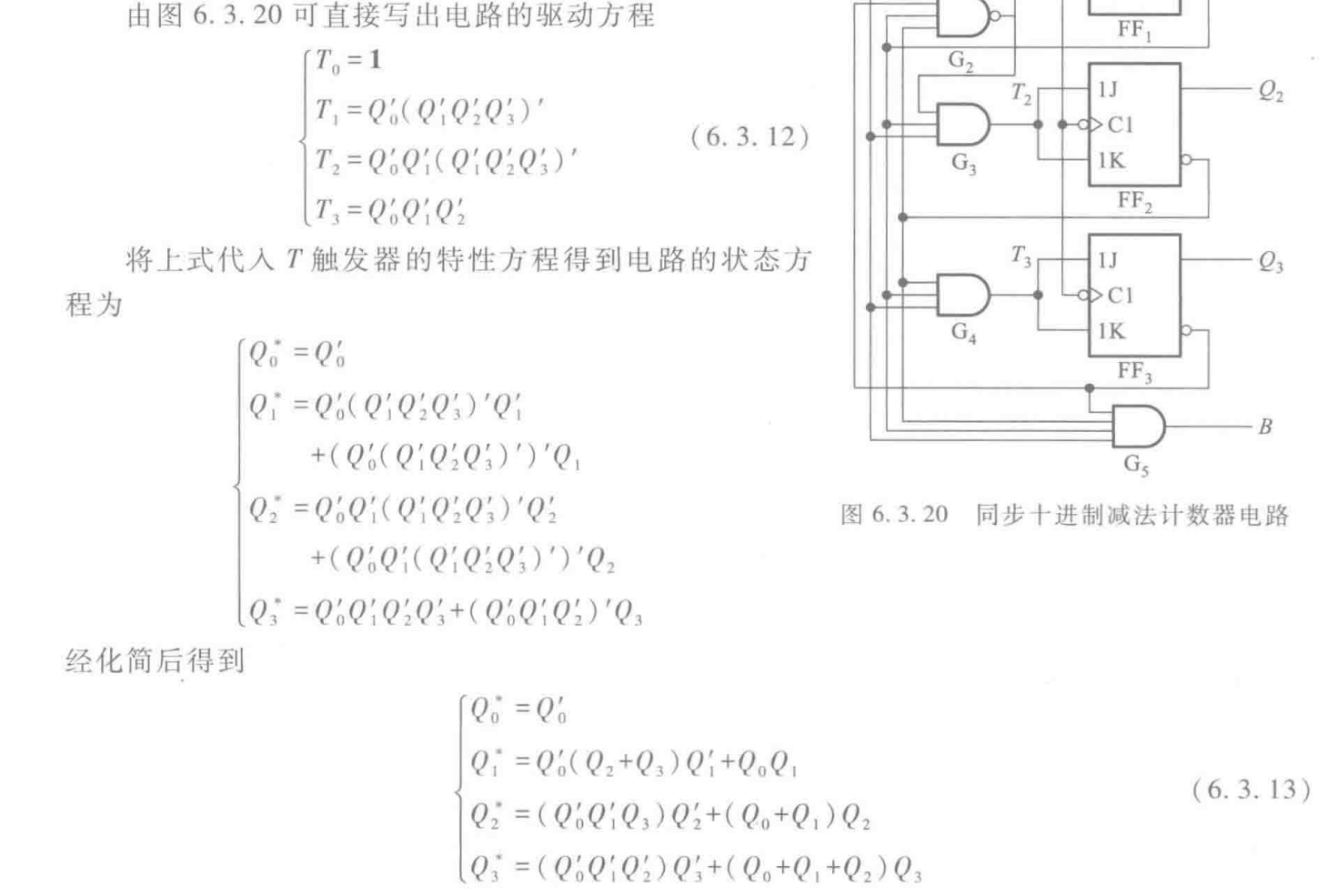

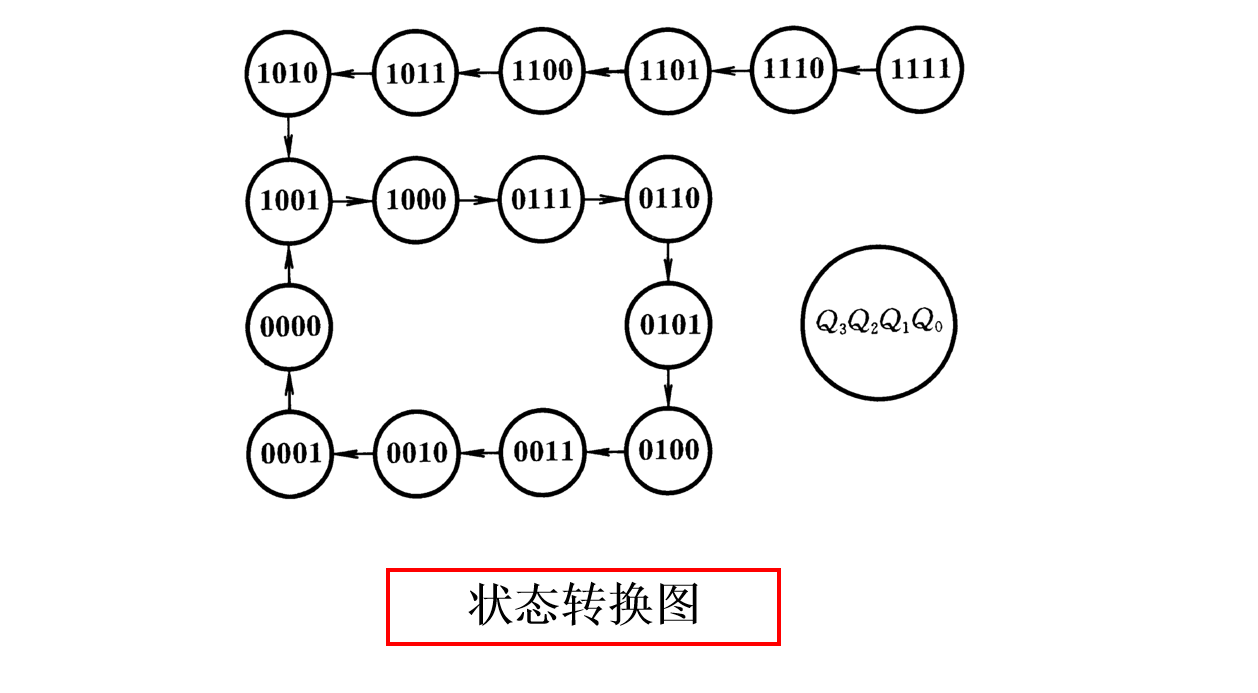

同步十进制减法计数器

对二进制减法计数器进行修改,在0000时减“1”后跳变为1001,然后按二进制减法计数就行了。

为了实现从Q3Q2Q1Q0= 0000状态减1 后跳变成1001 状态, 在电路处于全0 状态时用与非门G2 输出的低电平将与门G1 和G3 封锁, T1=T2=0。于是当计数脉冲到达后FFO 和FF3 翻成1 , 而FFI 和FF2 维持0 不变。

最后

以上就是执着早晨最近收集整理的关于同步计数器超详细分析的全部内容,更多相关同步计数器超详细分析内容请搜索靠谱客的其他文章。

发表评论 取消回复