脉冲触发

- 脉冲触发

- JK触发器

- JK状态在时钟周期内不变

- JK状态在时钟周期内发生改变

- 脉冲触发的动作特点

脉冲触发

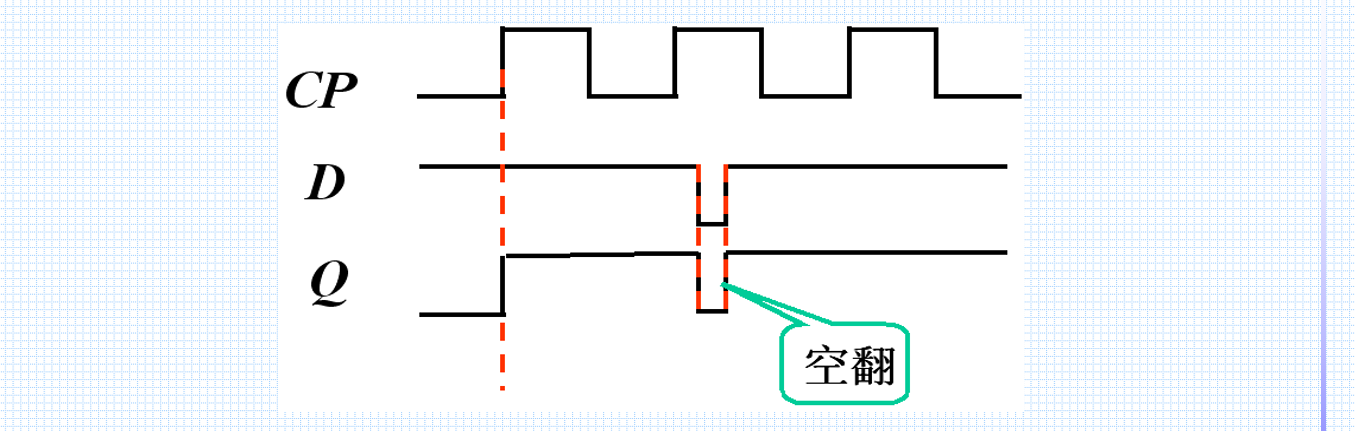

在之前的电平触发结构中,存在以下问题:

(1)结构简单,速度快。

(2)只要CP=1存在就可以翻转,所以容易造成空翻。

我们希望引入一种触发电路改善以上缺点。

下面讨论脉冲电路主要特点。

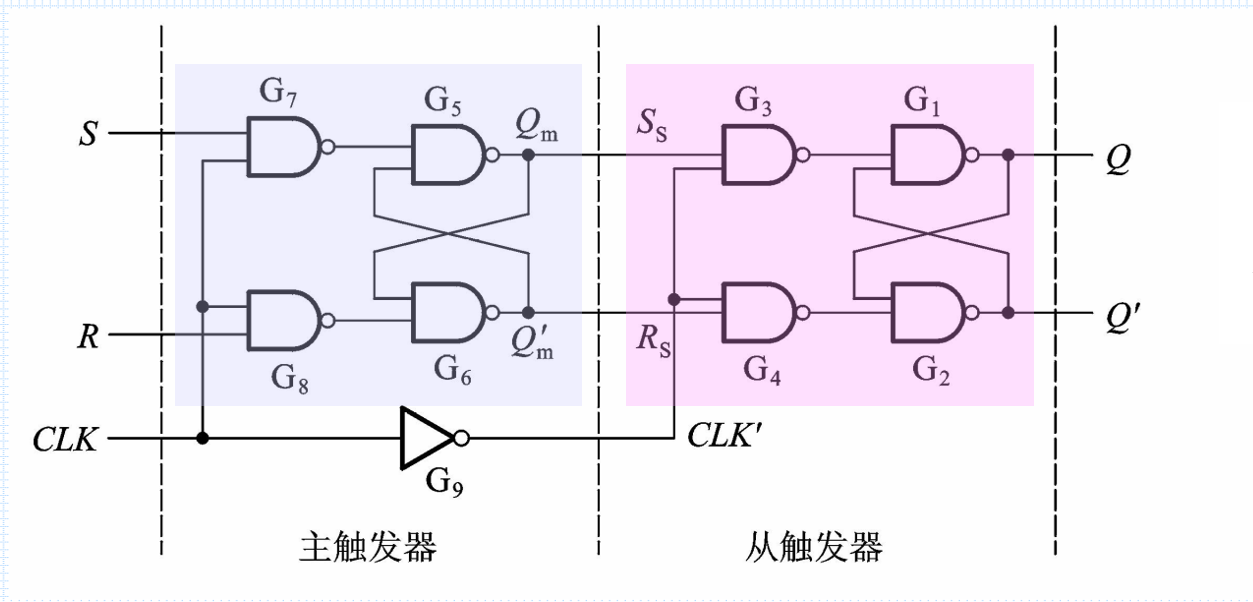

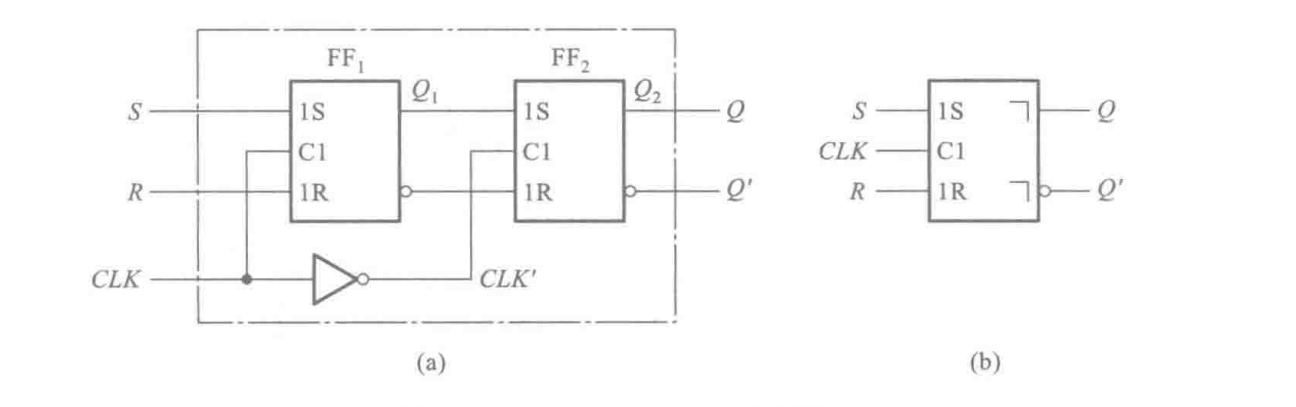

上述电路是脉冲触发SR 触发器的典型电路( 以前也把这个电路称作主从SR触发器) 。FF1 和FF2 分别为主触发器和从触发器。

当CLK = 0 时, FF1保持原状态不变。(这里参见SR触发器)

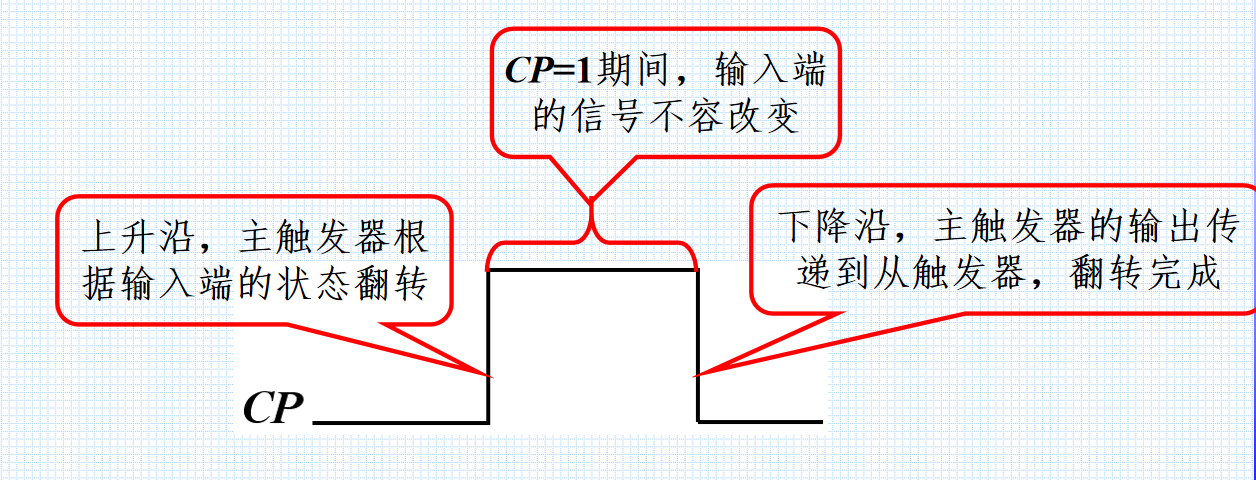

在CLK =1, 主触发器的输出Q1将按照S和R 输人端信号被置成相应的状态, 而从触发器保持原来的状态不变。

当CLK再次为0, 亦即下降沿到来时, 从触发器的输出Q2 被置成与此刻Q1相同的状态, 而主触发器开始保持状态不变。

由此可见, 在一个时钟周期里, 输出端的状态只可能改变一次, 而且发生在CLK 的下降沿。这一点和边沿触发器类似。

但与边沿触发不同的是,采用的为SR触发器而不是D触发器。且CLK=1时,主触发器输出的状态随SR变化而变化,则输出端状态与输入状态不可能始终保持一致。

因此,在脉冲SR触发器中,需要考察在CLK=1中主触发器的状态变化。

需要等到CLK的有效电平消失后,输出状态才能改变,因此也将这种触发方式称作延迟触发。

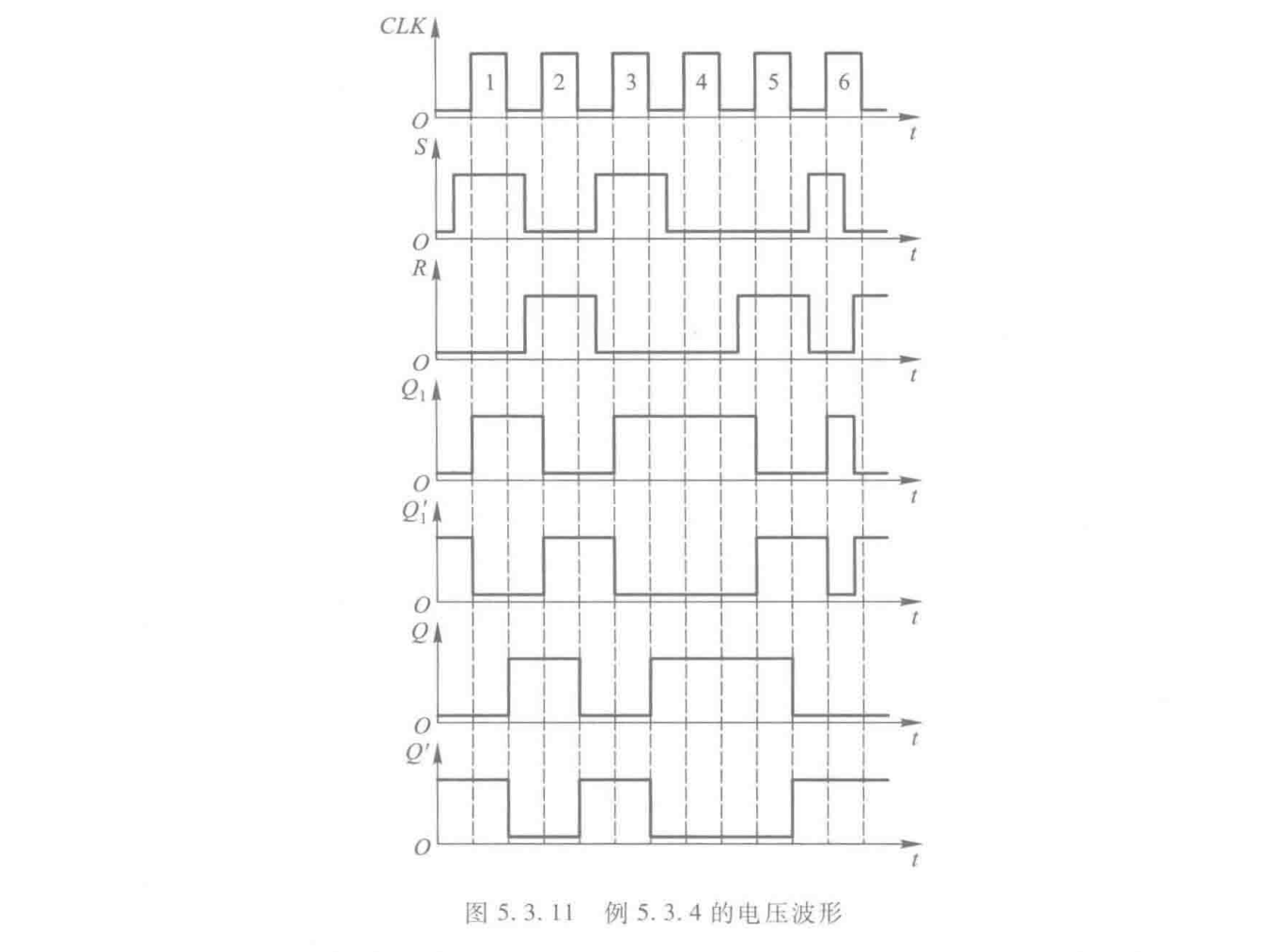

在图中更容易理解:

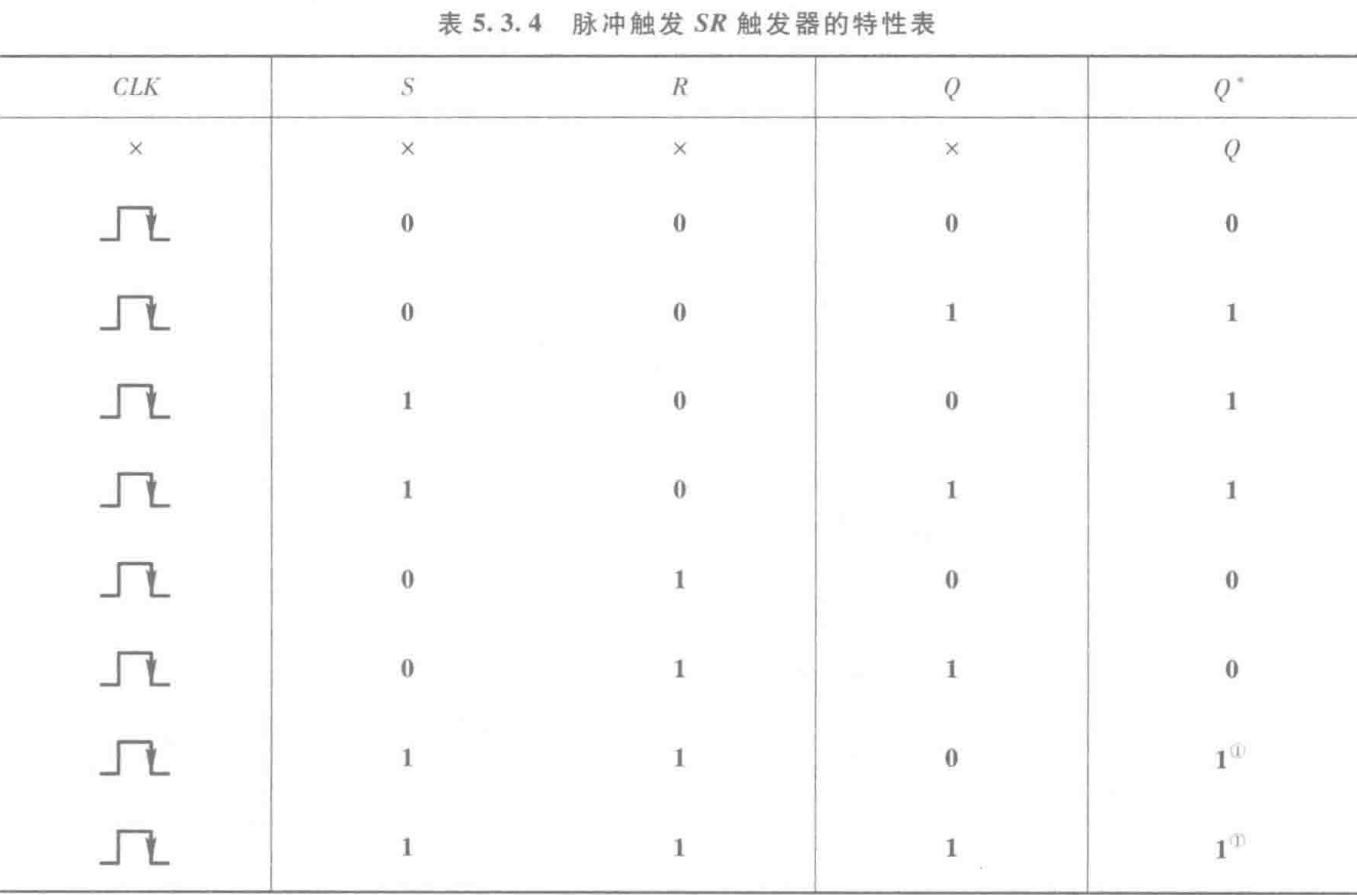

在CLK上升沿到来时,根据SR状态的变化决定Q1的取值;在CLK下降沿到来时,根据Q1的状态确定最终输出Q 的取值。但仍需要遵守SR=0的约束条件

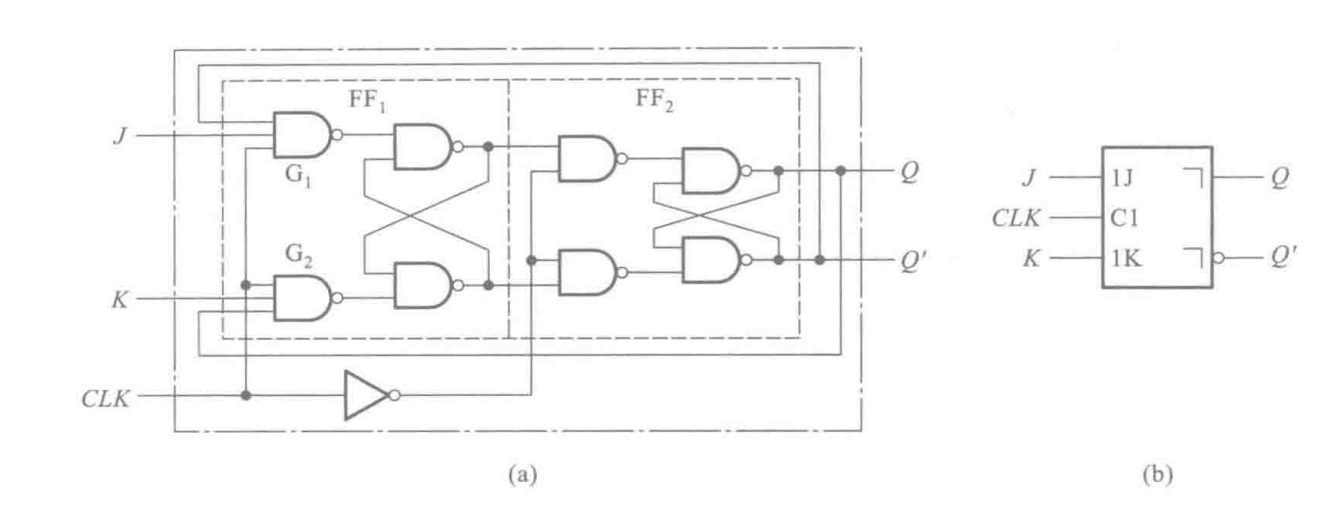

JK触发器

为了解决这个问题,我们将S=R=1的时候,Q和Q`接入输入端,则可以实现上述要求了。为了强调逻辑功能与SR触发器的区别,将输入端以J、K表示。

(1)若丿= K = 1 时, 需要分别考虑两种情况。第一种情况是Q = 0 。这时门G2 被Q 端的低电平封锁, CLK= 1 时仅G1 输出低电平信号, 故主触发器置1 、CLK= 0 以后从触发器也跟着置1 , 即Q*= 1

(2)第二种情况是Q= 1 。这时门G1被Q’ 端的低电平封锁, 因而在CLK = 1 时仅G2 能给出低电平信号, 故主触发器被置0 。当CLK = 0 以后从触发器跟着置0 , 故Q* = 0 。

综合以上两种情况可知, 当丿= K = 1 时, CLK 下降沿到达后触发器将翻转为与初态相反的状态。

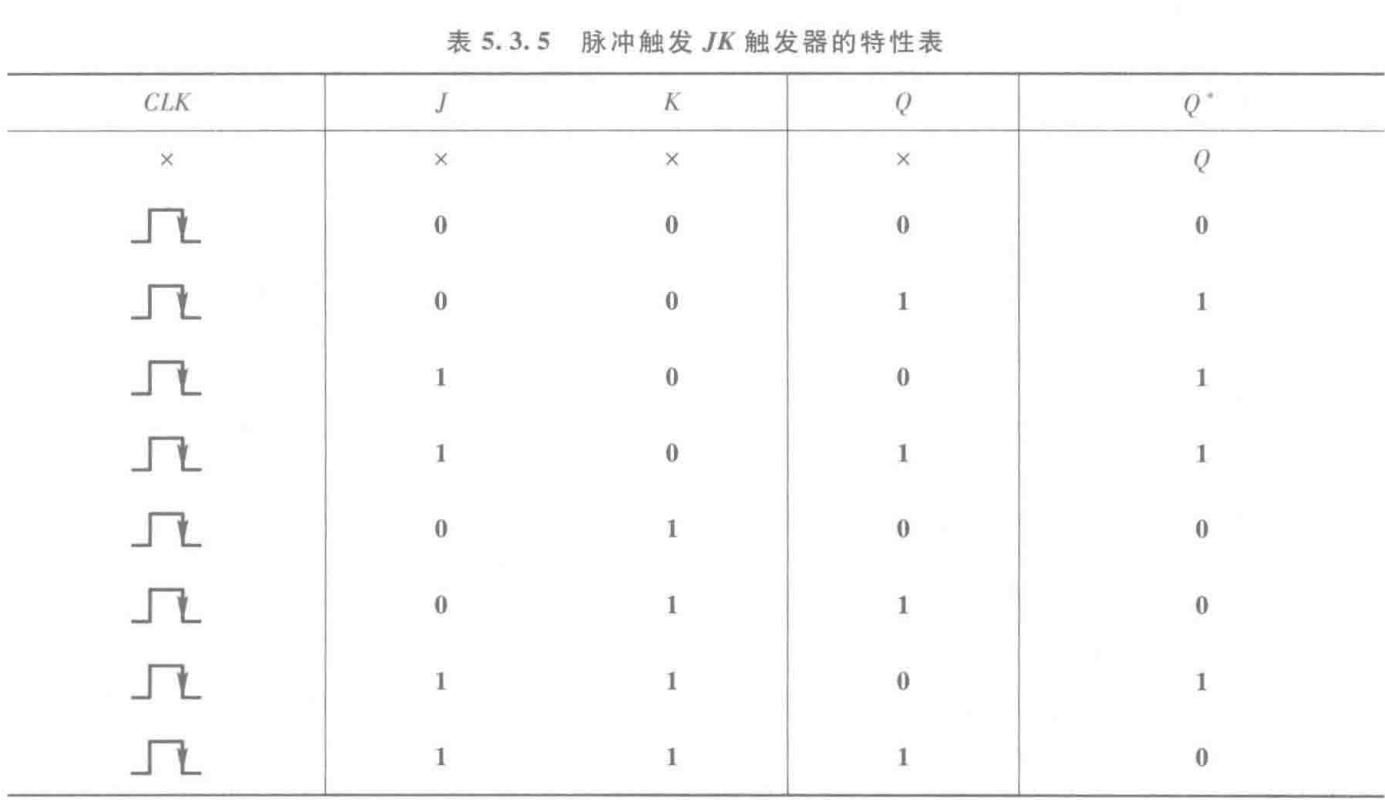

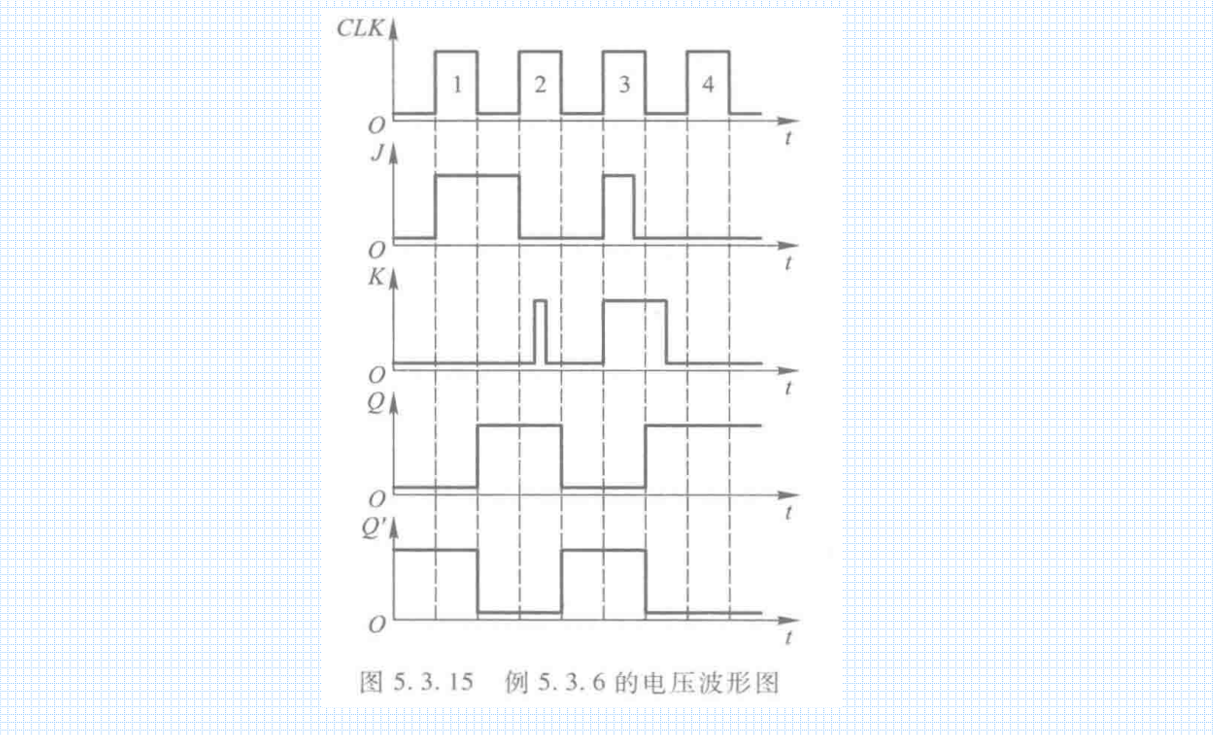

JK状态在时钟周期内不变

CLK=1时,J、K状态不变;下降沿到达时根据JK状态去查表画图。

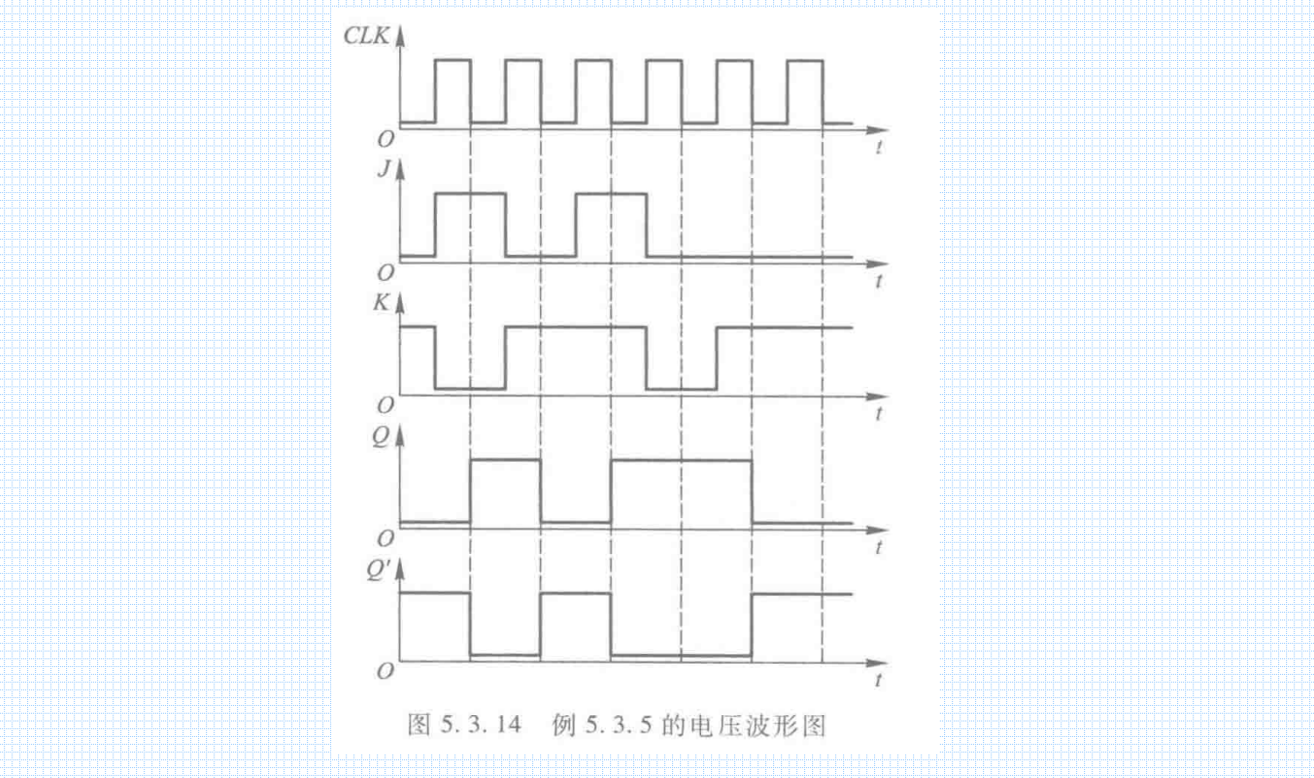

JK状态在时钟周期内发生改变

(1)第一个CLK高电平期间,JK无改变,则下降沿到时触发器置1

(2)第二个CLK高电平期间,K端发生变化,需要考虑在CLK高电平期间的变化,此时J=0,K=1,主触发器被置0;(且前面提过一个时钟周期内,状态只改变一次)则虽然第二个CLK下降沿到来时J=K=0,但从触发器仍按主触发器的状态被置0

(3)第三个CLK高电平期间,曾出现过J=K=1状态,则主触发器置1 ,当下降沿到来时,从触发器也被置1。

脉冲触发的动作特点

(1 ) 触发器的翻转分两步动作。第一步, 当CLK 以高电平为有效信号时, 在CLK = 1 期间主触发器接收输人端( SR或J 、K ) 的信号, 被置成相应的状态, 而从触发器不动; 第二步, CLK 下降沿到来时从触发器按照主触发器的状态翻转( 若CLK 以低电平为有效信号, 则Q 和Q’ 状态的变化发生在CLK 的上升沿。)

( 2 ) 因为主触发器本身是一个电平触发SR 触发器, 所以在CLK = 1 的全部时间里输人信号都将对主触发器起控制作用。

最后

以上就是冷艳滑板最近收集整理的关于脉冲触发、JK触发介绍——数电5.3节的全部内容,更多相关脉冲触发、JK触发介绍——数电5内容请搜索靠谱客的其他文章。

发表评论 取消回复