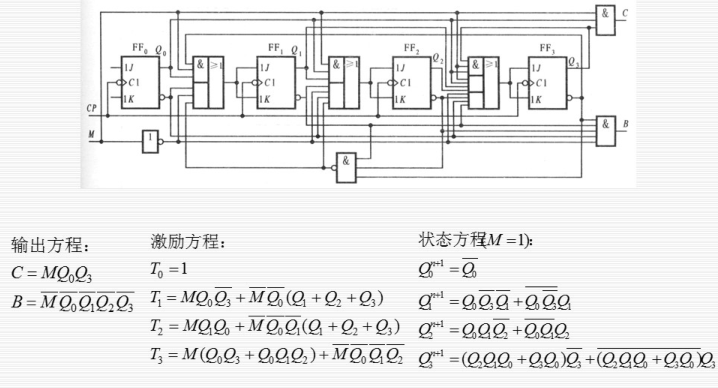

- 十进制计数器M=10,采取BCD编码方式从0000->1001,共有6个无效状态,检查自启动问题。可逆说明加法和减法两种模式都可以,需要增加一个控制端M=1时为加法计数

- 很复杂的原理图,看了就怀念Verilog

- 直接根据激励方程连接电路图,在第一次仿真时出现错误,检查几遍连线均没发现问题(应该还是有问题的)把一些端口直接命名的线连上后重新仿真后终于出来结果

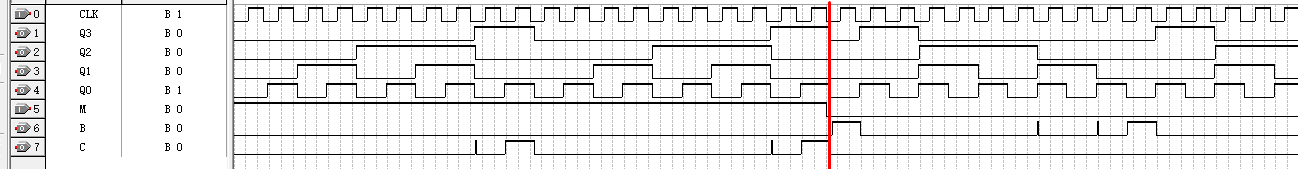

- 根据波形图可以看出,当M=1时计数从0000到1001并在1001时输出一个正脉冲,当M=0时计数从1001到0000并在0000时输出一个脉冲

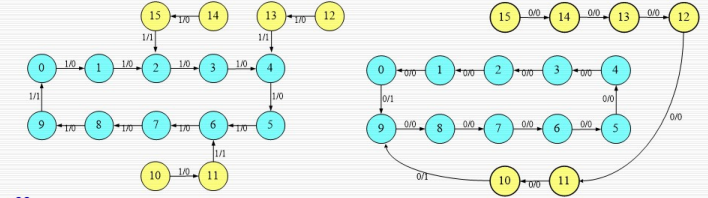

- 最后检查自启动问题

最后

以上就是活力万宝路最近收集整理的关于quartus仿真27:JK触发器构成的同步十进制可逆计数器(分析)的全部内容,更多相关quartus仿真27:JK触发器构成内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复