1、 前言

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的使用寿命,因此得到了广泛的应用。

2.设计任务和要求

用中小规模集成电路设计一台能显示日、时、分秒的数字电子钟,要求如下:

1.由晶振电路产生1Hz 标准秒信号。

2.秒、分为00—59六十进制计数器。

3.时为00—23二十四进制计数器。

4.周显示从1—日为七进制计数器。

5.可手动校正:能分别进行秒、分、时、日的校正。只要将开关置于手动位置,可分别对秒,分、时、日进行手动脉冲输入调整或连续脉冲输入的校正。

6.整点报时。整点报时电路要求在每个整点前鸣叫五次低音(500Hz),整点时 再鸣叫一次高音(1000Hz)。

3、实验器件选择

本次实验中需使用到的元器件如下表所示

器件名称 | 型号 | 数量 | 功能 |

芯片 | 74HC00 | 2 | 与非 |

芯片 | 74HC04 | 1 | 非门 |

芯片 | 74HC74 | 1 | 2分频 |

芯片 | 74HC161 | 7 | 16进制 |

芯片 | 4060 | 1 | 二进制计数器 |

芯片 | 4511 | 1 | 驱动LED |

晶体振荡器 | 32768 | 1 | 产生频率脉冲 |

电阻 | 22M | 1 | --- |

电阻 | 32M | 1 | --- |

共阴单8显示器 | 0.56英寸 | 7 | 显示数字 |

可调电容 | 30p | 2 | --- |

表1元器件列表

4、方案设计

(1)脉冲信号电路设计方案

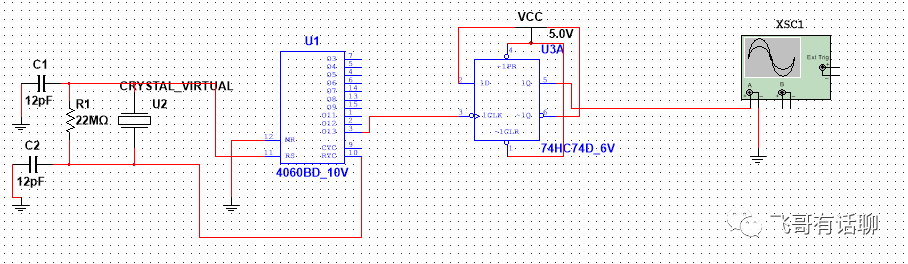

石英晶体主要成分是二氧化硅,它的物理化学性质十分稳定,本电路的显著优点是频率稳定性极好,理论上可达1.000000 Hz的精确度,石英晶体产生的信号经过4060可以达到14分频,再经过一个D触发器74HC74就实现了15分频输出1HZ信号。

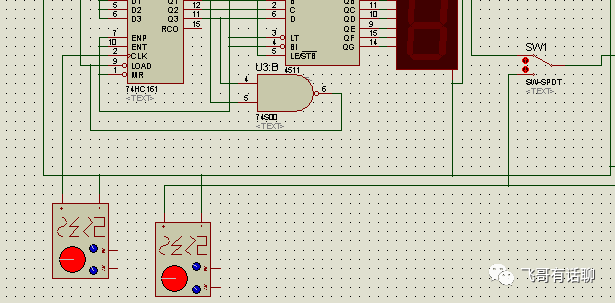

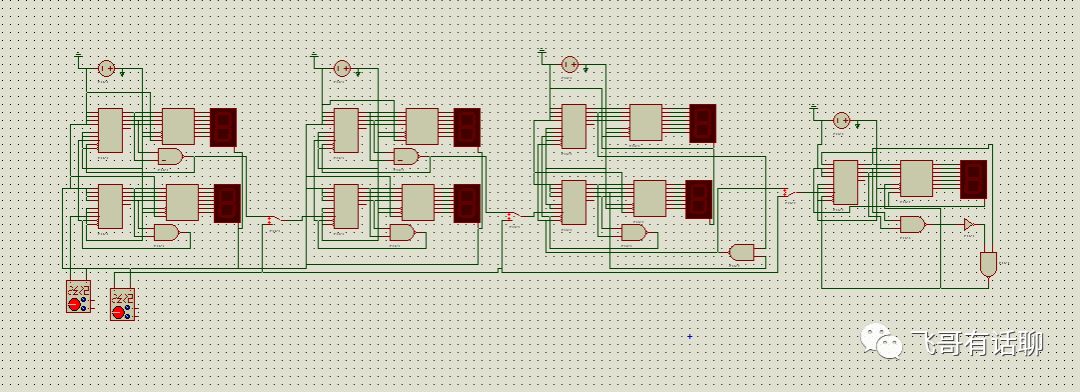

(2)秒、分电路设计

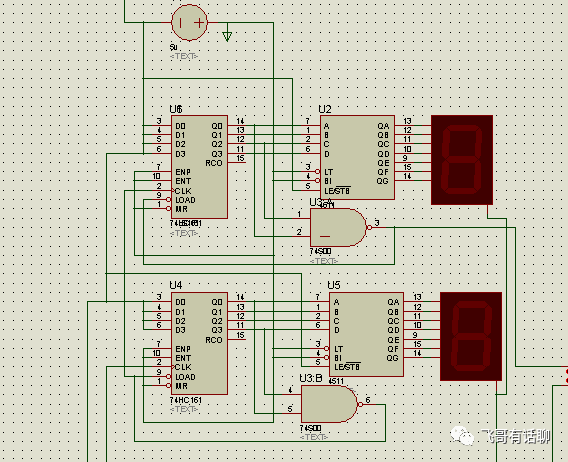

这个模块就是“秒”的部分,由74HC161芯片产生16进制计数,然后利用送数功能,当计时到1001(即十进制数字9)送0,实现0~9的循环,作为秒的个位。同时将1001经过与非门之后送到下一片74HC161芯片作为时钟信号,也就是个位计数十次十位进一次位。十位计数到0101(即十进制5)后经过与非门送到Load置数,同时作为下一片芯片的时钟信号。十位实现0~5的循环。这样,秒的个位和十位就完成了。

分的设计和秒类似,这里就不再赘述。

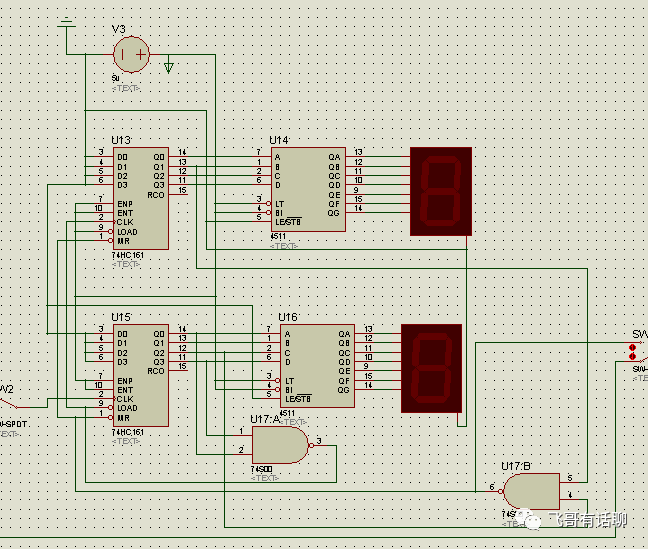

(3)时电路设计

时的电路设计与前面的分和秒类似,但是有些不同,主要是进位上面需要注意一下,个位上先是0~9循环两次,然后是0~4,接着向十位进位。十位上只能是0~2的循环。设计思路如下:个位上,当计数到1001时经过与非门产生送数,计时器回到0,并且向十位产生进位信号。十位上,当个位产生0100和十位产生0010时(组合后就是十进制24),产生的信号送到复位端,让个位和十位复位,并且信号输入到下一级的CLK上面。这样就可以达到要求了。

(4)周电路设计

周要实现周一~周日(日用8代替),因此,当计数到0111时经过与非门置数1,同时因为要显示8(跳过7),所以利用译码器的LT可以实现全亮,这样就达到了设计要求。

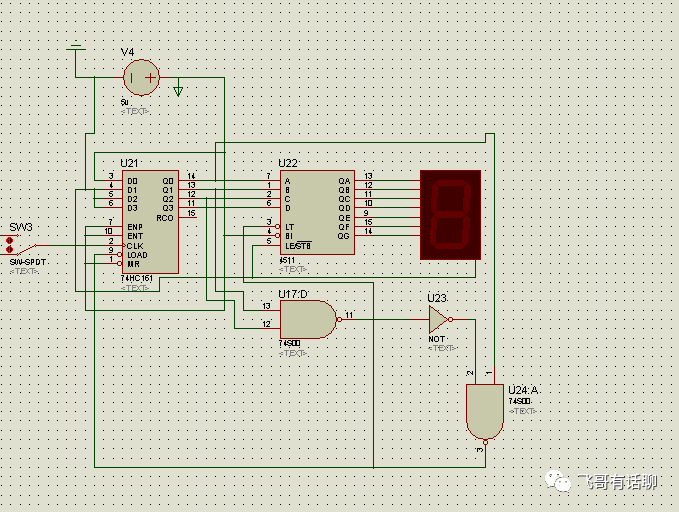

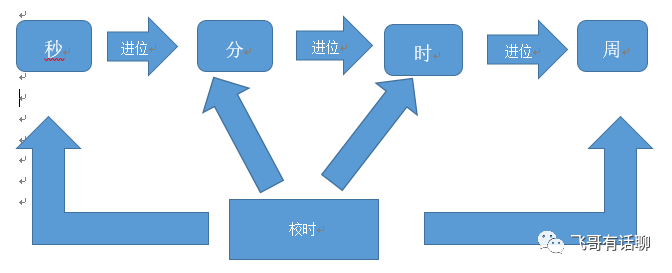

(5)校时电路设计

在刚刚开机接通电源时,由于日、秒、分、时为任意值,所以,需进行调整。置开关在手动位置,分别对时、分、秒、日进行单独计数,计数脉冲由单次脉冲或连续脉冲输入。

方案实现:在芯片的CLK引出一个接口,既可以接收前一级的进位信号,也可以单独输入一个高频率脉冲信号,方便调整时间。

总体连接示意图

整体电路图

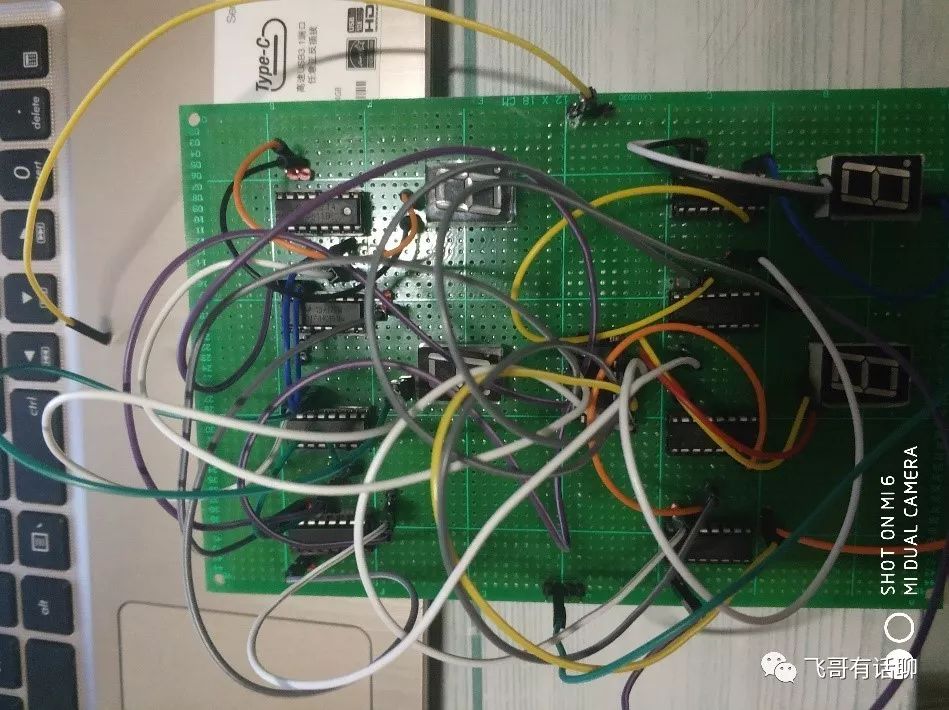

实物图1

实物图2

仿真动态图

以上就是关于数字时钟的设计。

更多精彩内容欢迎关注↓

最后

以上就是曾经老师最近收集整理的关于74ls90设计十进制计数器电路图_数字电子钟逻辑电路设计1、 前言2.设计任务和要求3、实验器件选择的全部内容,更多相关74ls90设计十进制计数器电路图_数字电子钟逻辑电路设计1、 前言2内容请搜索靠谱客的其他文章。

发表评论 取消回复