@TOC 导师的项目是低功耗,尽量减少功耗。看到GPS_-TSMC28N_PLL_DIV用的是异步计数器。产生疑问,为什么用异步计数器而不用同步计数器。 利用相同的D触发器,分别设计同步计数器和异步计数器,在Cadence平台仿真验证。 下面分别设计3位的递减计数器,带置数端和置数使能

1.异步递减计数器

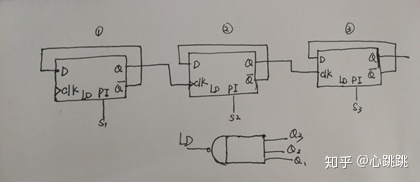

1.1异步计数器原理图

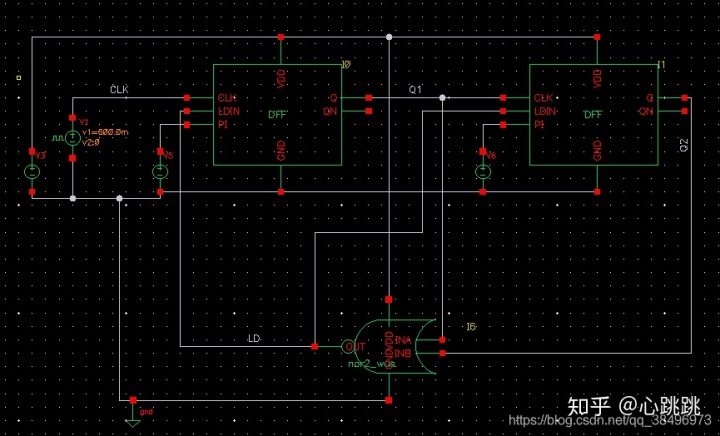

异步递减计数器,用带置数功能的D触发器实现,每一个D触发器的Q-和D连接,构成二分频器。PI是置数端,LD是置数使能(高点平有效)。开始从S3 S2 S1开始递减计数,当Q3 Q2 Q1=000时,经过或非门输出高电平,使能置数,使的Q3 Q2 Q1= S3 S2 S1。

注意:此处的置数端为异步置数,当LD=1时,立即置数,图中化成了与非门,应为或非门,置数高电平有效

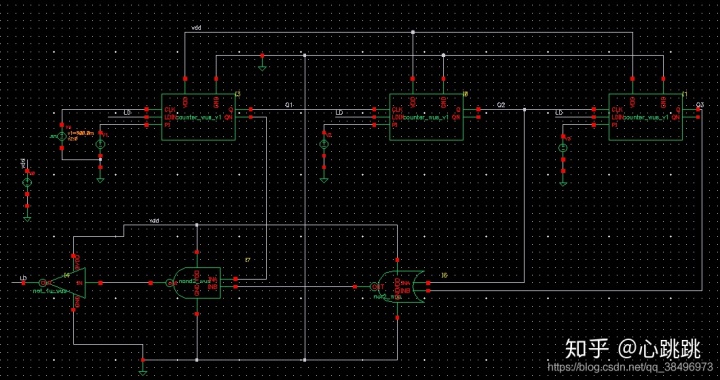

cadence仿真电路如图所示。

1.2异步计数器仿真结果

这里不放仿真结果图片,仿真功能正常。

2.同步计数器

2.1同步计数器原理

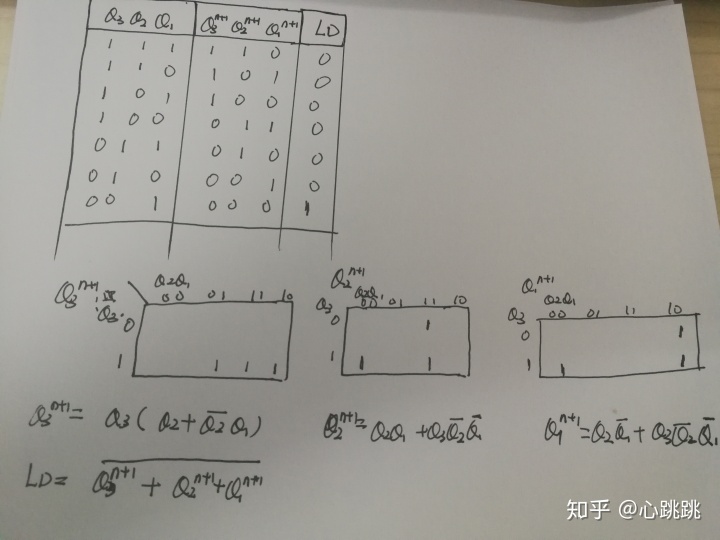

- 用时序逻辑设计的方法,画出真值表:

- 根据真值表画卡诺图

- 根据卡诺图化简逻辑表达式

根据逻辑表达式,搭建电路图,采用与异步计数器同样的D触发器。

3.性能参数对比

功耗对比表

时钟频率 | 异步 | 同步 - | :-: | -: 100M | 1.76uA| 3.37uA 2G | 33.4uA | 66.4uA 3G | 无法工作|无法工作

传播延时对比表 传播延时仿真的时候,cadence中vpulse信号源的上升下降时间不设置,保持软件自动设置。

时钟频率 | 时钟边沿| 异步tplh | 同步tplh|异步tphl|同步tphl - | - | :-: | -: | -|- 100M | 100p|220p|260p|170p|180p 2G | 5p | 170p|201p|116p|113p

同步和异步计数器最高工作频率近似均在2-3G,传播延时差距不大,但同步计数器功耗较大,由于其包含有大量的组合逻辑电路。

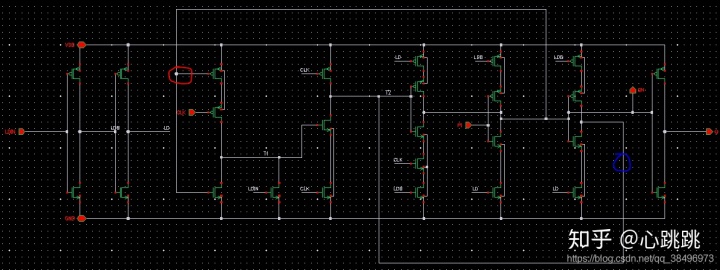

4.D触发器原理分析

如图为计数器中用到的D触发器,带异步置数功能。红色的为数据端,如1.1节所示的异步计数原理图,将Q-和数据端DATA接在一起,构成递减计数器(也可以看作二分频器)。PI是置数端,LD是置数使能(高点平有效),LD=1时,Q=PI. 下面分析D触发器的功能:假设Q-与D端未连接,分析正常触发器的功能。 假设正常计数:LD=0,LDB=1;LDIN=0 clk=0时:T1=D-,T2=1 clk=1时:T1=D-(保持clk=0时的数据),T2=D,Q-=D-,Q=D。 置数功能: 假设LD=1,LDB=0;LDIN=1 则PI经过两级反相器传递给Q。完成置数功能。

问题:蓝色线的作用是什么?是否可以去掉 将蓝色反馈回路去掉后搭建如下电路仿真触发器的功能。

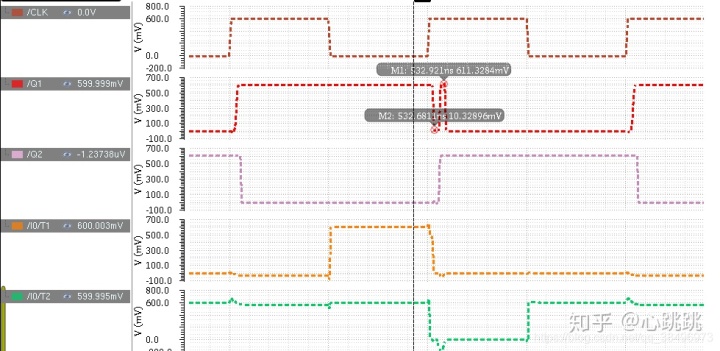

如图所示为一个2位的递减计数器,已经除去了蓝色反馈线。仿真结果如下

图a 无蓝色反馈线的异步递减计数器仿真结果

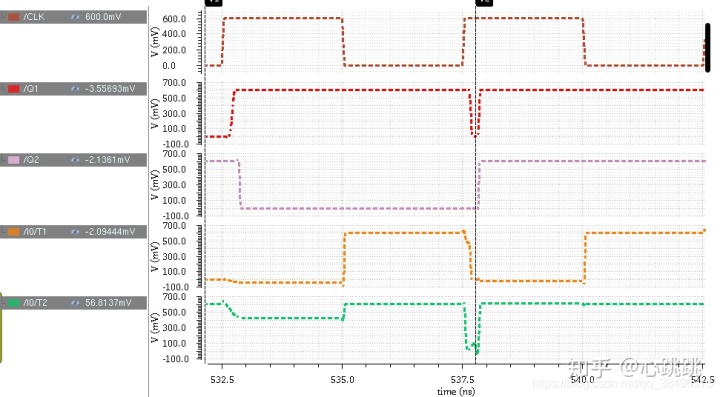

图b 带蓝色反馈线的异步递减计数器仿真结果

图a和图b对比结果,在Q2Q1=00之后,计数器重新置数为11,无蓝色反馈线的触发器的Q1会立即再拉低,导致Q2Q1=11状态无法保持一个时钟周期。

假设,在某个上升沿之后,Q2Q1=00,此时LD=1,立即置数Q1=1,则Q-=0。 此时T2=0;上升沿之后,clk仍然为高电平clk=1;此时会将T2=0传递到Q端,使得Q立即拉低。 如果带有蓝色反馈线: 在某个上升沿之后,Q2Q1=00,此时LD=1,立即置数Q1=1,则Q-=0。与此同时,由于蓝色反馈线的存在会使得T2=1,之后clk为高电平clk=1;此时会将T2=1传递到Q端,Q端数据不变。

同理如果,假设在某个上升沿之后,Q2Q1=00,此时LD=1,立即置数Q1=0,则Q-=1。 当T2=1时,上升沿之后,clk仍然为高电平clk=1;此时会将T2=1传递到Q端,使得Q立即拉高,出现错误。

总结:蓝色反馈线的存在会在置数的同时将T2与Q端数据保持一致,防止在上升沿置数之后clk=1的时候,将T2传递给Q,造成错误。

2020.08.31更新 跟导师聊过之后,导师提出质疑,理论上同步计数器时钟信号驱动更多mos管的栅极,而本次仿真验证的过程用的是cadence理想时钟,驱动能力相当于无穷大。真实的仿真过程是双模预分频输出驱动连个计数器,而双模预分频驱动能力有限,驱动太多mos管限制工作频率提高。

最后

以上就是野性招牌最近收集整理的关于74ls90设计十进制计数器电路图_同步计数器与异步计数器对比的全部内容,更多相关74ls90设计十进制计数器电路图_同步计数器与异步计数器对比内容请搜索靠谱客的其他文章。

发表评论 取消回复