对于学习FPGA的初学者而言,使用Altera公司芯片的开发板价格较为便宜,参考的资料也多,而与之配套的就是Quartus II开发软件。小白自己使用的就是Quartus II 13.1版本,下面用一个计数器的verilog代码为例,简述一下Quartus II的入门级使用和调用Modelsim仿真的方法。

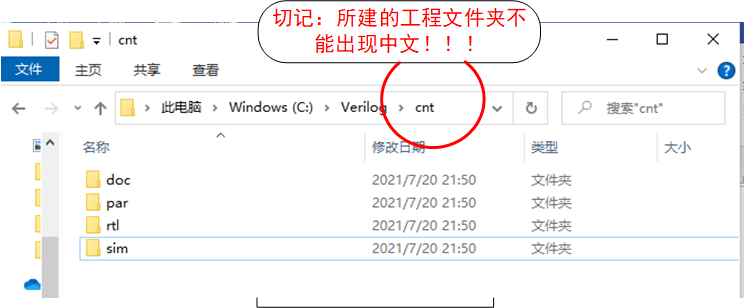

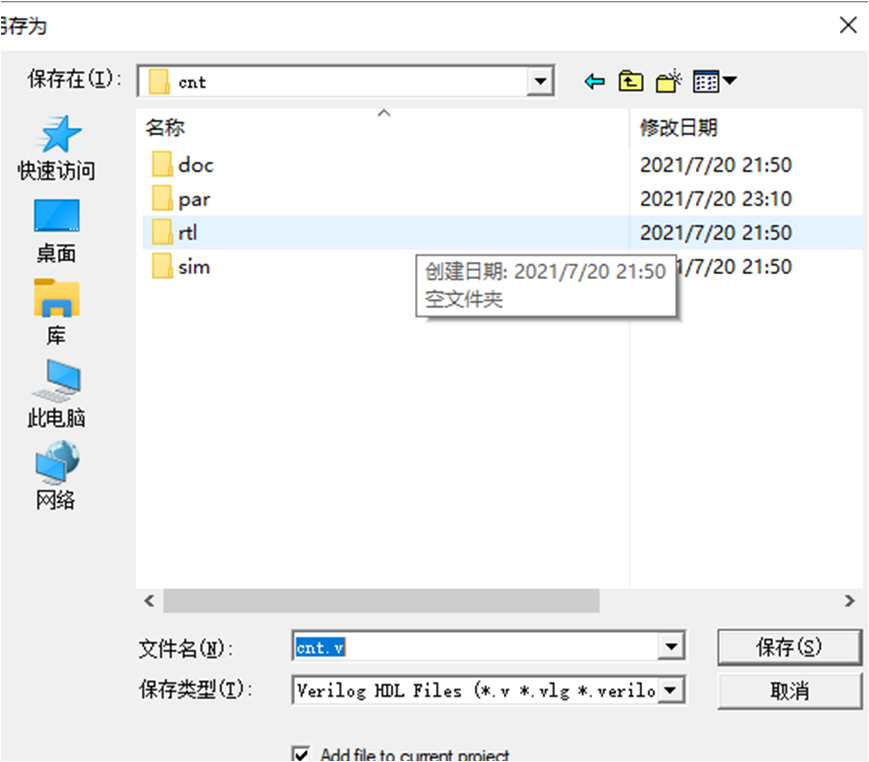

1:首先养成一个良好的习惯,在做工程前建立一个良好的工程文档(目的是让你自己可以找到该工程!!!)。本次工程文档命名cnt,小白呢,喜欢将工程文档内部分为以下四个文档:doc(放文件资料),par(放Quartus II所创建的工程),rtl(放代码),sim(仿真的东西)。

如果不会的话,可以参照小白的文件进行创建。

2:在Quartus II中创建工程。步骤如下:

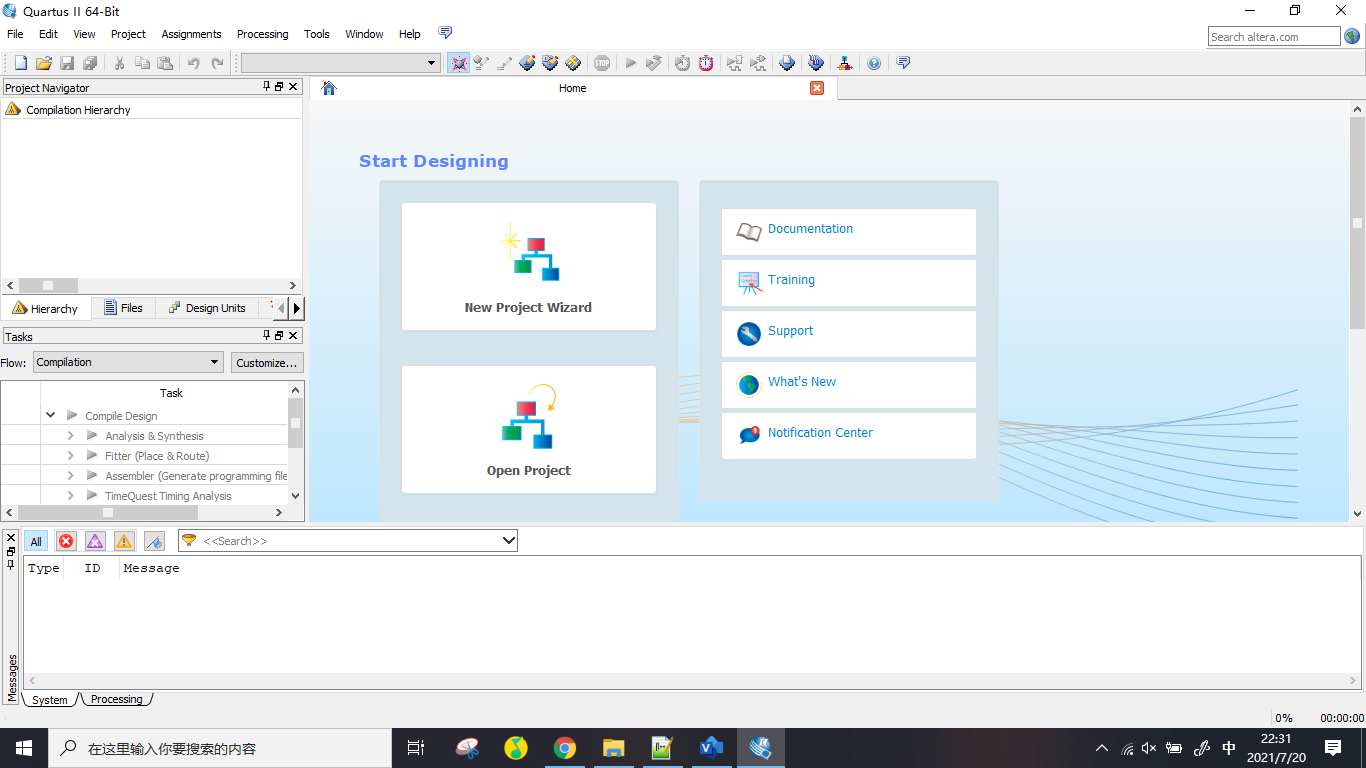

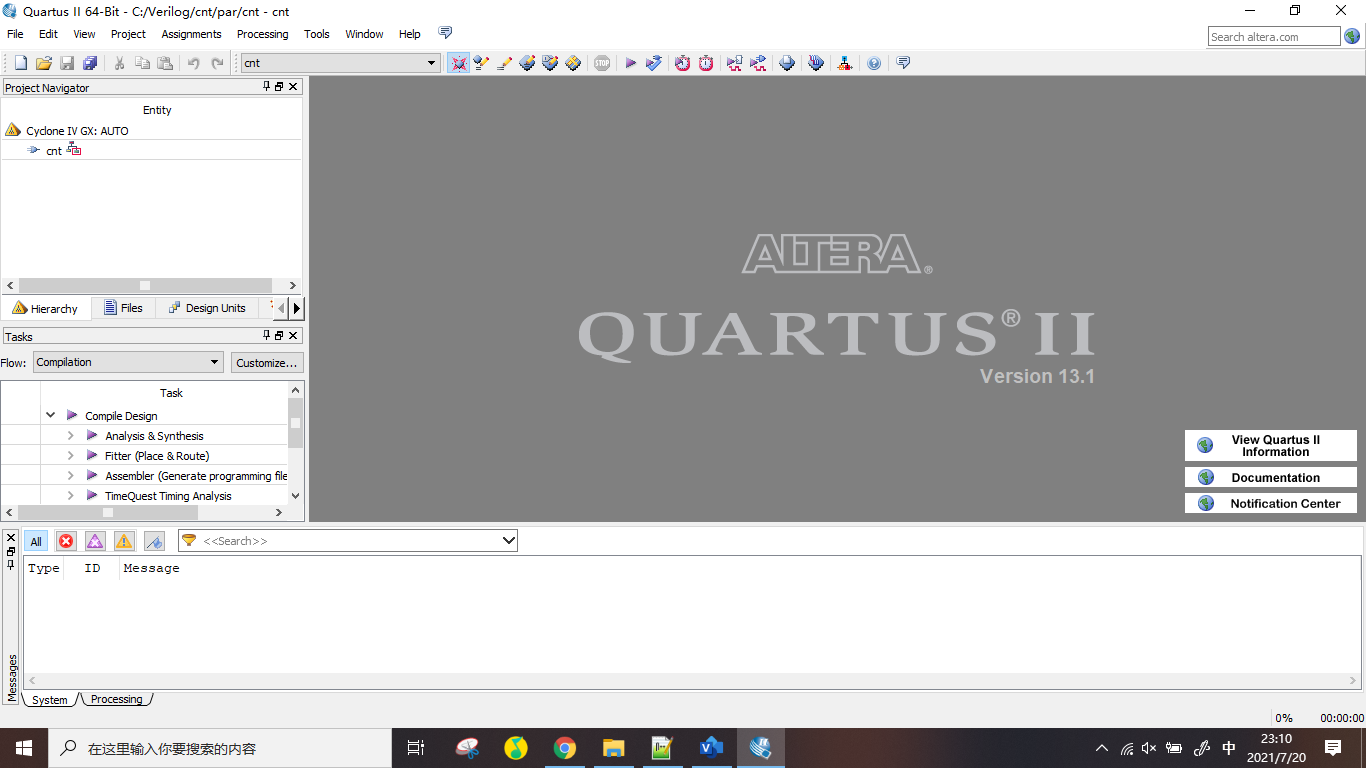

2-1:打开Quartus II,界面如下:

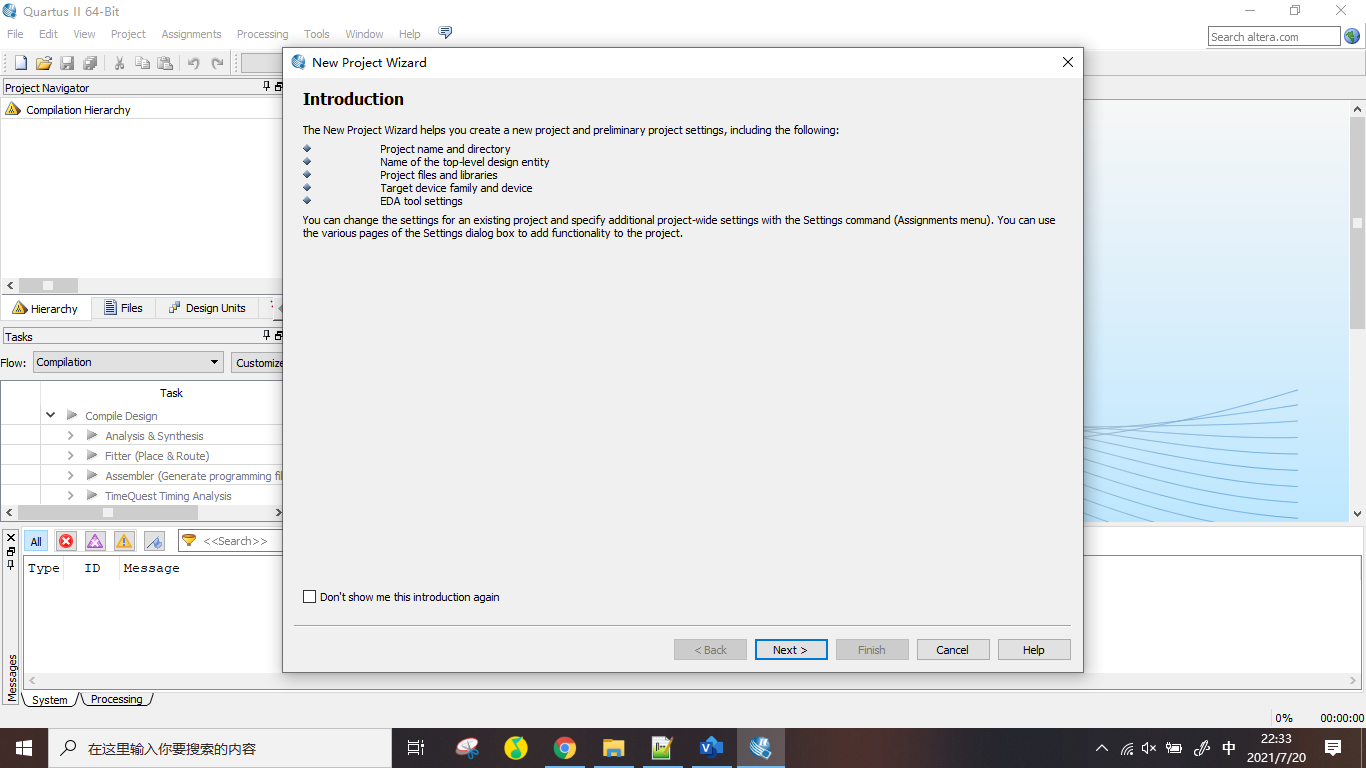

2-2:直接点击2-1图中的New Project,点完后出现以下界面:

这个界面不用管,直接点击 Next !!!

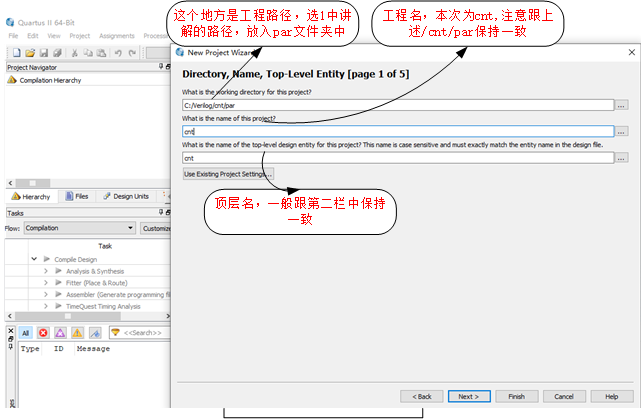

2-3:点击Next后,出现以下界面:

第一栏为工程放哪?选择1中路径,注意路径中不能出现中文!!!

第二栏为工程名?与1中创建的工程名保持一致,本次工程名为cnt。

第三栏为顶层名?对于小白来说,一般与第二栏保持一致。

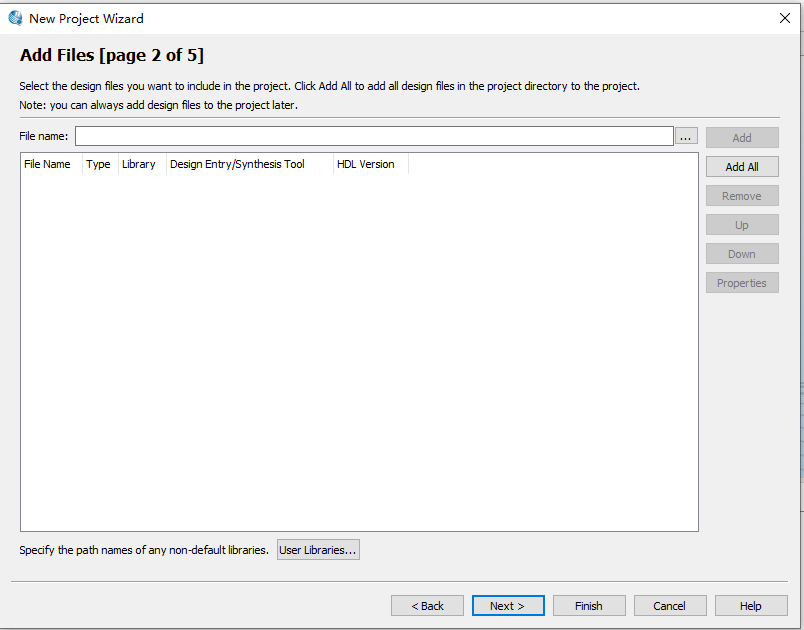

2-4:输入完后,点击Next,出现以下界面:这个是添加设计代码的地方,不用管它,直接点击Next。

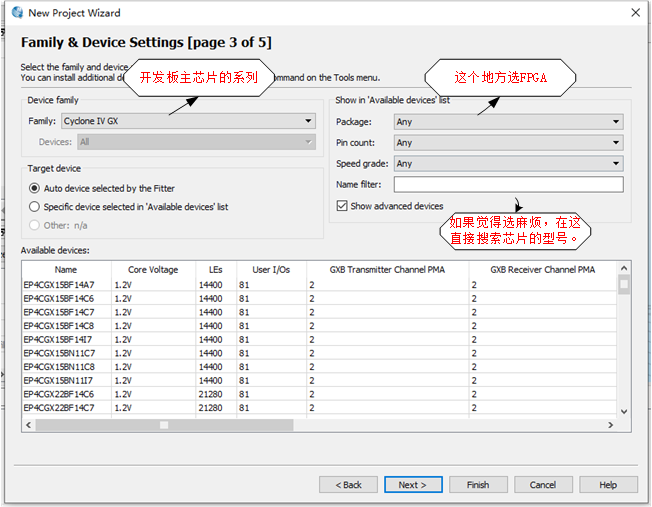

2-5:点击Next 后,出现以下界面:

这个界面针对的是有开发板的同学,注意一定要是Altera公司生产的芯片,可以去参考开发板手册,了解芯片的型号!!!小白推荐了解了型号之后,直接搜索型号!!!

如果没有开发板的同学,直接点击Next。

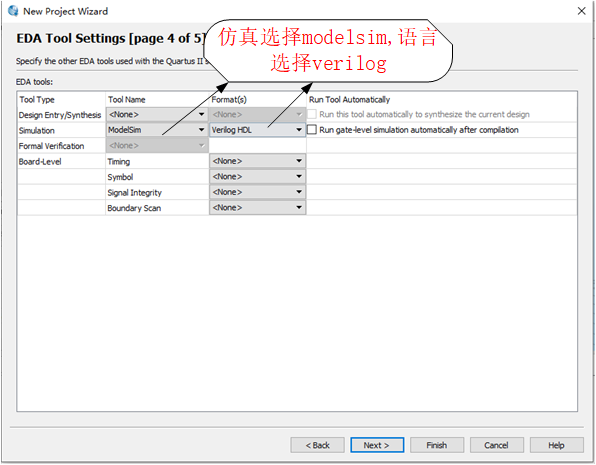

2-6:点击Next 后,出现以下界面:

因为要调用modelsim仿真,所以这里就选择modelsim,语言的话,小白使用的是verilog语言,所以这里选择verilog。然后点击Next。

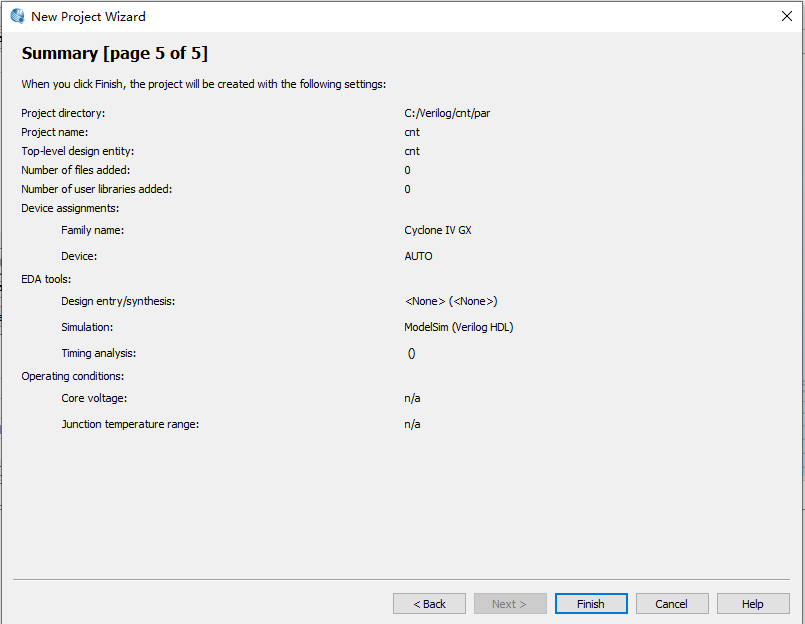

2-7:点击Next后,会出现以下界面:

这个界面就是一个你的所选清单,不用管他,直接点击Finish。

2-8:这时会出现以下界面:

不要慌,看下一步!!!

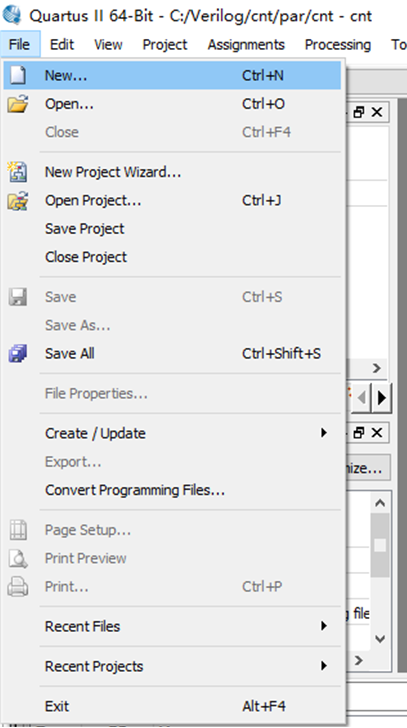

2-9:点击File-New后,选择verilog HDL。至此所有前期工作已经完成,下面来编写本次cnt的verilog代码。

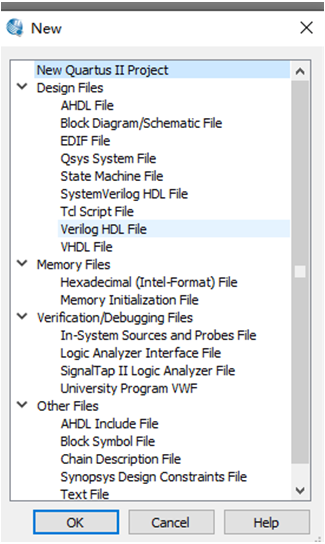

3:现在来编写verilog代码。(刚入门的同学可以去找找一些工程敲一敲代码来练一练),大家也可以使用本次计数器的工程,本次是一个四位的计数器,所以最大计数值是15,所以计数器记到15,计数器清零,否则计数器加1.。代码如下:

module cnt(

clk ,

rst ,

cnt

);

input clk ;

input rst ;

output reg [3:0] cnt ;

always@(posedge clk or negedge rst)

begin

if (!rst)

cnt <= 0;

else if (cnt == 4'd15)

cnt <= 0;

else

cnt <= cnt + 1'b1;

end

endmodule为了防止同学们看不清代码,将代码附在此,小白还是希望同学门去敲一敲代码。

3-1:点击保存后,将代码保存在rtl中。

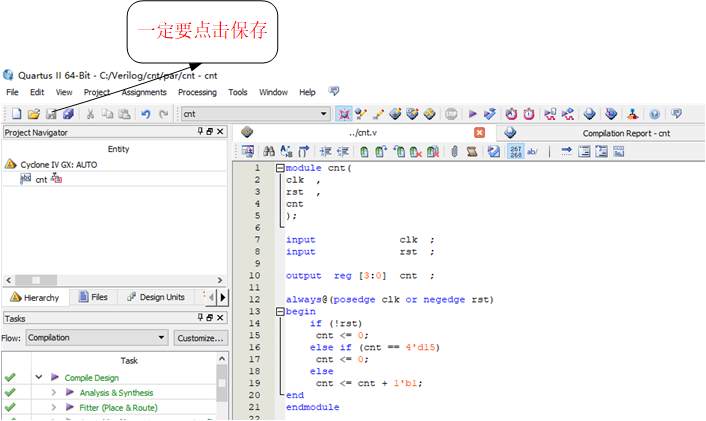

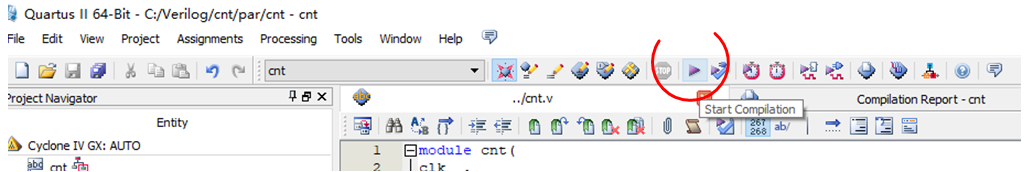

3-2:保存完后,开始编译:

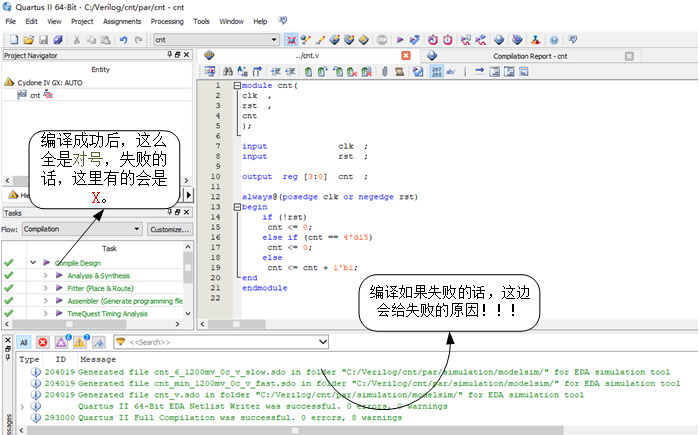

3-3:下面给出编译后的界面:

4:上面就是verilog代码的编译过程,对于代码设计而言,仿真是极其重要的,下面就介绍如何在Quartus中生成仿真测试文件的模板?如何调用Modelsim进行仿真?如何看波形?

4:上面就是verilog代码的编译过程,对于代码设计而言,仿真是极其重要的,下面就介绍如何在Quartus中生成仿真测试文件的模板?如何调用Modelsim进行仿真?如何看波形?

最后

以上就是年轻板凳最近收集整理的关于Quartus II 13.1入门级使用方法 适用于小白的全部内容,更多相关Quartus内容请搜索靠谱客的其他文章。

发表评论 取消回复