Quartus基础功能和SignalTap基本使用方法

- 基础:项目创建、编译和下载

- FPGA译码器组合逻辑

- 2_4译码器

- 计数器波形仿真和SignalTap

- 0-9计数器

- 0-17计数器及signaltap检验

- 0-17计数及方波发生器

- 显示输出

- 显示的问题

- SignalTap 报错记录

基础:项目创建、编译和下载

创建和编译比较基本,不写了。

指派管脚:

- 查阅板子说明来指派对应管脚;

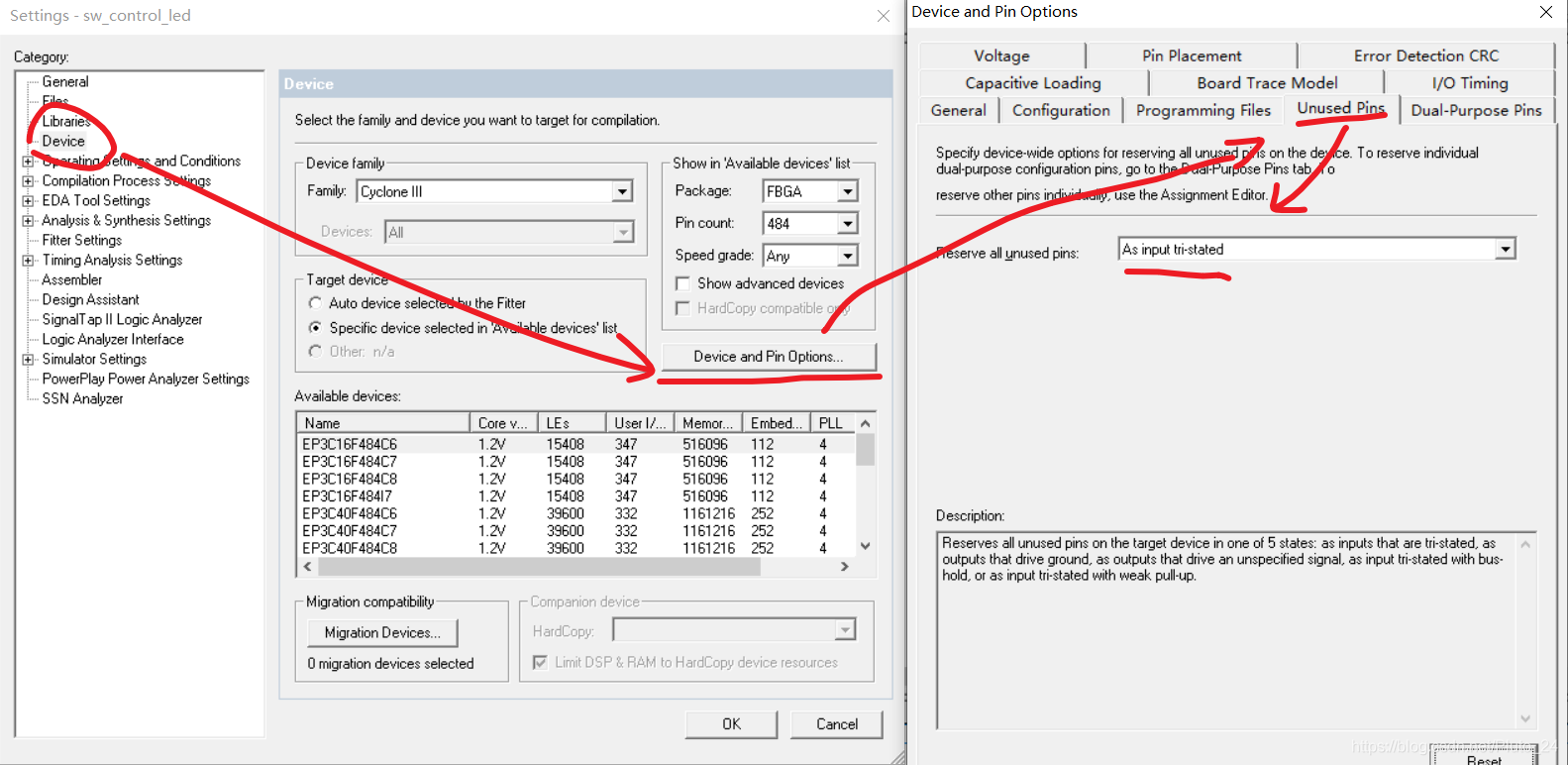

- 要将不用的管脚设置成三态。

设置方法:Assignments -> Settings -> Device -> Device and Pin Options -> Unused Pins -> As input tri-stated

module sw_control_led( swa , leda );

input swa;

output [9:0]leda;

reg [9:0]leda;

always @ (swa) begin

if (swa)

leda = 10'b1111111111;

else

leda = 10'b0000000000;

end

endmodule

名字设置为swa和leda是为了防止和系统命名冲突。命名为sw和led编译可以通过但是上板子的时候就会报错。

编译下载:Tools -> Programmer

现在Hardware Setup 里选择板子连接的端口,然后Start下载。下载完成后就可以操作板子验证一下了。

我在同时开多个文件的时候出现了问题,只有第一个可以下载运行,其他的不可以。只有完全关闭第一个的所有程序及quartus之后才能下载,否则就会报Can’t access JTAG chain。不是很懂。

FPGA译码器组合逻辑

2_4译码器

-

先建立顶层文件,设定为BDF格式。

顶层文件名与工程名相同,设置其他文件名与工程名不同。

-

在Files一栏中右键Files添加2_4译码器的Verilog代码。

这个代码文件不是必须在工程文件夹中。最好不要随意移动文件位置,否则以后用的时候可能会找不到文件。

可以提前写好这个文件。或者先写这个文件,保存之后再创建工程。

2_4译码器代码:

module dec_2to4(

IN ,

OUT);

input [2-1:0] IN ;

output [4-1:0] OUT ;

reg [4-1:0] OUT ;

always @ (IN) begin

case(IN)

2'b00: OUT = 4'b 0001;

2'b01: OUT = 4'b 0010;

2'b10: OUT = 4'b 0100;

2'b11: OUT = 4'b 1000;

endcase

end

endmodule // module dec_2to4;

-

为代码创建符号以在顶层文件中使用。

在Files中右键文件名,选择Creat Symbol Files for Currennt File,会在工程文件夹中生成一个代码文件对于的符号模块。这个模块可以在BDF文件中调用。

-

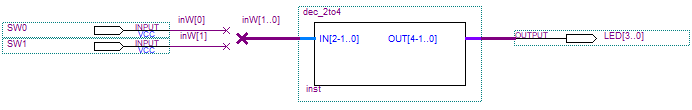

在BDF顶层文件中画图,调用模块。

注意使用网标式接线方法。

总线名格式为’name[3…0]’,单独的线名字格式为’name[3]’,编译时会自动连接。

名字设置方法:右键导线 -> properties -> name

- 编译。设置引脚。编译。上板子。

计数器波形仿真和SignalTap

0-9计数器

与上同,设计计数器文件。

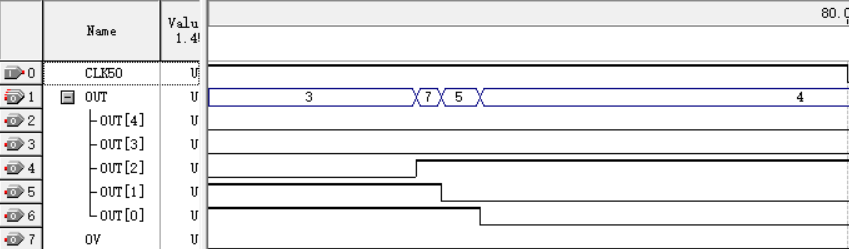

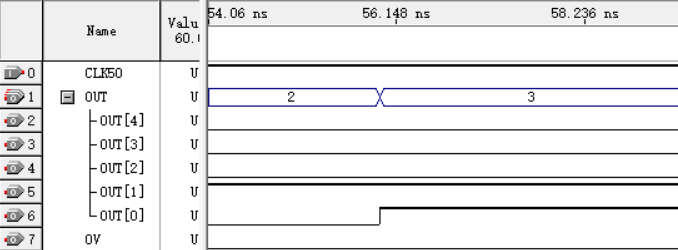

仿真文件如图。计数值中间的毛刺是电路元件延时信号跳变不一致导致的。

3到4之间有三个信号的跳变,而2到3只有一个信号的跳变,所以3到4有过渡的信号7和5,而2到3之间没有过渡的信号。

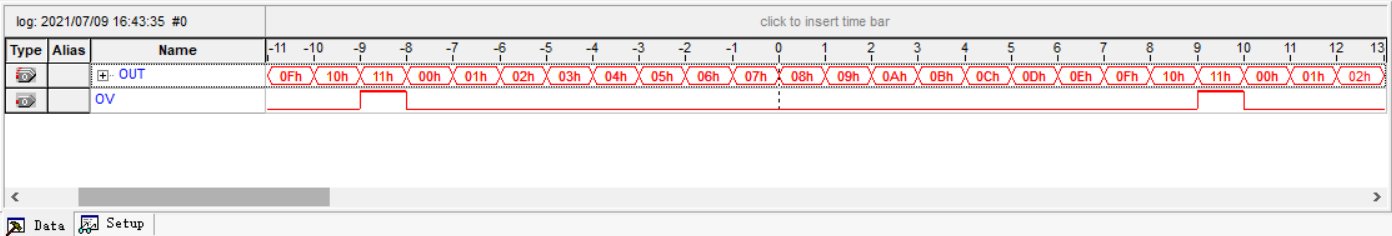

0-17计数器及signaltap检验

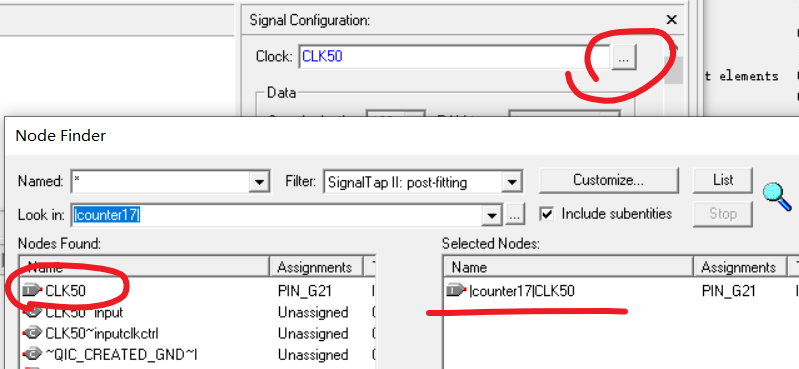

首先选择采样时钟

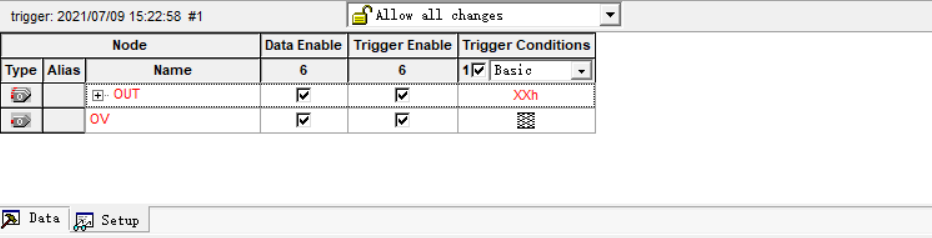

在setup框内双击然后选择要观察的数据信号

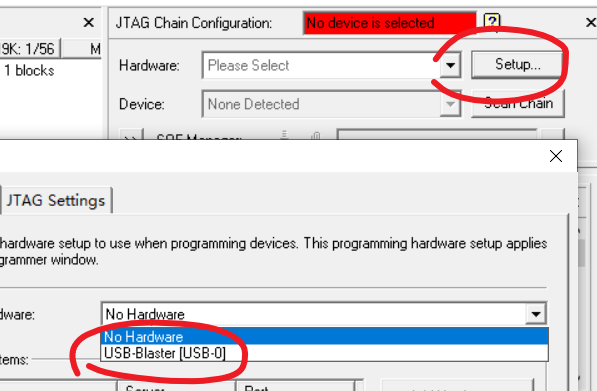

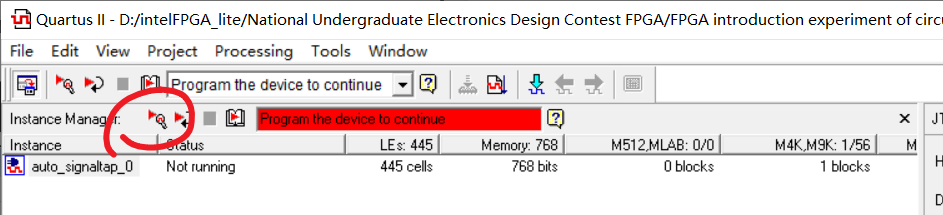

下载程序到板子上,然后在signaltap里右上角JTAG设置中选择硬件

最后编译

在Data里查看数据并进行分析

0至17计数并在17时OV输出1,输出正确无误。

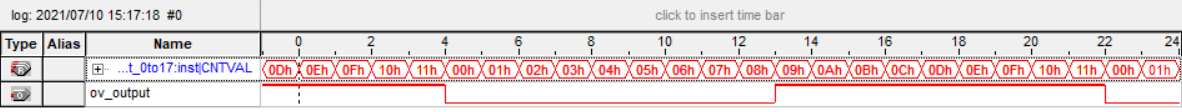

0-17计数及方波发生器

只需要在Verilog里将OV输出时的判断语句更改一下即可。

SignalTap验证结果:

显示输出

如果把OV接到一个LED上,那么可以依输出看到不同的现象。

对于第一个0-17计数器,仅在计数值为17时OV输出1,那么将会看到LED微弱的亮光或者几乎不亮。这是因为亮光频率高而时间太短,灯光微弱,眼睛反应不过来,所以看上去几乎不亮。

如果把占空比改为0.5,那么由于视觉暂留效应,我们几乎无法察觉LED的闪烁,所以看上去几乎是一直在发光。

如果再把计数值增大,增大到25000000级别,那么LED的交替周期就超过了0.2秒,这时候LED的闪烁就可以看得很清晰了。

显示的问题

没用到的LED也可能会亮。这是因为这些管脚是客观存在的,它们上面有客观存在的电压,如果不去设置,那么就是默认的电压,给LED不同的亮度,就会产生不同的现象。

解决方法:将不用的管脚设置成三态。

SignalTap 报错记录

若显示Error: Can’t run SignalTap II Logic Analyzer – SignalTap II File is not compatible with the file programmed in the device,表示文件与设备中编程的文件不兼容,问题在于没有先下载到板子上再运行SignalTap。

最后

以上就是积极猎豹最近收集整理的关于Quartus基础功能和SignalTap基本使用方法的全部内容,更多相关Quartus基础功能和SignalTap基本使用方法内容请搜索靠谱客的其他文章。

发表评论 取消回复