Verilog练习结果记录

- 一、HDLBits网站练习

- 1.门电路

- 2.组合电路

- 3.时序电路

- 二、小结

一、HDLBits网站练习

进入HDLBits网址练习

总的参考链接:在这里

1.门电路

练习题目链接

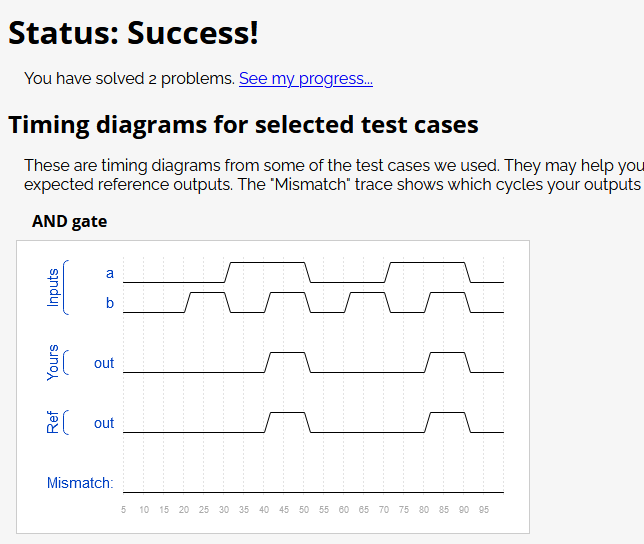

- 与门 and gate

module top_module(

input a,

input b,

output out );

assign out=a&b;

endmodule

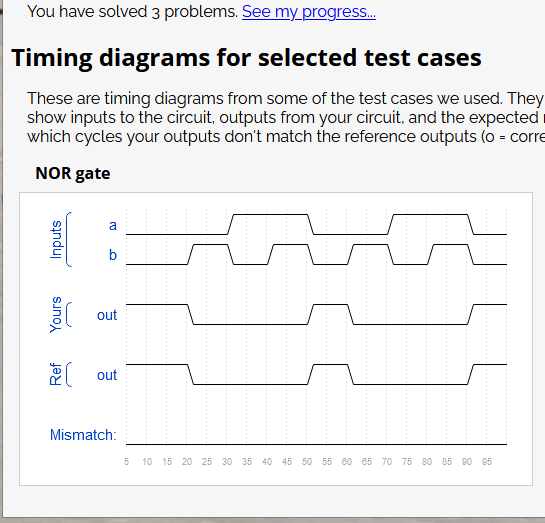

- 或非门 nor gate

或门的输出取反。

module top_module(

input a,

input b,

output out );

assign out=~(a|b);

endmodule

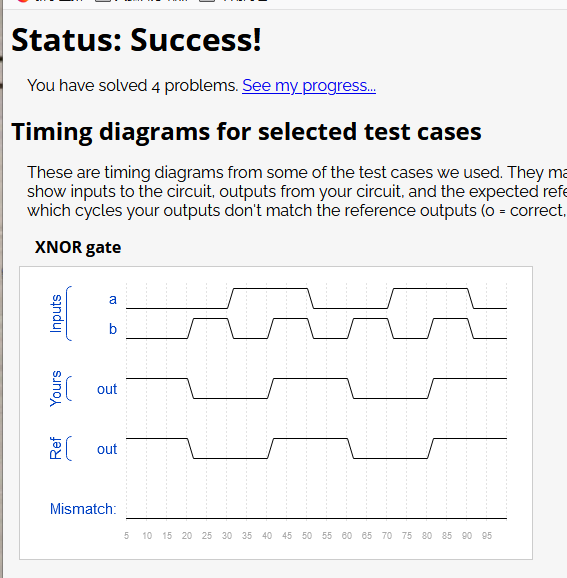

- 同或门

异或门的取反输出

module top_module(

input a,

input b,

output out );

assign out=~(a^b);

endmodule

^ 为逐位异或,Verilog 中不存在逻辑异或符号。

参考链接:在这里

2.组合电路

练习链接

- 半加法器 Half adder

实现一个 2 进制 1bit 加法器,加法器将输入的两个 1bit 数相加,产生两数相加之和以及进位

module top_module(

input a, b,

output cout, sum );

assign {cout,sum}=a+b;

endmodule

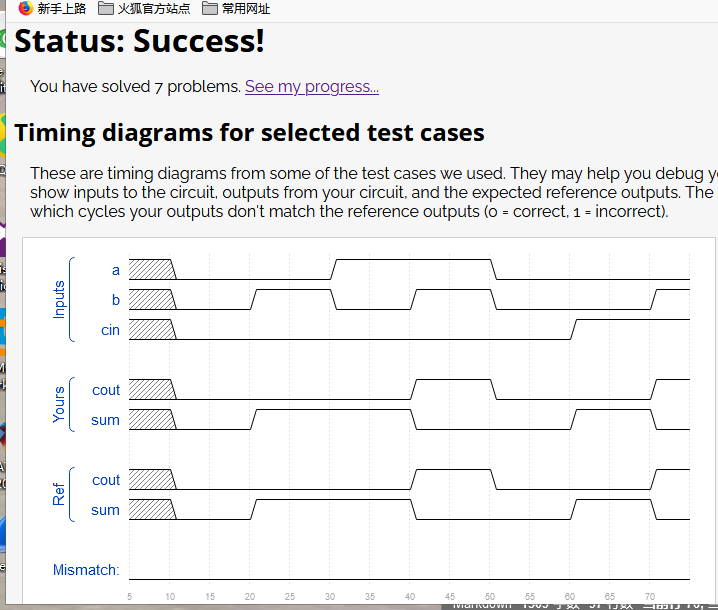

- 全加器 Full adder

实现一个 2 进制 1bit 全加器,将输入的两个 1bit 数相加,同时累加来自前级的进位,产生相加之和以及进位。

module top_module(

input a, b, cin,

output cout, sum );

assign {cout,sum} = a + b + cin;

endmodule

- 全加法器 Adder

4-bit 全加器。

module top_module (

input [3:0] x,

input [3:0] y,

output [4:0] sum);

assign sum=x+y;

endmodule

参考链接:在这里

3.时序电路

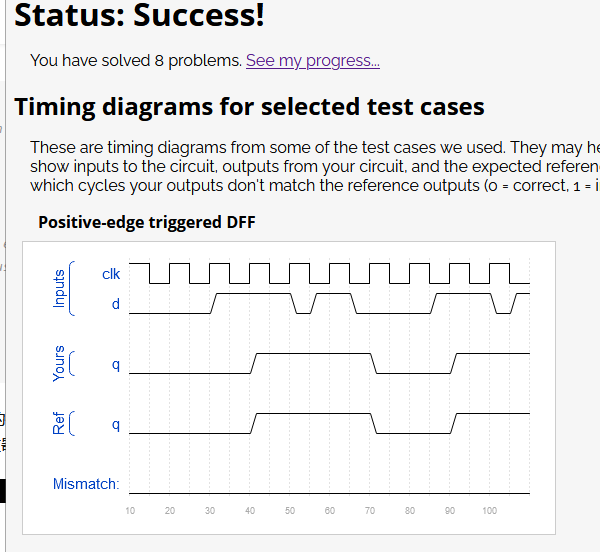

- D-触发器 D flip-flop

题目链接

D 触发器是一个电路,存储 1bit 数据,并定期地根据触发器的输入(d)更新这 1 bit 数据,更新通常发生在时钟上升沿(clk)。存储的数据会通过输出管脚(q)输出。

module top_module (

input clk, // Clocks are used in sequential circuits

input d,

output reg q );//

// Use a clocked always block

// copy d to q at every positive edge of clk

// Clocked always blocks should use non-blocking assignments

always @(posedge clk)

begin

q<=d;

end

endmodule

参考链接:在这里

参考链接:在这里

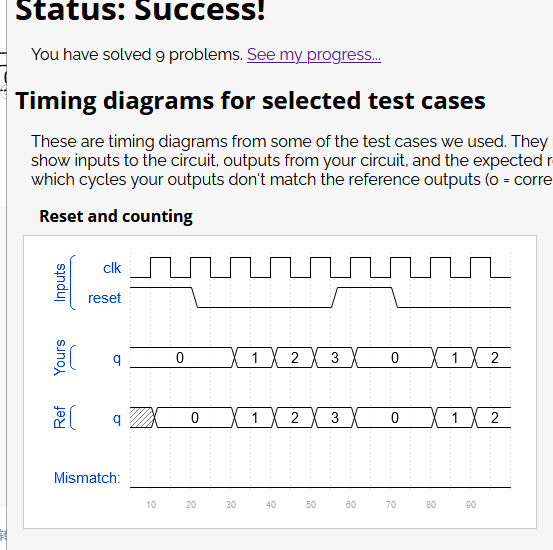

- 4位2进制计数器 Four-bit binary counter

题目链接

4bit的计数器,从0~15,共16个周期。reset是同步复位且复位为0。

module top_module (

input clk,

input reset, // Synchronous active-high reset

output [3:0] q);

always @ (posedge clk)

begin

if(reset)

q <= 4'b0000;

else

q <= q + 1'b1;

end

endmodule

参考链接:在这里

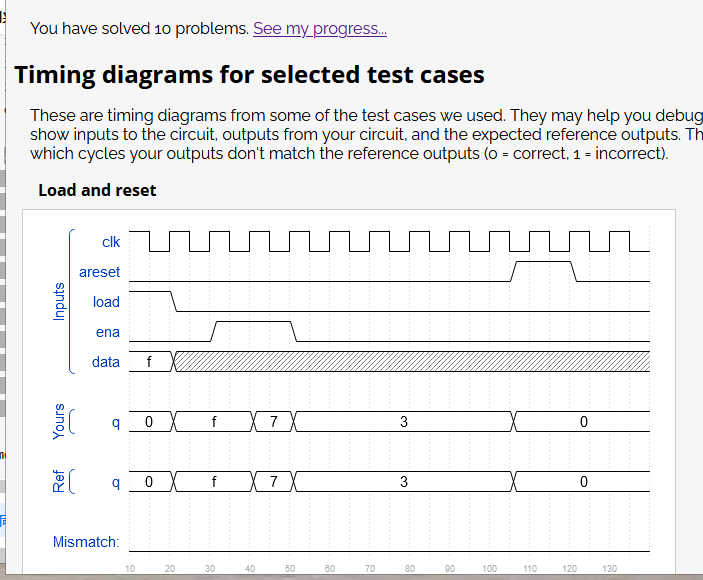

- 4位移位寄存器

题目链接

一个4bit异步复位,拥有同步置位和使能的右移移位寄存器。

module top_module(

input clk,

input areset, // async active-high reset to zero

input load,

input ena,

input [3:0] data,

output reg [3:0] q);

always @ (posedge clk or posedge areset)

begin

if(areset)

q <= 4'b0;

else if (load)

q <= data;

else if (ena)

begin

q[3:0] <= {1'b0, q[3:1]};

//q[3]q[2]q[1]q[0] --> 0q[3]q[2]q[1],q[0]在移动后消失了,原先q[3]的位置变为0

end

end

endmodule

参考链接:在这里

参考链接:在这里

二、小结

感叹网上资源的丰富多彩。有时间还是要继续练习

最后

以上就是朴实鱼最近收集整理的关于Verilog编程练习的全部内容,更多相关Verilog编程练习内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复