Verilog数字系统设计——方式可控的移位寄存器

题目

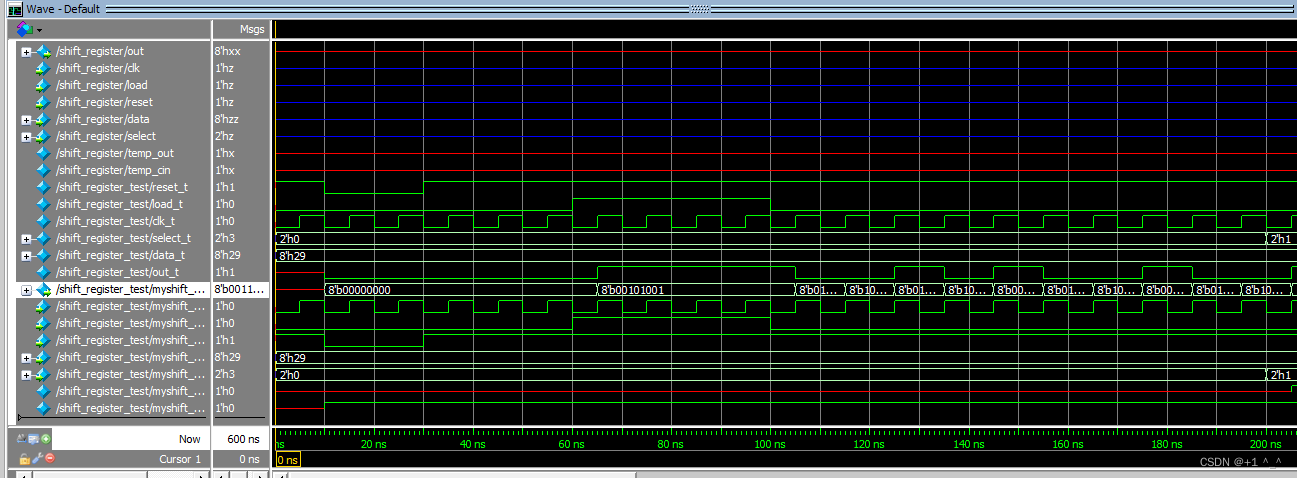

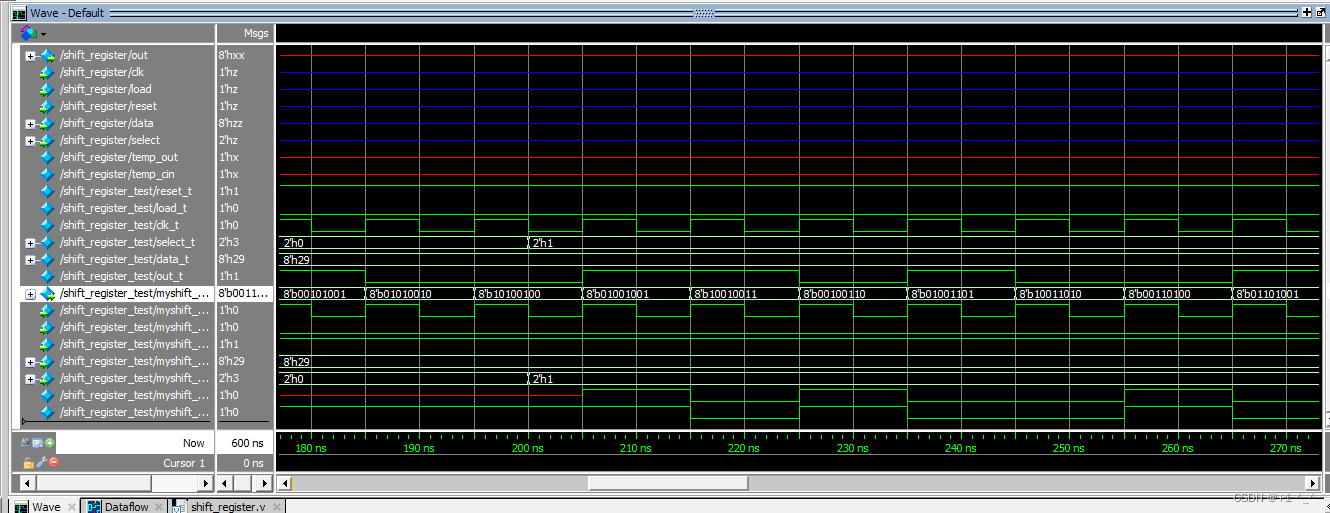

- 编程实现方式可控的移位寄存器,移位方式共有四种:a、自循环左移;b、带进位位循环左移;c、自循环右移;d、带借位位的循环右移。寄存器异步复位。

- 仔细考虑功能模块端口定义。

- 要求完成程序编辑、编译、时序仿真;

- 实验提交Verilog设计文件(.v文件)、仿真波形截图文件打包,压缩包以自己的学号+姓名命名;

下面展示一些内联代码片。

module shift_register(out,reset,load,clk,data,select);

output [7:0]out;

input clk,load,reset;

input [7:0]data;

input [1:0]select;

reg temp_out;

reg temp_cin;

reg [7:0]out;

always @(posedge clk or negedge reset)

begin

if(!reset)

begin

out=0;

temp_cin=1;

end

else if(load)

begin

out=data;

temp_cin=1;

end

else

begin

case(select[1:0])

2'b00:out<={out[6:0],out[7]};

2'b01:

begin

temp_out=out[7];

out={out[6:0],temp_cin};

temp_cin=temp_out;

end

2'b10:out<={out[0],out[7:1]};

2'b11:

begin

temp_out=out[0];

out={temp_cin,out[7:1]};

temp_cin=temp_out;

end

default:

out<=8'bxx;

endcase

end

end

Endmodule

module shift_register_test();

reg reset_t,load_t,clk_t;

reg [1:0]select_t;

reg [7:0]data_t;

shift_register myshift_register(.out(out_t),.reset(reset_t),.load(load_t),.clk(clk_t),.data(data_t),.select(select_t));

initial

begin

reset_t=1;

load_t=0;

data_t=8'b0010_1001;

clk_t=0;

select_t=2'b00;

#10 reset_t=0;

#20 reset_t=1;

#30 load_t=1;

#40 load_t=0;

end

always #5 clk_t=~clk_t;

always #200 select_t=select_t+1;

endmodule

最后

以上就是犹豫未来最近收集整理的关于【Verilog数字系统设计——方式可控的移位寄存器】Verilog数字系统设计——方式可控的移位寄存器的全部内容,更多相关【Verilog数字系统设计——方式可控内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复