- 利用MegaWizard实现创建RAM和ROM。(1)建立1个32单元8bit的RAM,并将0-31填入该RAM;(2)建立1个32单元8bit的ROM,建立.mif文件填入数据,并读出来显示。

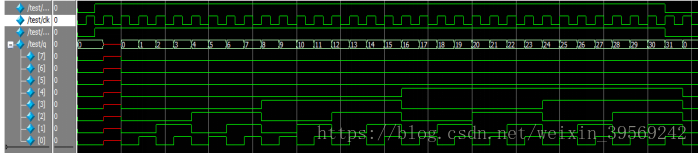

(1)、RAM

功能代码:

module shiyan41(clk,wren,reset,q);

input clk;

input wren;

input reset;

output [7:0] q;

reg [4:0] address;

reg [7:0] data;

RAM1 U1(address,clk,data,wren,q);

always @(posedge clk)

begin

if(!reset)

begin

address<=5'b0;

data <=8'b0;

end

else

begin

address<=address+1;

data<=data +1;

end

end

Endmodule

测试文件:

`timescale 1ns/1ns

module test();

reg reset,clk,wren;

wire[7:0] q;

shiyan41 U2(clk,wren,reset,q);

always #10 clk=~clk;

initial

begin clk=0;reset=0;wren=0;

#20 reset=1;wren=1;

#650 reset=0;wren=0;

#2000 $stop;

end

endmodule

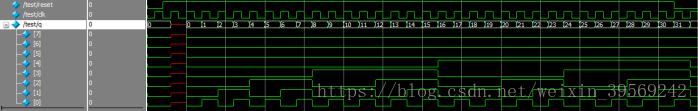

(2)ROM

功能代码:

module shiyan42(clk,reset,q);

input clk;

input reset;

output [7:0] q;

reg [4:0] address;

ROM1 U1(address,clk,q);

always @(posedge clk)

begin

if(!reset)

address<=5'b0;

else

address=address+1;

end

Endmodule

测试文件:

`timescale 1ns/1ns

module test();

reg reset,clk;

wire[7:0] q;

shiyan42 U2(clk,reset,q);

always #10 clk=~clk;

initial

begin clk=0;reset=0;

#20 reset=1;

#650 reset=0;

#2000 $stop;

end

endmodule

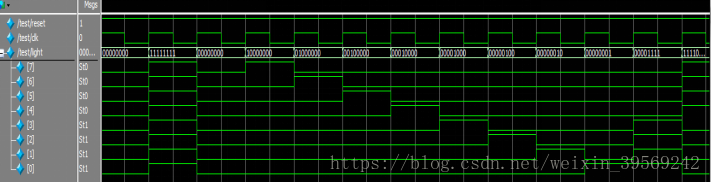

- 编写一个8路彩灯控制程序,要求彩灯有以下3种演示花型。

(1)8路彩灯同时亮灭;(2)从左至右逐个亮(每次只有1路亮);(3)8路彩灯每次4路灯亮,4路灯灭,且亮灭相间,交替亮灭;在演示过程中,只有当一种花型演示完毕才能转向其他演示花型。

功能代码:

module shiyan43(clk,light,reset);

input clk,reset;

output[7:0] light;

reg[3:0] state;

reg[7:0] light;

always @(posedge clk)

begin

if(!reset)

begin

light=8'b00000000;state=4'b0000;

end

else case(state)

4'b0000:begin light<=8'b11111111;state<=4'b0001;end

4'b0001:begin light<=8'b00000000;state<=4'b0010;end

4'b0010:begin light<=8'b10000000;state<=4'b0011;end

4'b0011:begin light<=8'b01000000;state<=4'b0100;end

4'b0100:begin light<=8'b00100000;state<=4'b0101;end

4'b0101:begin light<=8'b00010000;state<=4'b0110;end

4'b0110:begin light<=8'b00001000;state<=4'b0111;end

4'b0111:begin light<=8'b00000100;state<=4'b1000;end

4'b1000:begin light<=8'b00000010;state<=4'b1001;end

4'b1001:begin light<=8'b00000001;state<=4'b1010;end

4'b1010:begin light<=8'b00001111;state<=4'b1011;end

4'b1011:begin light<=8'b11110000;state<=4'b1100;end

4'b1100:begin light<=8'b00001111;state<=4'b0100;end

default:begin light<=8'b00000000;state<=4'b0000;end

endcase

end

endmodule

测试代码:

`timescale 1ns/1ns

module test();

reg reset,clk;

wire[7:0] light;

shiyan43 U2(clk,light,reset);

always #10 clk=~clk;

initial

begin clk=0;reset=0;

#10 reset=1;

#280 reset=0;

#20 reset=1;

#2000 $stop;

end

endmodule

最后

以上就是耍酷小蚂蚁最近收集整理的关于Verilog HDL语言实现ROM、RAM+有限状态机的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复