HDLBits网址:https://hdlbits.01xz.net/wiki/Main_Page

题目

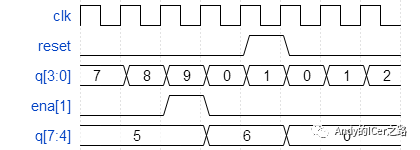

Build a 4-digit BCD (binary-coded decimal) counter. Each decimal digit is encoded using 4 bits: q[3:0] is the ones digit, q[7:4] is the tens digit, etc. For digits [3:1], also output an enable signal indicating when each of the upper three digits should be incremented.

我的设计

题目的意思就是设计一个16位的十进制BCD计数器(个位占4位,十位占4位,百位占4位,千位占4位),然后个位进位,十位进位,百位进位时,都输出一个使能信号,这里提供两种实现的方法,法一是直接实现,不例化模块;法二是先设计一个4位的BCD计数器,然后再例化为16位的BCD计数器。

法一

module top_module (input clk,input reset, // Synchronous active-high resetoutput [3:1] ena,output reg [15:0] q);always @(posedge clk)if (reset)begin // Count to 10 requires rolling over 9->0 instead of the more natural 15->0q <=0;endelse beginif(q[3:0] != 4'd9)q[3:0] <= q[3:0]+1;else beginq[7:4] <= q[7:4]+1;q[3:0] <= 0;if(q[7:4] == 4'd9)beginq[7:4] <= 0;q[11:8] <= q[11:8]+1;if(q[11:8] == 4'd9)beginq[11:8] <= 0;q[15:12] <= q[15:12]+1;if(q[15:12] == 4'd9)beginq <= 0;endendendendendassign ena[1]=(q[3:0] == 4'd9)?1:0;assign ena[2]=(q[7:4] == 4'd9 && q[3:0] == 4'd9)?1:0;assign ena[3]=(q[11:8] == 4'd9 && q[7:4] == 4'd9 && q[3:0] == 4'd9)?1:0;endmodule

法二

module count4(input clk,input reset,input ena,output reg[3:0] q);always @ (posedge clk)beginif(reset)q <= 4'b0;else if (ena)beginif(q == 4'd9)q <= 4'd0;elseq <= q + 1'b1;endendendmodulemodule top_module (input clk,input reset, // Synchronous active-high resetoutput [3:1] ena,output [15:0] q);wire en1, en2, en3, en4;assign en1 = 1;assign en2 = (q[3:0] == 4'd9);assign en3 = (q[7:4] == 4'd9 && q[3:0] == 4'd9);assign en4 = (q[11:8] == 4'd9 && q[7:4] == 4'd9 && q[3:0] == 4'd9);//onecount4 inst1_count4(.clk(clk),.reset(reset),.ena(en1),.q(q[3:0]));//tencount4 inst2_count4(.clk(clk),.reset(reset),.ena(en2),.q(q[7:4]));//hundredcount4 inst3_count4(.clk(clk),.reset(reset),.ena(en3),.q(q[11:8]));//thousandcount4 inst4_count4(.clk(clk),.reset(reset),.ena(en4),.q(q[15:12]));//用来表示进位assign ena = {q[11:8] == 4'd9 && q[7:4] == 4'd9 && q[3:0] == 4'd9, q[7:4] == 4'd9 && q[3:0] == 4'd9, q[3:0] == 4'd9};endmodule

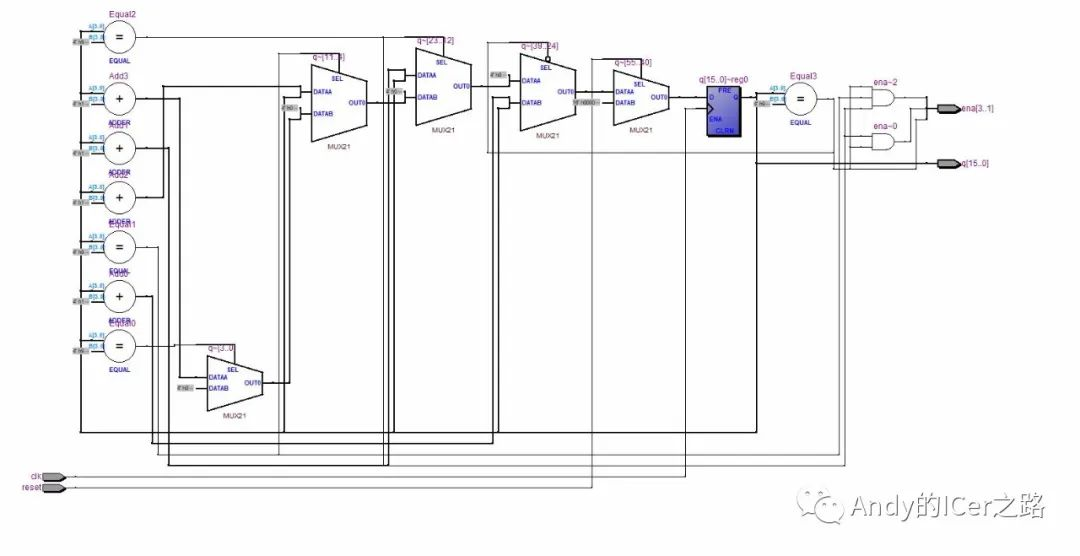

综合的电路

微信公众号

建立了一个微信公众号“Andy的ICer之路”,此公众号主要分享数字IC相关的学习经验,做公众号的目的就是记录自己的学习过程,很多东西回过头来可能就忘记了,为了记住知识和分享知识,希望自己可以保持更新,有兴趣的朋友可以关注一下!

最后

以上就是优秀蜜粉最近收集整理的关于Verilog专题(十四)BCD码计数器的设计题目我的设计微信公众号的全部内容,更多相关Verilog专题(十四)BCD码计数器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复