Verilog应用——24秒篮球计数器

- 设计思路

- 变模计数器

- 思路

- 代码实现

- 设计模块

- 测试模块

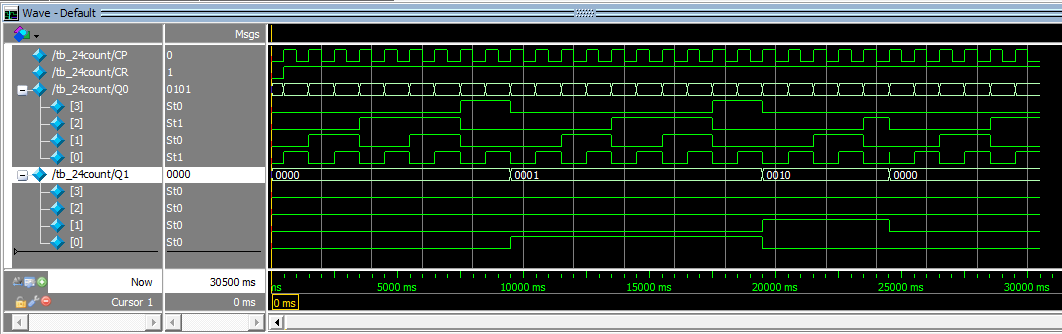

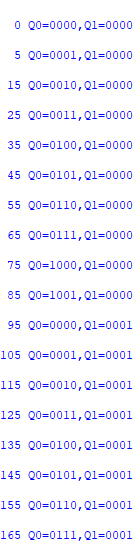

- 仿真结果

- 显示

- 思路

- 代码显示

- 设计模块

- 测试模块

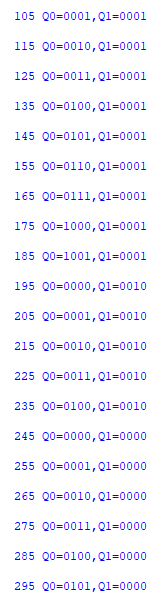

- 仿真

设计思路

需要一个模3计数器和模10计数器,这里需要设计一个可变模数的计数器,并对两个计数器进行级联。显示模块则采用最常用的七段显示器,这里需要注意的是,当十位数为0时,应该令显示器熄灭,合理控制计数器控制端即可。

变模计数器

思路

采用行为级建模。

代码实现

设计模块

//filename:_24count.v

module varmodcnt(CP,CLR,EN,Q,carry_out);

parameter n=4,MOD=10;

input CP,CLR,EN;

output reg[n-1:0] Q;

output carry_out;

/*参数说明:

输入:CP为时钟信号,CLR为清零信号,EN为使能信号

输出:Q为输出,carry_out为进位信号

*/

//敏感信号:CP上升沿,CLR下降沿

always@(posedge CP,negedge CLR)

begin

if(!CLR) Q<='d0;//置零

else if(!EN) Q<=Q; //保持

else begin

if(Q==MOD-1) Q<='d0; //达到MOD-1,归零

else Q<=Q+1;//未达到MOD-1时,加一

end

end

assign carry_out=(Q==MOD-1); //Q=MOD-1时,进位信号有效

endmodule

module _24count(

input CP,

input CR,

output [3:0]Q0,Q1);

/*端口说明:

输入:

CP为时钟信号,CR为输入清零信号

输出:

Q1为十位上数字对应的四位二进制,Q0为十位上数字对应的四位二进制数

*/

//中间变量:TC进位信号,CLR为为24模的清零信号

wire TC0,TC1;

wire CLR;

varmodcnt #(4,10) U0(CP,CLR,EN,Q0,TC0); //个位信号

varmodcnt #(4,3) U1(CP,CLR,TC0,Q1,TC1); //十位信号

assign CLR=CR&(~({Q1,Q0}==8'b0010_0101)); //当外部清零信号有效或者输出为24时,进行清零

endmodule

测试模块

//filename:tb_24count

`timescale 100ms/10ms

module tb_24count();

reg CP;

reg CR;

wire [3:0] Q0,Q1;

/*端口说明:

输入:

CP为时钟信号,CR为输入清零信号

输出:

Q1为十位上数字对应的四位二进制,Q0为十位上数字对应的四位二进制数

*/

//中间

_24count U(CP,CR,Q0,Q1);

initial

$monitor($time,"tQ0=%b,Q1=%bn",Q0,Q1);

//时钟信号

initial

CP=0;

always

#5 CP=~CP;

//元件例化

initial

begin

//清零

CR=0;

#5;

//计数25s

CR=1;

#300;

$stop;

end

endmodule

仿真结果

显示

思路

七段显示器74HC4511之前已经进行了仿真,这里只需注意十位显示器的控制输入应该在十位为0的时候无效。注意这一点即可。

代码显示

设计模块

//filename:_24show.v

module _24show(

input CP,CR,BL,LT,

output [6:0] L1,L0);

/*端口描述:

CP为时钟信号,CR为清零信号,BL,LT实现灭灯和灯测试

*/

wire [3:0]Q0,Q1;

wire BL1;

_24count U(CP,CR,Q0,Q1);

assign BL1=BL&(Q1!=4'b0000);//十位显示器的控制输入应该在十位为0的时候无效

_74HC4511 U1(1'b0,BL,LT,Q1,L1);

_74HC4511 U0(1'b0,BL,LT,Q0,L0);

endmodule

module _74HC4511(

input LE,BL,LT,

input [3:0] D,

output reg [6:0] L); //输入输出

wire [2:0] E;

assign E={LE,BL,LT}; //中间变量用于后续的控制端优先级判断

always@(*)

begin

if(LE==0&&BL==1&<==1)

begin

case(D)

4'b0000:L=7'b111_1110;

4'b0001:L=7'b011_0000;

4'b0010:L=7'b110_1101;

4'b0011:L=7'b111_1001;

4'b0100:L=7'b011_0011;

4'b0101:L=7'b101_1011;

4'b0110:L=7'b001_1111;

4'b0111:L=7'b111_0000;

4'b1000:L=7'b111_1111;

4'b1001:L=7'b111_1011;

4'b1010:L=7'b000_0000;//以下为无效状态

4'b1011:L=7'b000_0000;

4'b1100:L=7'b000_0000;

4'b1101:L=7'b000_0000;

4'b1110:L=7'b000_0000;

4'b1111:L=7'b000_0000;

endcase

end

else

begin

casex(E)

3'bxx0:L=7'b111_1111; //灯测试

3'bx01:L=7'b000_0000; //灭灯

3'b111:L<=L; //锁存

endcase

end

end

endmodule

//filename:_24count.v

module _24count(

input CP,

input CR,

output [3:0]Q0,Q1);

/*端口说明:

输入:

CP为时钟信号,CR为输入清零信号

输出:

Q1为十位上数字对应的四位二进制,Q0为十位上数字对应的四位二进制数

*/

//中间变量:TC进位信号,CLR为为24模的清零信号

wire TC0,TC1;

wire CLR;

varmodcnt #(4,10) U0(CP,CLR,EN,Q0,TC0); //个位信号

varmodcnt #(4,3) U1(CP,CLR,TC0,Q1,TC1); //十位信号

assign CLR=CR&(~({Q1,Q0}==8'b0010_0101)); //当外部清零信号有效或者输出为24时,进行清零

endmodule

测试模块

//filename:tb_show.v

`timescale 100ms/10ms

module tb_show();

reg CP,CR;

reg BL,LT;

wire [6:0] L1,L0;

_24show U3(CP,CR,BL,LT,L1,L0); //实例化元器件

initial

$monitor($time,"tL1=%b,L0=%bn,",L1,L0);

//时钟信号

initial

CP=0;

always

#5 CP=~CP;

initial

begin

//清零

CR=0;BL=1'b1;LT=1'b1;

#5;

//24s计时器开始计数

CR=1;BL=1'b1;LT=1'b1;

#300;

$stop;

end

endmodule

仿真

最后

以上就是坚强御姐最近收集整理的关于Verilog应用——24秒篮球计数器设计思路变模计数器显示的全部内容,更多相关Verilog应用——24秒篮球计数器设计思路变模计数器显示内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复