3.1标识符

1.Verilog中的Identifier是由任意字母、数字、下划线和$符号组成的,第一个字符必须是字母或者下划线。区分大小写。

2.Escaped Identifier是为了解决简单标识符不能以数字和$符号开头的缺点。如下所示:

3.关键字。我的理解是保留字包括关键字,verilog中关键字都是小写的。

3.2注释

- /* */

2. //

3.3格式

语句结构既可以跨越多行编写,也可以在一行内编写。

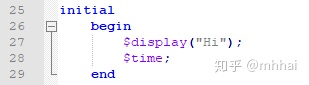

3.4系统任务和系统函数

以$开头的标识符被认为是系统任务或者系统函数。任务可以返回0个或者多个值,函数只能返回一个值。函数的执行不允许由任何延迟,任务可以有延迟。但是系统任务不能有延迟。简单做个测试,但是发现控制台没有输出。

3.5编译器指令

某些以`(反引号)开头的标志符是编译器指令。

1. `define和`undef指令:宏定义以及取消前面的宏。

2.`ifdef、`ifndef、`else、`elseif和`endif:条件编译。

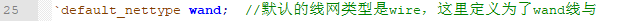

3.`default_nettype:该指令用于为隐式线网指定线网类型。

4.`include:可以包含其他文件的内容(替换的方式)。绝对路径和相对路径都可以。

5.`resetall:将所有的编译指令重新设置为缺省值。

6.`timescale:一般放在模块声明的外部,影响其后所有的延迟值。直到遇到另一个`timescale指令或者`resetall指令。

3.6值集合

Verilog中有四种基本值:0,1,x,z。其中x、z是不区分大小写的。这四种基本值构成了Verilog语言中3种类型的常数:Integer、Real和String。下划线可以自由地在整数中或者实数中使用,用来改进常量的易读性。

3.6.1整数型

1.简单的十进制:+、-这两个操作符只能作用于十进制,不能作用于其他进制。

2.基数格式表示法:

[size] '[signed] base value

基数格式的数通常为无符号数。若某整型数的位宽没有定义,则默认是32位的。无符号数在左边补零,有符号数在左边补符号位。若数的最左边是x或者z,则补x或z。

base是必须要有的。

3.6.2实数

1.十进制:小数点两侧必须有数字。

2.科学计数法:23_5.1e2。

Verilog将实数隐式地转换成整数。

3.6.3字符串

字符串是双引号括起的字符序列。字符串是8位ASCII值的序列。

3.7数据类型

Verilog有两大数据类型:Net Type和Variable Type。

3.7.1线网类型

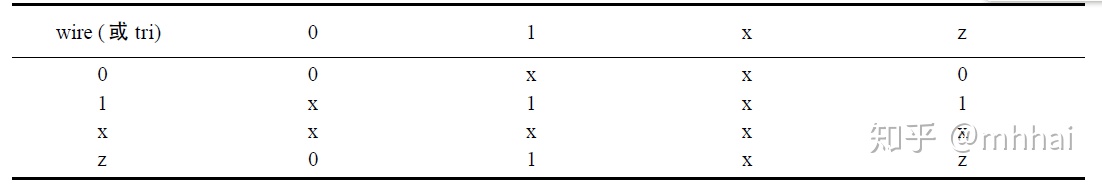

关于这部分,多个激励源驱动的线网,线网的值有效值由表决定。

3.7.2未声明的线网

3.7.3向量线网和标量线网

3.7.4变量类型

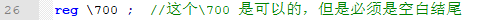

1.reg变量类型

使用了关键词signed的reg变量,会以补码的形式保存。

2.存储器

存储器是由reg变量组成的数组。存储器声明格式如下:

reg[[msb : lsb]] memory1[upper1 : lower1], ...;

存储器中的每一个元素被称为字,对存储器赋值可以分别对存储器中的每个字进行赋值。文中提到了使用for循环对存储器进行赋值。还可以使用$readmemb和$readmemh这两个函数对存储器进行赋值。

3.整型变量

整型变量的声明格式如下所示:

integer integer1, integer2, ... integerN[msb : lsb];

[msb : lsb]指定了整型数组的范围。一个整形数至少有32位。

整型能被当作向量处理。可以通过赋值将整数型转换为位向量。

4.time变量

5.real和realtime变量

3.7.5数组

看一下二维数组的声明:

integer 一维reg变量的数组也被称为存储器。不能对整个数组进行赋值。只能对数组的一个元素进行赋值。

3.8参数

参数声明语句的格式如下:

parameter [signed][msb : lsb] param1 = const_expr,...;

参数值在编译的时候可以使用defparam进行改变。参数是局部的,只能在其定义的模块内部其作用,而宏定义对同时编译的多个文件起作用。

最后

以上就是殷勤保温杯最近收集整理的关于verilog设置24进制计数器_阅读笔记:《Verilog HDL入门》第3章 Verilog语言要素的全部内容,更多相关verilog设置24进制计数器_阅读笔记:《Verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复