假如我有一些信号需要展开,信号的格式如下所示:

input.file

Hello/My/name/is/AAAAA[9:0]

Hello/My/name/is/BBBBB[0:7]

Hello/My/name/is/CCCCC[3:3]

Hello/My/name/is/DDDDD展开之后的格式如下所示:

Hello/My/name/is/AAAAA[9]

Hello/My/name/is/AAAAA[8]

Hello/My/name/is/AAAAA[7]

~~~此处省略若干行~~~

Hello/My/name/is/CCCCC[1]

Hello/My/name/is/CCCCC[0]

Hello/My/name/is/CCCCC[3]

Hello/My/name/is/DDDDD下面的python脚本(python2)可以实现这个功能:

expand_bus_bits.py

#!/usr/bin/python

import re

fh = open('./input.file')

for line in fh.readlines():

# print line

m = re.match(r'(.*)[(d+):(d+)]', line)

if m:

signal_name = m.group(1)

index0 = int(m.group(2))

index1 = int(m.group(3))

# print signal_name

# print index0

# print index1

# print signal_name + "[" + str(index0) + ":" + str(index1) + "]"

if (index0 > index1):

while (index0 >= index1):

print signal_name + "[" + str(index0) + "]"

index0 = index0 - 1

elif (index0 < index1):

while (index0 <= index1):

print signal_name + "[" + str(index1) + "]"

index1 = index1 - 1

else:

print signal_name + "[" + str(index0) + "]"

else:

print line执行的结果默认输出到屏幕上。

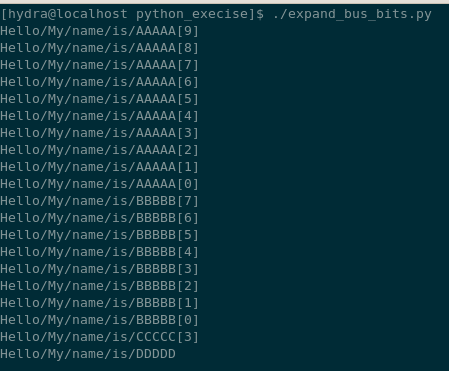

下面是输出的结果:

最后

以上就是冷艳钢笔最近收集整理的关于展开Verilog BUS信号名的方法的全部内容,更多相关展开Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复