verilog——移位寄存器实现

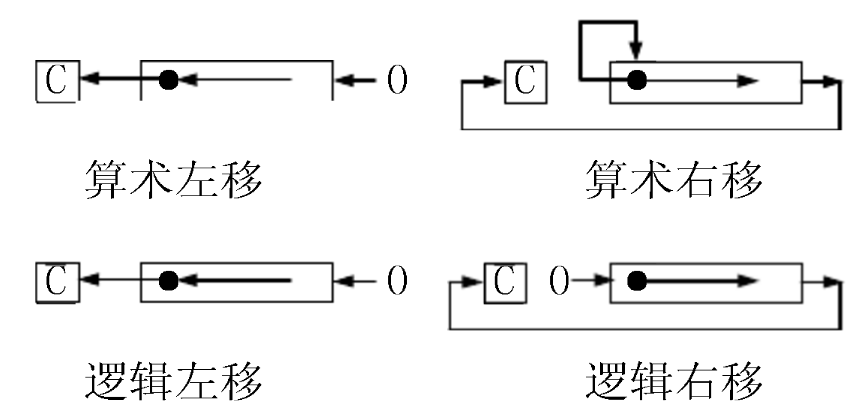

一、各种移位寄存器的原理

1.1、自循环移位

这里用例子说明较为清晰:

假如一个二进制数字是 1111100000

自循环左移 --> 1111000001 1110000011 1100000111 …

自循环右移 --> 0111110000 0011111000 0001111100 …

1.2、带进位位的循环移位

这里用例子说明较为清晰:

带进位的循环左移RCL(Rotate Left Through Carry):

用原CF的值填补空出的位,移出的位再进入CF。

假设当前,AL=01010011B,CF=1,则

执行指令 ROL AL,1

后,AL=10100110B,CF=0

执行指令 RCL AL,1

后,AL=10100111B,CF=0

最后一位的1,是先前CF的1

1.3、区别

具体区别可分为下面三种:

1.3.1、方式不同

循环左移:累加器自身循环向左移位。

带进位循环左移:累加器连同进位位一起左移。

1.3.2、过程不同

循环左移:移出的位不仅要进入CF,而且还要填补空出的位。

带进位循环左移:用原CF的值填补空出的位,移出的位再进入CF。

1.3.3、功能不同

循环左移:把操作数d,的各个二进制位向左移动d位,从d左端移出的每一位再依次移到右端空出的位上,最后移出的位还要送到CF中。

带进位循环左移:把操作数d的各位与CF联合在一起,构成9个或者17个二进制位,向左移动d位,从左端移出的各位再依次移到右端空出的位上。

二、代码实现

2.1、shift module

module shiftreg(out,reset,clk,data,select);

output reg [7:0] out; //output signal

input [1:0] select; //Status selection signal

input [7:0] data;

input reset,clk; //reset signal

reg CF,temp;

always @(posedge clk or posedge reset)

begin

if(reset) //reset signal

begin

out <= data;

CF <= 0;

end

else

begin

case(select)

2'b00: //ROL:Shift left from cycle

out <= {out[0],out[7:1]};

//用原CF的值填补空出的位,移出的位再进入CF

2'b01: //RCL:Cyclic left shift with carry

begin

temp = out[0];

out = {CF,out[7:1]};

CF = temp;

end

2'b10: //ROR:Rotate Right

out = {out[6:0],out[7]};

2'b11: //RCR:Rotate Right Through Carry

begin

temp =out[7];

out = {out[6:0],CF};

CF = temp;

end

default:out <= 8'bx;

endcase

end

end

endmodule

2.2、test module

module test_shiftreg;

reg clk_t,reset_t;

reg[1:0] select_t;

wire[7:0] out_t;

reg[7:0] data_t;

shiftreg myshift(

.out(out_t),

.reset(reset_t),

.clk(clk_t),

.data(data_t),

.select(select_t));

initial

begin

data_t = 8'b1011_0101;

reset_t = 1;

clk_t = 0;

select_t = 2'b11;

#20 reset_t = 0;

end

always #20 clk_t = ~clk_t; //clock signal

endmodule

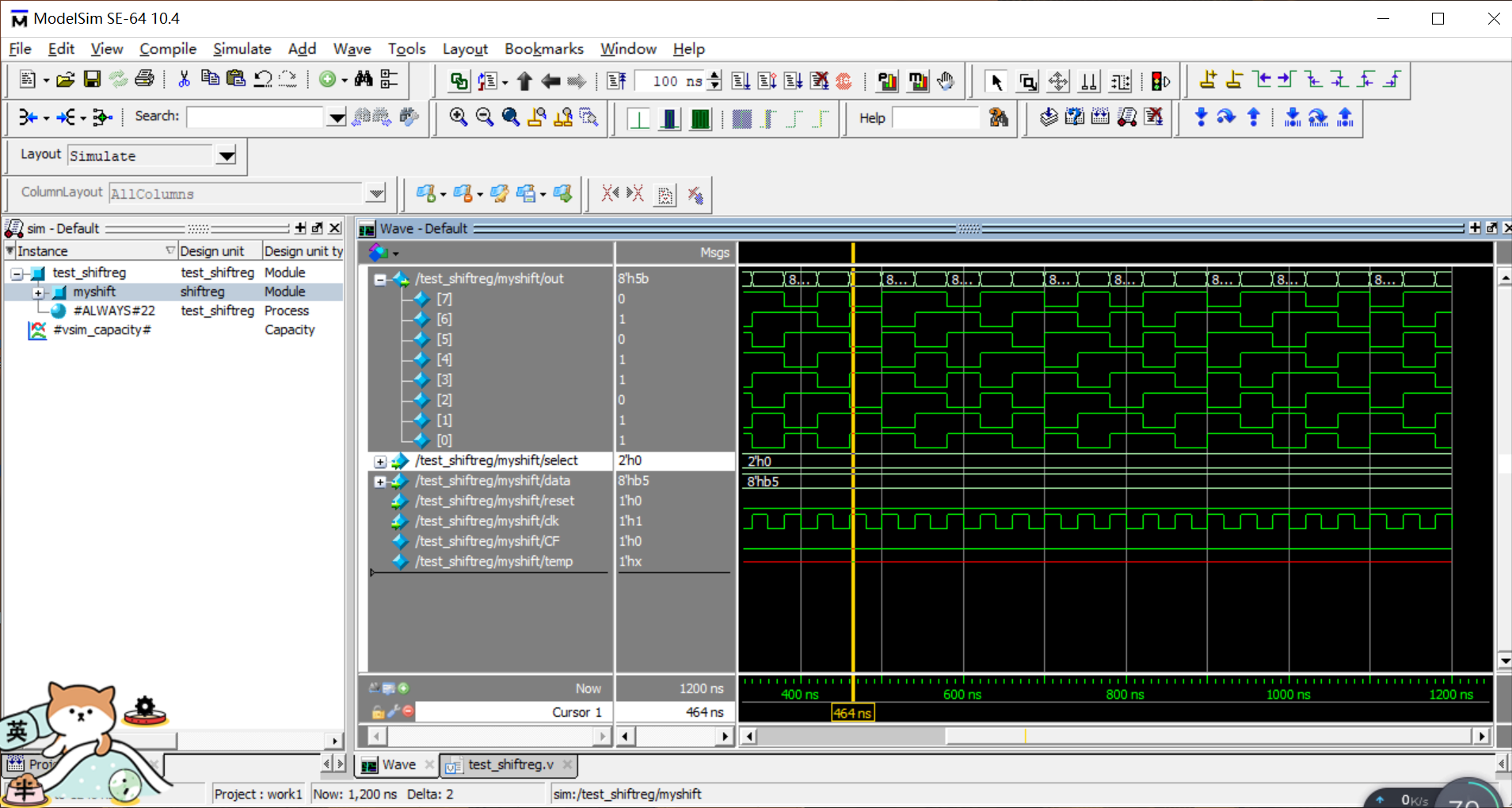

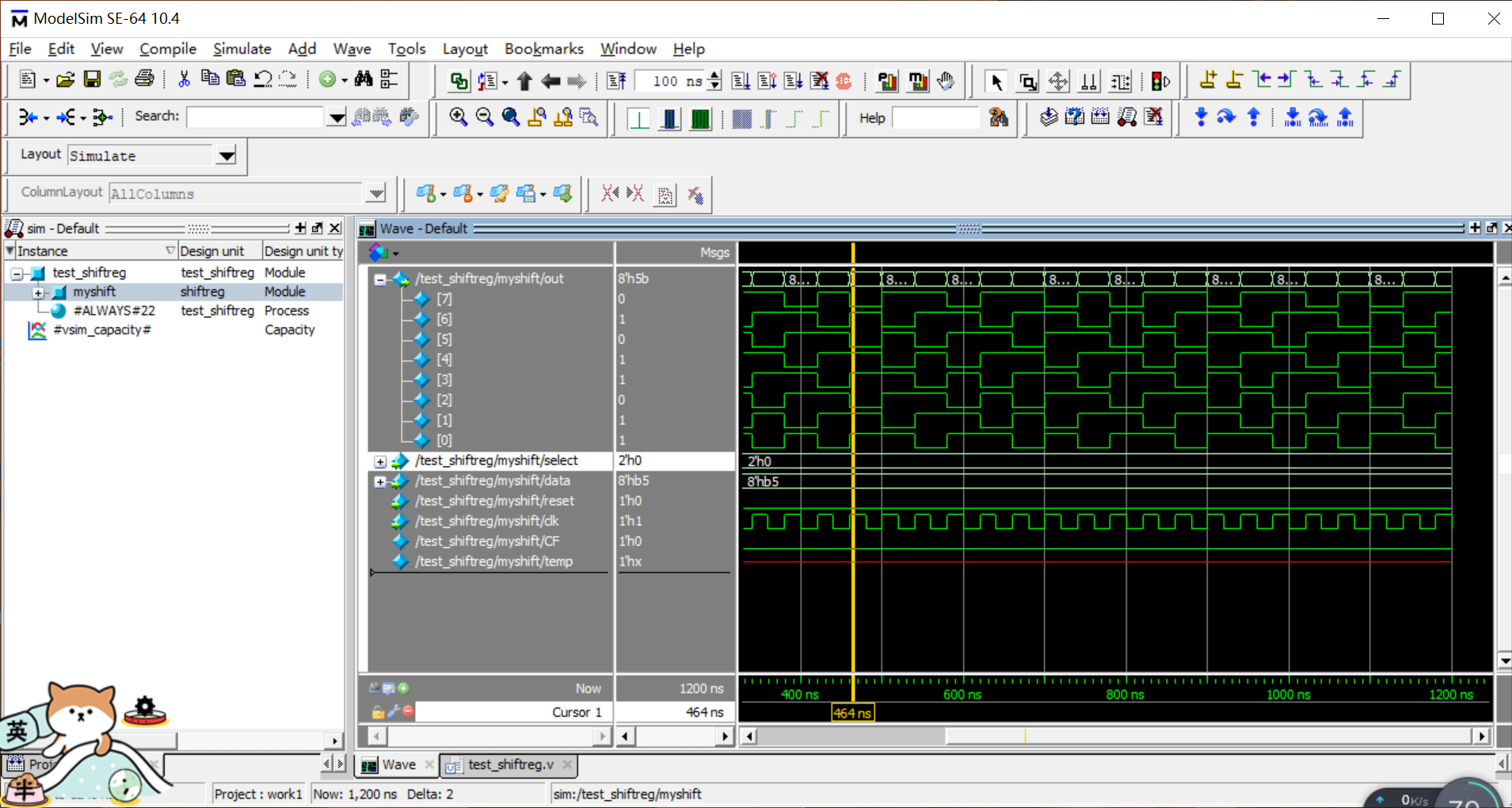

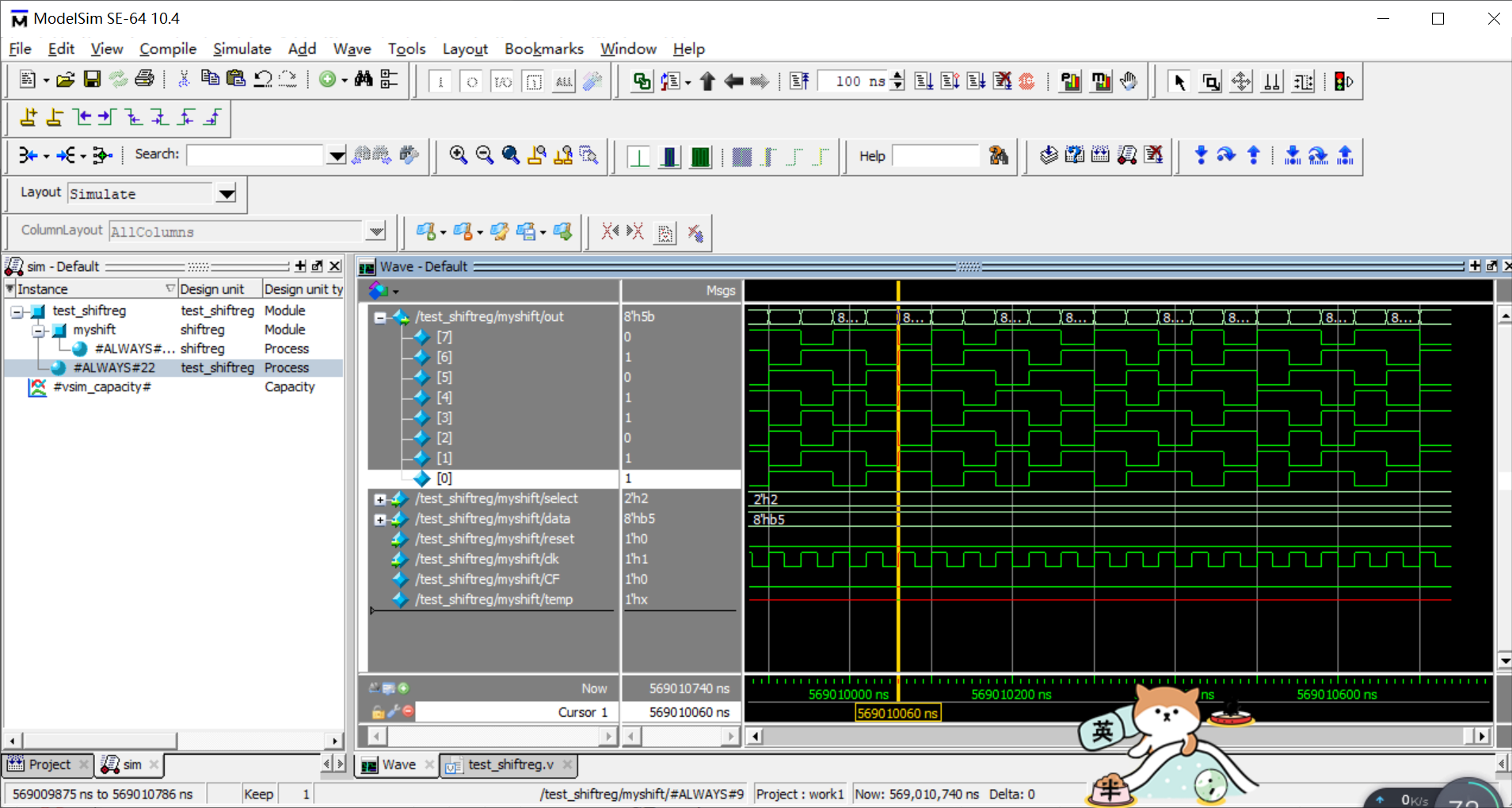

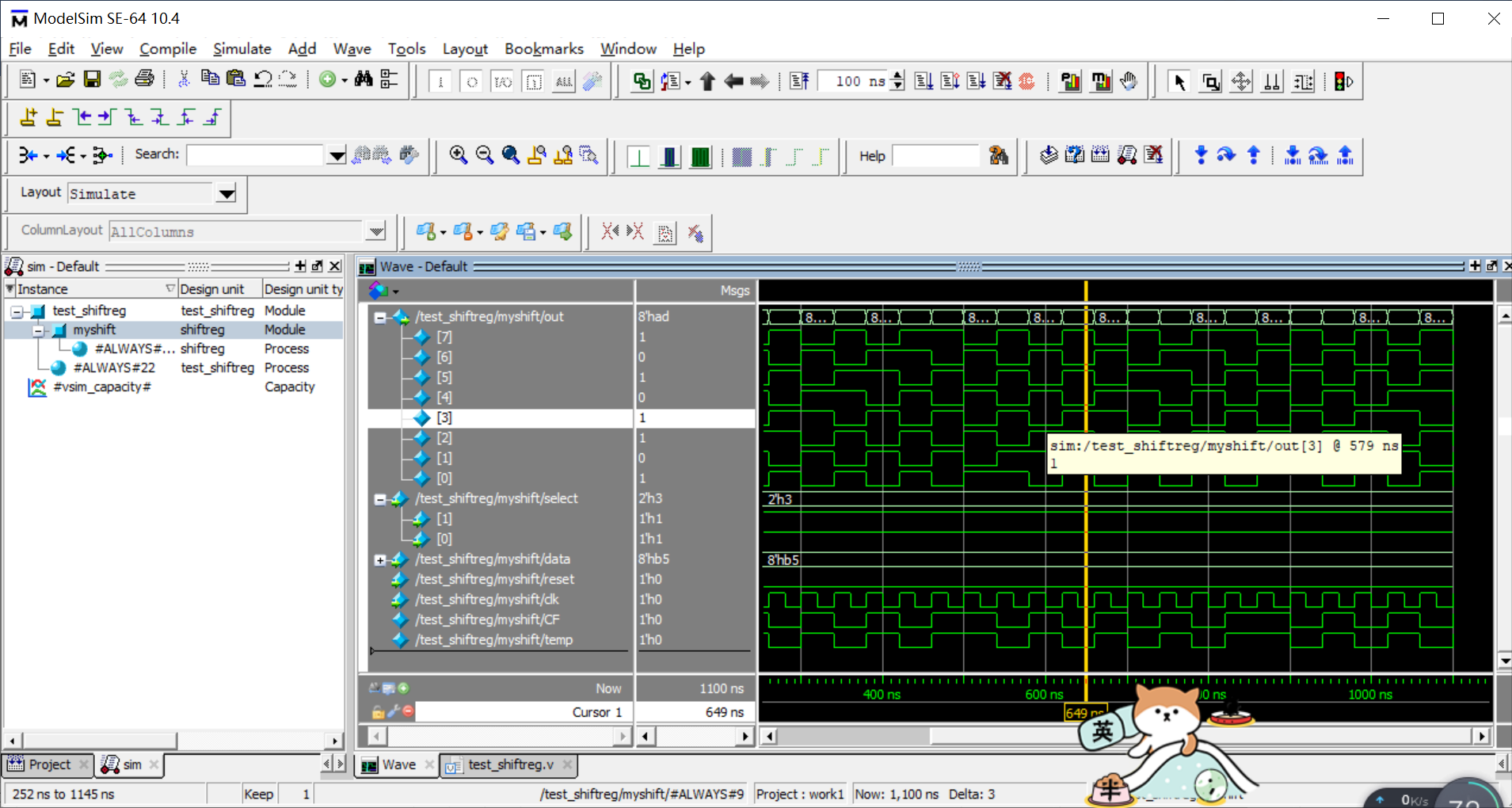

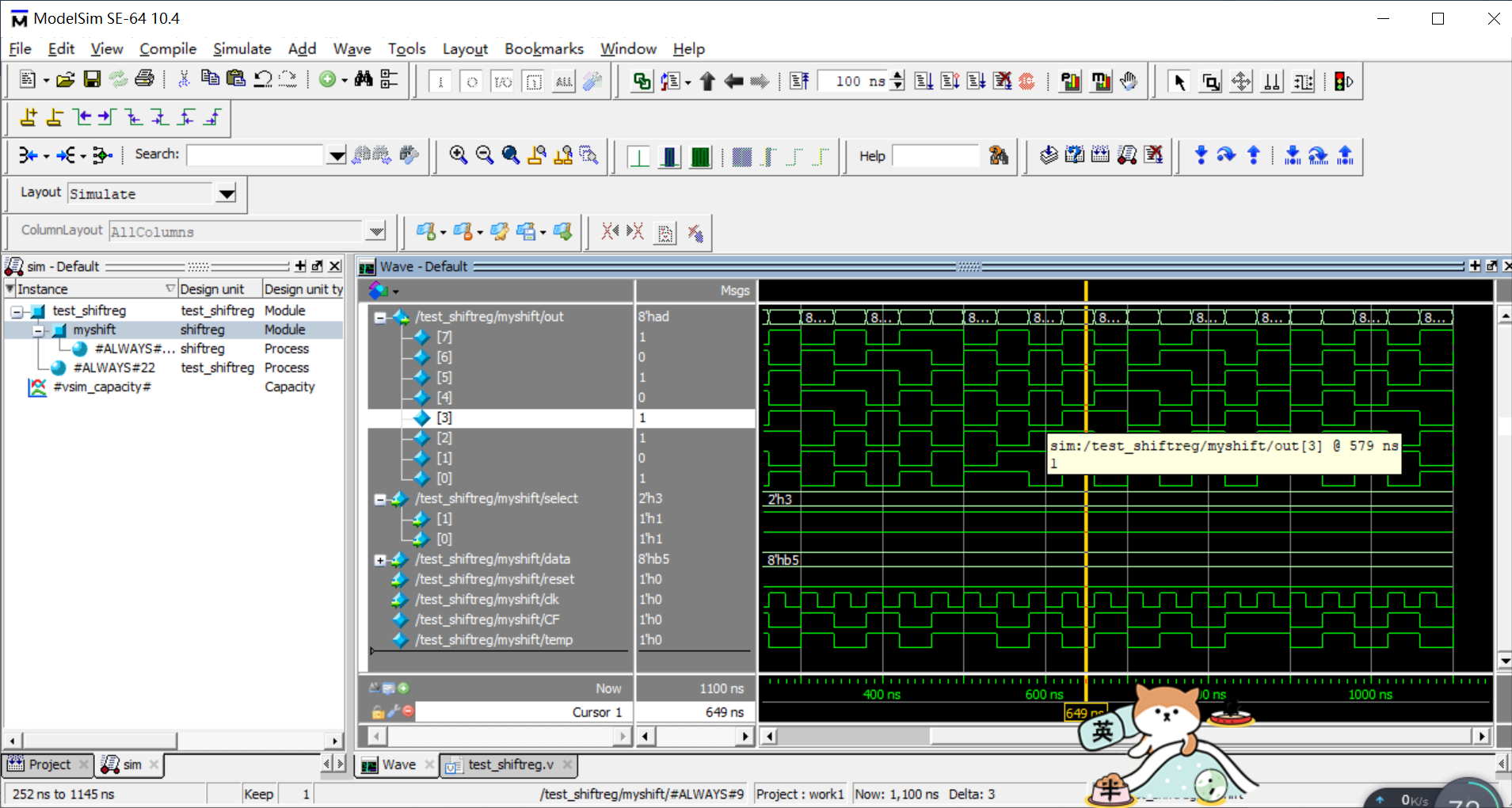

三、仿真截图

3.1、自循环左移

3.2、带进位位的循环左移

3.2、自循环右移

3.3、带进位位的循环右移

3.4、带进位位的循环右移

最后

以上就是忐忑月饼最近收集整理的关于Verilog数字系统设计——移位寄存器实现verilog——移位寄存器实现的全部内容,更多相关Verilog数字系统设计——移位寄存器实现verilog——移位寄存器实现内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[转]EP3C16Q240C8N 引脚说明](https://www.shuijiaxian.com/files_image/reation/bcimg20.png)

发表评论 取消回复