HDLBits网址:https://hdlbits.01xz.net/wiki/Main_Page

题目

From a 1000 Hz clock, derive a 1 Hz signal, called OneHertz, that could be used for the digital wall clock. Build the frequency divider using modulo-10 (BCD) counters and as few other gates as possible. Also output the enable signals from each of the BCD counters you use (c_enable[0] for the fastest counter, c_enable[2] for the slowest).

The following BCD counter is provided for you. Enable must be high for the counter to run. Reset is synchronous and set high to force the counter to zero. All counters in your circuit must directly use the same 1000 Hz signal.

我的设计

通过例化一个10进制bcd码计数器,来实现1000分频的分频器,即把一个1KHz的时钟通过分频的手段,变成一个1Hz的信号,那就计数到999给一个输出作为1Hz信号输出。

那怎么样计数到999?这个时候就要利用题目提供的BCD计数器,例化成为个位计数器、十位计数器、百位计数器。个位计数器计数到9,进位到十位计数器,十位计数器计数到9,进位到百位计数器,直到计数到999为止。综上所述,设计如下:

法一(输出为时序逻辑)

由于时序逻辑是上升沿触发,所以总是会慢一拍。为了使c_enable的翻转与个位计数器计数到9同步,所以要提前一拍,所以code的15行和17行的个位计数器计数是判断是否等于8。

module top_module (input clk,input reset,output reg OneHertz,output reg [2:0] c_enable); //wire [3:0] Q1,Q2,Q3;always@(posedge clk)beginif(reset) beginc_enable <= 1;OneHertz <= 0;endelse beginif(Q1 == 4'd8)beginc_enable <= 3'd3;if(Q2==4'd9 && Q1==4'd8 )beginc_enable <= 3'd7;if(Q3 == 4'd9)OneHertz <= 1;endendelse beginc_enable <= 1;OneHertz <= 0;endendendbcdcount counter0 (clk, reset, c_enable[0],Q1);bcdcount counter1 (clk, reset, c_enable[1],Q2);bcdcount counter2 (clk, reset, c_enable[2],Q3);endmodule

法二(输出为组合逻辑)

既然要慢一拍处理,那为什么不直接组合逻辑输出?这样就可以实现同步的效果了,而且更加简单易懂,设计如下:

module top_module (input clk,input reset,output OneHertz,output [2:0] c_enable); //wire [3:0] q0, q1, q2;assign c_enable = {q1 == 4'd9 && q0 == 4'd9, q0 == 4'd9, 1'b1};assign OneHertz = {q2 == 4'd9 && q1 == 4'd9 && q0 == 4'd9};bcdcount counter0 (clk, reset, c_enable[0], q0);bcdcount counter1 (clk, reset, c_enable[1], q1);bcdcount counter2 (clk, reset, c_enable[2], q2);endmodule

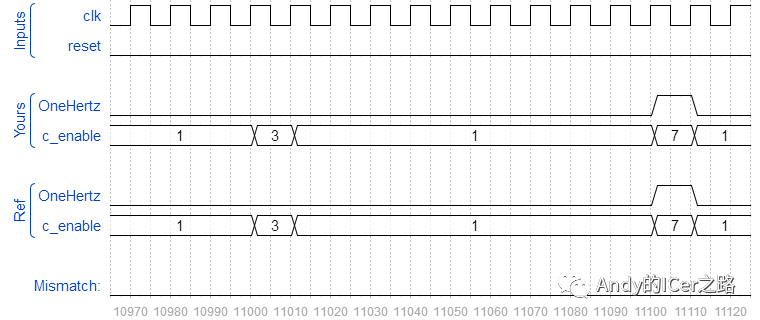

仿真波形

微信公众号

建立了一个微信公众号“Andy的ICer之路”,此公众号主要分享数字IC相关的学习经验,做公众号的目的就是记录自己的学习过程,很多东西回过头来可能就忘记了,为了记住知识和分享知识,希望自己可以保持更新,有兴趣的朋友可以关注一下!

最后

以上就是兴奋电话最近收集整理的关于Verilog专题(十三)计数器的级联实现1000分频的分频器题目我的设计微信公众号的全部内容,更多相关Verilog专题(十三)计数器内容请搜索靠谱客的其他文章。

发表评论 取消回复