目录

前言

3.2.5.5 Simple state transitions 3(Fsm3comb)

Solution:

3.2.5.6 Simple one-hot state transitions 3(Fsm3onehot)

Solution:

3.2.5.7 Simple FSM 3(asynchoronous reset) (Fsm3)

Solution:

3.2.5.8 Simple FSM 3(synchoronous reset) (Fsm3s)

Solution:

3.2.5.9 Design a Moore FSM(Exams/ece241 2013 q4)

Solution:

前言

HDLbits网站如下

Problem sets - HDLBits (01xz.net)

失踪人口回归,这个寒假想把hdlbits刷完!话不多说开冲~

从本期开始我们继续HDLbits第三章Circuits的学习,本期的内容是Finite State Machines有限状态机的第二小节(3.2.5.5-3.2.5.9)

3.2.5.5 Simple state transitions 3(Fsm3comb)

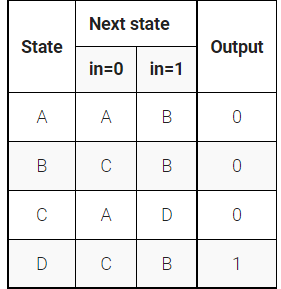

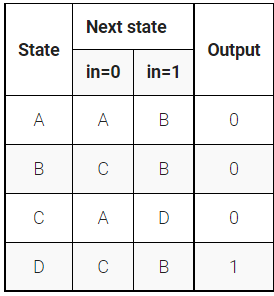

下面是一输入一输出四状态的摩尔状态机的状态转移表。使用以下状态编码:A=2'b00, B=2'b01, C=2'b10, D=2'b11.

仅实现此状态机的状态转换逻辑和输出逻辑(组合逻辑部分)。给定当前状态(state),根据状态转移表计算 next_state 和 输出(out)。

Solution:

module top_module(

input in,

input [1:0] state,

output [1:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: next_state = f(state, in)

always@(*) begin

case(state)

A:next_state=in?B:A;

B:next_state=in?B:C;

C:next_state=in?D:A;

D:next_state=in?B:C;

endcase

end

// Output logic: out = f(state) for a Moore state machine

assign out = (state == D);

endmodule

3.2.5.6 Simple one-hot state transitions 3(Fsm3onehot)

下面是一输入一输出四状态的摩尔状态机的状态转移表。使用以下独热码进行编码:A=4'b0001, B=4'b0010, C=4'b0100, D=4'b1000。

假设 one-hot 编码,通过检查导出状态转换和输出逻辑方程。仅实现此状态机的状态转换逻辑和输出逻辑(组合逻辑部分)。 (testbench将使用非独热码输入进行测试,以确保您不会尝试做更复杂的事情)。

“derive equations by inspection”什么意思呢?

One-hot 状态机编码保证恰好一个状态位为 1。这意味着可以通过仅检查一个状态位而不是所有状态位来确定状态机是否处于特定状态。通过检查状态转换图中每个状态的输入边,这会导致状态转换的简单逻辑方程。

比如上面的状态机中,状态机怎么才能到达状态A呢?它必须使用两个传入要求之一:“当前处于状态 A 并且 in=0”或“当前处于状态 C 并且 in = 0”。由于 one-hot 编码,测试“当前处于状态 A”的逻辑方程只是状态 A 的状态位。这导致了状态位 A 的下一个状态的最终逻辑方程:next_state[0] = state[0]&(~in) | state[2]&(~in)。 one-hot 编码保证一次最多有一个子句(乘积项)是“活动的”,因此这些子句可以一起进行或运算。

当练习要求“通过检查”获得状态转移方程时,请使用这种特殊方法。测试平台将使用非独热输入进行测试,以确保您的逻辑方程遵循此方法,而不是针对状态位的非法(非独热)组合执行其他操作(例如复位 FSM)。

尽管 RTL 级设计不需要知道这个算法(逻辑综合器处理这个),但它说明了为什么 one-hot FSM 通常具有更简单的逻辑(以更多的状态位存储为代价),并且这个主题经常显示参加数字逻辑课程的考试。

Hint:独热状态转换逻辑的逻辑方程可以通过查看状态转换图的跳变沿来推导出。

Solution:

module top_module(

input in,

input [3:0] state,

output [3:0] next_state,

output out); //

parameter A=0, B=1, C=2, D=3;

// State transition logic: Derive an equation for each state flip-flop.

assign next_state[A] = state[A]&(~in)|state[C]&(~in);

assign next_state[B] = state[A]&(in)|state[B]&(in)|state[D]&(in);

assign next_state[C] = state[B]&(~in)|state[D]&(~in);

assign next_state[D] = state[C]&(in);

// Output logic:

assign out = (state[D]==1);

endmodule

3.2.5.7 Simple FSM 3(asynchoronous reset) (Fsm3)

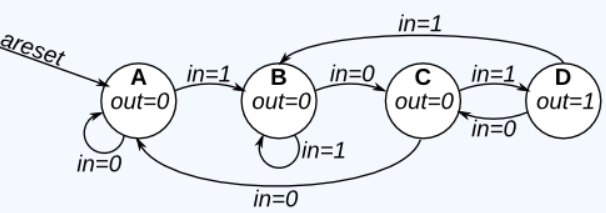

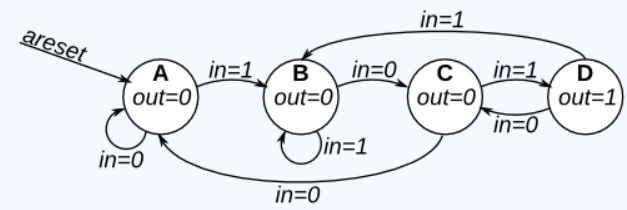

与3.2.5.5类似Fsm3comb - HDLBits

下面是一输入一输出四状态的摩尔状态机的状态转移表。实现这个状态机。包括将 FSM 异步复位为状态 A 。

Hint:

Solution:

module top_module(

input clk,

input in,

input areset,

output out); //

parameter A=0,B=1,C=2,D=3;

reg [1:0]state;

reg [1:0]next;

// State transition logic

always@(*) begin

case(state)

A:next=in?B:A;

B:next=in?B:C;

C:next=in?D:A;

D:next=in?B:C;

endcase

end

// State flip-flops with asynchronous reset

always@(posedge clk,posedge areset) begin

if(areset)

state<=A;

else

state<=next;

end

// Output logic

assign out = (state==D);

endmodule

3.2.5.8 Simple FSM 3(synchoronous reset) (Fsm3s)

与3.2.5.5类似Fsm3comb - HDLBits

下面是一输入一输出四状态的摩尔状态机的状态转移表。实现这个状态机。包括将 FSM 同步复位为状态 A 。

Hint:

Solution:

module top_module(

input clk,

input in,

input reset,

output out); //

parameter A=0,B=1,C=2,D=3;

reg[1:0]state;

reg[1:0]next;

// State transition logic

always@(*) begin

case(state)

A:next=in?B:A;

B:next=in?B:C;

C:next=in?D:A;

D:next=in?B:C;

endcase

end

// State flip-flops with synchronous reset

always@(posedge clk)

begin

if(reset)

state<=A;

else

state<=next;

end

// Output logic

assign out = (state == D);

endmodule

3.2.5.9 Design a Moore FSM(Exams/ece241 2013 q4)

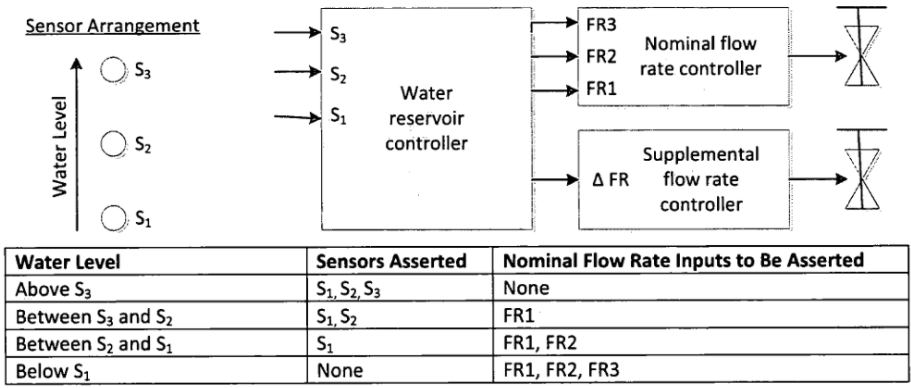

一个大水库供几个用户用水。为了保持水位足够高,三个传感器以5英寸的间隔垂直放置。当水位高于最高传感器(S3)时,输入流量为零。当水位低于最低传感器(S1)时,流量应在最大(标称流量FR和补充流量dFR都打开)。当水位在上下传感器之间时,流量由两个因素决定:水位和上一个传感器变化前的水位。每个水位都有一个与之相关的标称流量(FR),如下表所示。如果传感器的变化表明先前的水位低于当前的水位,则标称流量应该放在适当的位置。如果先前的水位高于当前的水位,应通过打开补充流量阀(由dFR控制)来增加流量。画出水库控制器的摩尔状态机的转换图。清楚地指出每个状态的所有状态转换和输出。FSM的输入为S1、S2、S3;输出是FR1、FR2、 FR3和dFR。

还包括一个高电平有效同步复位,它将状态机复位到相当于below S1状态

Solution:

module top_module (

input clk,

input reset,

input [3:1] s,

output fr3,

output fr2,

output fr1,

output dfr

);

parameter ML=0,L=1,H=2,MH=3;//最低、低、高、最高

reg [1:0]state;

reg [1:0]next;

//1

always@(*) begin

case(state)

ML:begin

if(s[1])

next=L;

else

next=ML;

end

L:begin

if(s[2])

next=H;

else if(!s[1])

next=ML;

else

next=L;

end

H:begin

if(s[3])

next=MH;

else if(!s[2])

next=L;

else

next=H;

end

MH:begin

if(!s[3])

next=H;

else

next=MH;

end

endcase

end

//2

always@(posedge clk) begin

if(reset)

state<=ML;

else

state<=next;

end

reg lower;

always@(posedge clk) begin

if(reset||state<next)

lower<=1'b0;

else if(state>next)

lower<=1'b1;

end

//3

assign fr3=(state<=ML)?1'b1:1'b0;

assign fr2=(state<=L)?1'b1:1'b0;

assign fr1=(state<=H)?1'b1:1'b0;

assign dfr=(state==ML)||lower;

endmodule

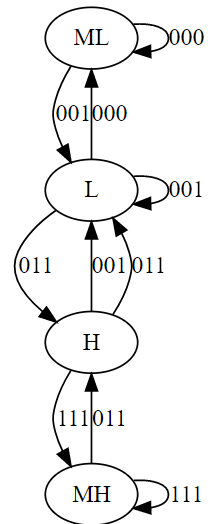

现在回头想水库问题,其实也不是很难。一共有3个传感器S1、S2、S3,对应4个状态(即表中4个状态,我用ML、L、H、MH来表示)。

- 首先是状态转变逻辑,状态机大概是下图,写到这,发现还有更简单的方法,即把s当成条件(将第一步改成下面这样)

//简化第一步

always@(*) begin

case(s)

3'b000:next=ML;

3'b001:next=L;

3'b011:next=H;

3'b111:next=MH;

default:next=ML;

endcase

end- 第二步是当前状态寄存器,先前水位高于当前水位的话要打开dFR,故通过lower来判断是否打开dFR

- 第三步是输出

状态机这里写得很乱QAQ

最后

以上就是细心帽子最近收集整理的关于Verilog HDLBits 第十六期:3.2.6 Finite State Machines(3.2.5.5-3.2.5.9)前言3.2.5.5 Simple state transitions 3(Fsm3comb) 3.2.5.6 Simple one-hot state transitions 3(Fsm3onehot) 3.2.5.7 Simple FSM 3(asynchoronous reset) (Fsm3)3.2.5.8 Simple FSM 3(synchoronous r的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复