先做一句话总结,if语句和组合逻辑下的case语句,他们的条件是有优先级的,从上到下优先级递减,每多一个条件就会多消耗一个二选一多路器,很浪费资源;

优先级:if else 结构if的优先级最高;多if 结构最后一个if优先级最高如:

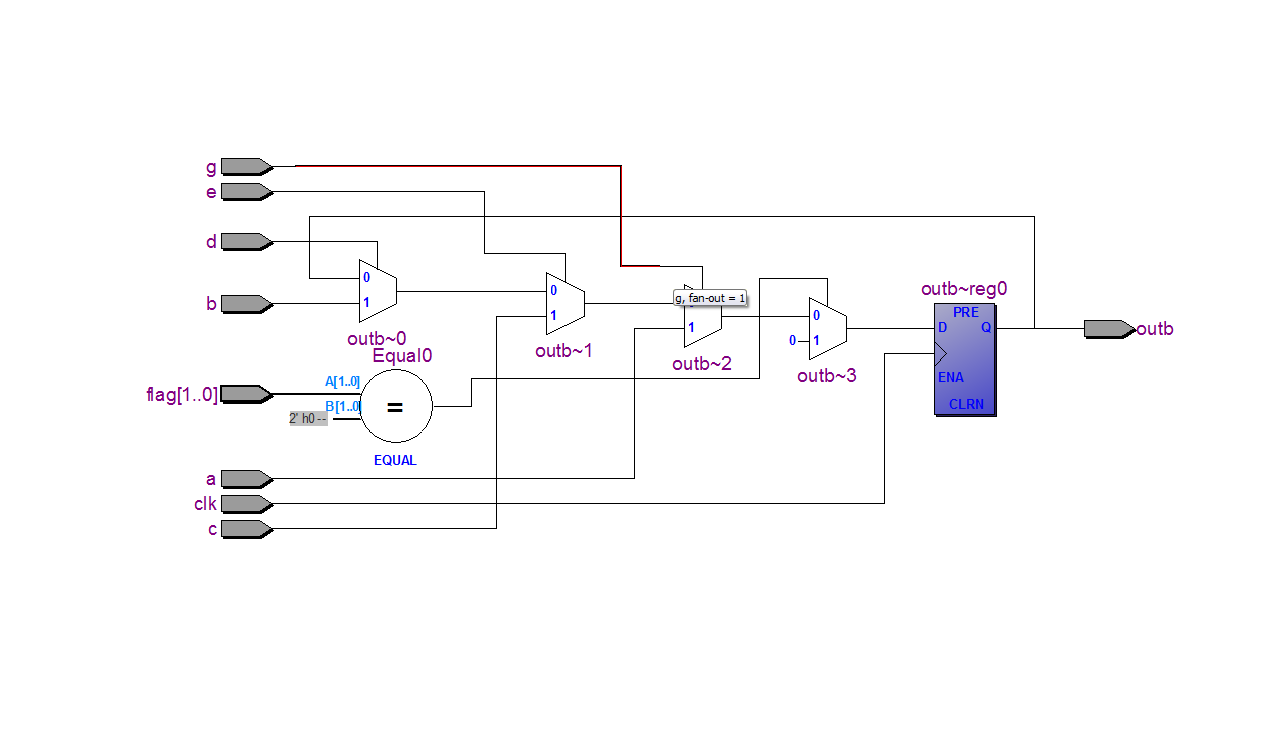

always@(posedge clk)

if(flag==2'b00)

begin

outb=0;

end

else

begin

if(d==1)

begin

outb=b;

end

if(e==1)

begin

outb=c;

end

if(g)

begin

outb=a;

end

end

而对于时序语句中的case,会被综合成n选一多路器,条件没有优先级,占用的资源更少。

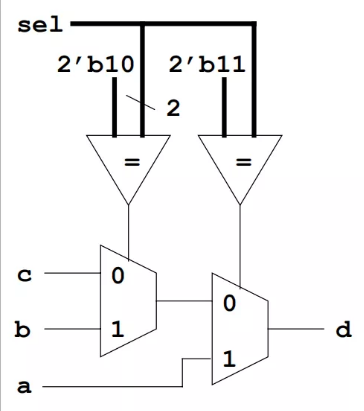

always_comb

if(sel=2'b11)

d=a;

else if(sel=2'b10)

d=b;

else

d=c;

endcase

always_comb

case(sel)

2'b11:d=a;

2'b10:d=b;

default:d=c;

endcase 上面的组合逻辑代码综合的电路如下图:

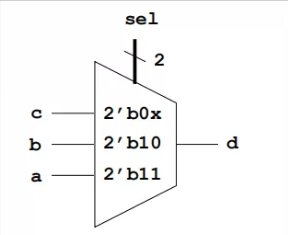

always_ff

case(sel)

2'b11:d=a;

2'b10:d=b;

default:d=c;

endcase上面的代码综合的电路如下:

很明显时序case占用的逻辑资源更少。

最后

以上就是雪白鞋垫最近收集整理的关于verilog 中if语句和case语句综合成的电路的全部内容,更多相关verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[Verilog]Verilog中的位拼接运算符{ } Verilog中的位拼接运算符{ }](https://www.shuijiaxian.com/files_image/reation/bcimg10.png)

发表评论 取消回复