FPGA–D触发器记录

D 触发器根据复位的不同分为两种,一种是同步复位的 D 触发器,另一种时异步复位的 D 触发器。“同步”是和工作时钟同步的意思。

这里模拟的是边沿触发器,上升沿触发。

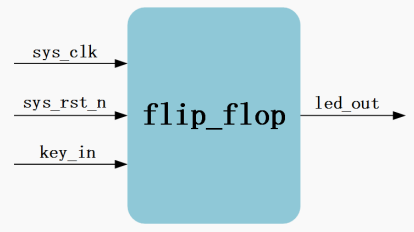

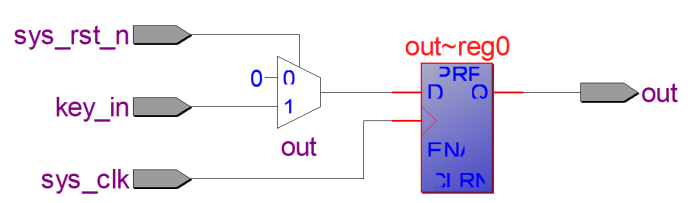

模块框图:

1. 异步复位

只要有检测到按键被按下,就立刻执行复位操作。

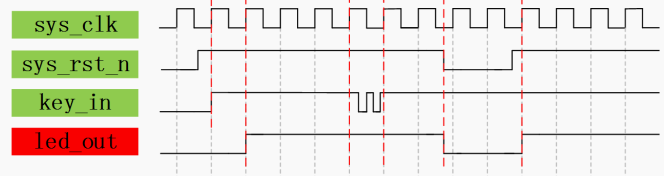

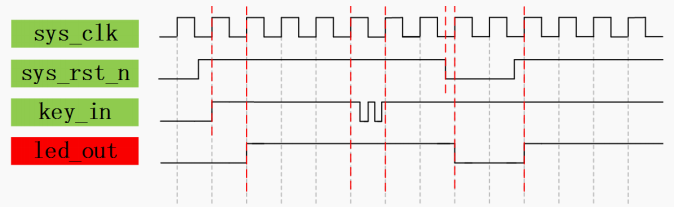

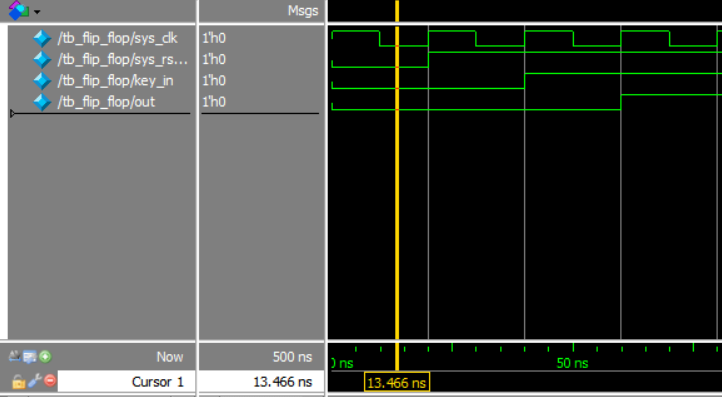

- 波形图

这是时序电路,有“延一拍”的效果,不管同步还是异步都如此。

如上图左边两条红线所示,第一次key_in变化时,led_out并没有立刻跳变,而是在下一个上升沿才变。此刻输出是与这次上升沿左边值为准。

3. 代码

module flip_flop

(

input wire sys_clk,

input wire sys_rst_n,

input wire key_in,

output reg out

);

always@(posedge sys_clk or negedge sys_rst_n) //当always块中的敏感列表为检测到

//sys_clk上升沿或复位信号下降沿时执行下面的语句

if (sys_rst_n == 1'b0)

out <= 1'b0;

else

out <= key_in;

endmodule

学习边沿检测的写法,posedge 和 negedge 分别表示上升沿和下降沿来到,positive和negative 。

-

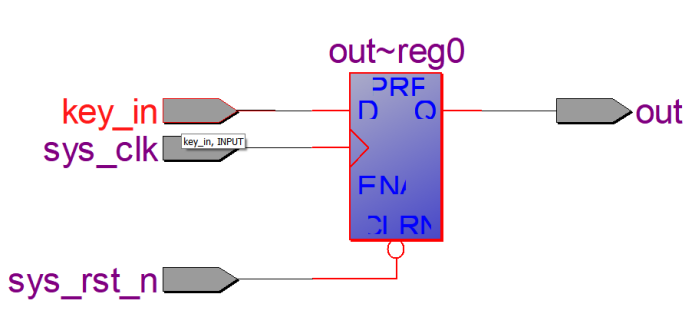

RTL视图

-

仿真代码

`timescale 1ns/1ns

module tb_flip_flop();

reg sys_clk, sys_rst_n, key_in;

wire out;

initial

begin

sys_clk = 1'b1; //时钟信号的初始化为 1,且使用“=”赋值,

//其他信号的赋值都是用“<=”,有了时钟信号后面的信号才有用

sys_rst_n <= 1'b0;

key_in <= 1'b0;

#20

sys_rst_n <= 1'b1;

#210 //210的原因是要在时钟上升沿的其他时刻跳变,这样容易观察

//同步与异步的区别,可以是其他类似时刻

sys_rst_n <= 1'b0; //有一次复位信号下降沿的产生

#40

sys_rst_n <= 1'b1;

end

always #10 sys_clk = ~sys_clk; //利用取反,获得时钟信号,周期为 20ns,频率为 50MHz

always #20 key_in <= {$random} % 2;//之所以每 20ns 产生一次随机

//数是为了在时序逻辑中能够保证 key_in 信号的变化的

//时间与时钟的周期相同,这样就不会产生类

//似毛刺的变化信号,虽然产生的毛刺在时序电

//路中也能被滤除掉,但是不便于我们观察波形

//尽量是10的倍数,比较好观察

flip_flop flip_flop_inst

(

.sys_clk(sys_clk),

.sys_rst_n(sys_rst_n),

.key_in(key_in),

.out(out)

);

endmodule

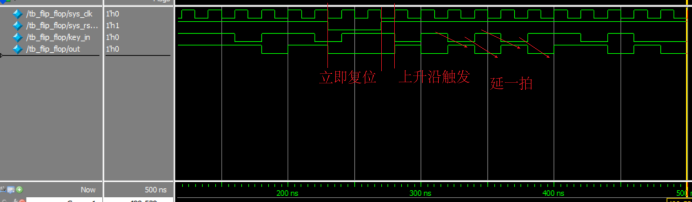

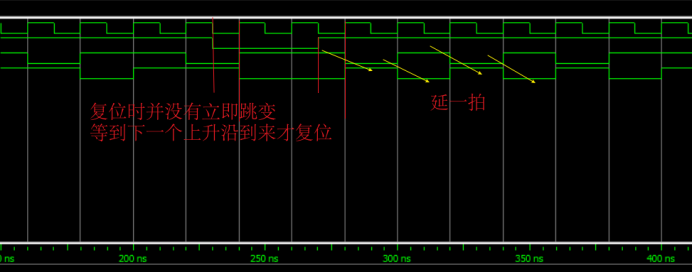

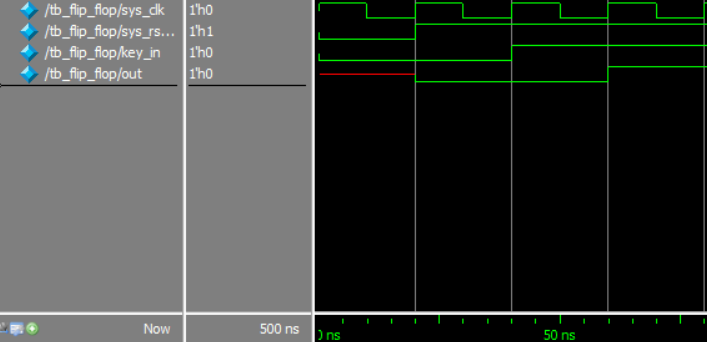

- 仿真结果

当时钟和信号在同一时刻变化时,我们以时钟的上升沿前一时刻采集的输入信号为依据来产生输出信号,这样看到的效果与设计波形图时一致。

2. 同步复位

-

波形图

当时钟的上升沿(也可以是下降沿,一般习惯上为上升沿触发)来到时检测到按键的复位操作才有效,否则无效。

依然延一拍。 -

代码

module flip_flop

(

input wire sys_clk,

input wire sys_rst_n,

input wire key_in,

output reg out

);

always@(posedge sys_clk) //当always块中的敏感列表为检测到sys_clk上升沿时执行下面的语句

if (sys_rst_n == 1'b0)

out <= 1'b0;

else

out <= key_in;

endmodule

-

RTL视图

-

仿真代码,与异步相同

-

仿真结果

两者初始波形分析:

同步的:

异步的

- 我们可以看到第一个20ns内,out输出不同,同步的是1,而异步的是0,其实同步的不是1,看着是1,它应该是x,因为不能确定,一开始复位信号有效,但得等到下一个上升沿才会变化。所以初值不确定。

而异步信号是初值是0是因为一开始复位有效,即立刻有效,则out输出为0.- 20ns-40ns输出一样,输出out都是0是因为第一个时钟上升沿时的前一点点时刻复位信号有效,所以输出就是0。

总结:

- always 块实现时序逻辑时无论是单比特信号还是多比特信号都具有这种延一拍的效果。

- <=(赋值号的一种,非阻塞赋值,在可综合的模块中表达时序逻辑的语句时使用)

- 注意时钟信号边沿触发逻辑的编写,posedge和negedge.

最后

以上就是悦耳钥匙最近收集整理的关于D触发器记录的全部内容,更多相关D触发器记录内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复